ZHCSWA1E August 2003 – August 2024 SN74LVC74A-Q1

PRODUCTION DATA

封装选项

请参考 PDF 数据表获取器件具体的封装图。

机械数据 (封装 | 引脚)

- D|14

- PW|14

- BQA|14

散热焊盘机械数据 (封装 | 引脚)

- BQA|14

订购信息

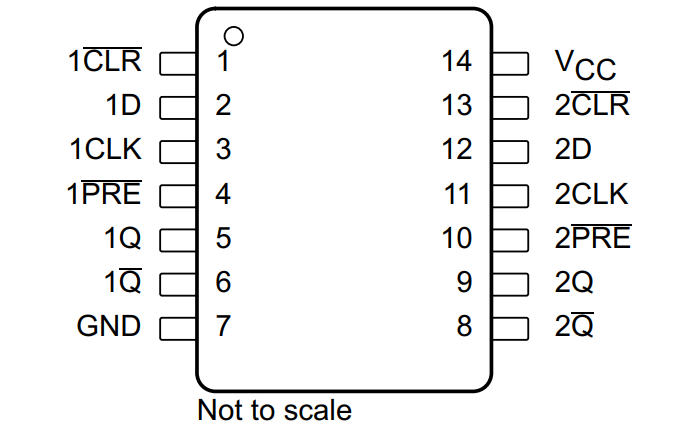

3 引脚配置和功能

图 3-1 D 或 PW 封装,14 引脚 SOIC 或 TSSOP(顶视图)

图 3-1 D 或 PW 封装,14 引脚 SOIC 或 TSSOP(顶视图) 图 3-2 BQA 封装14 引脚 WQFN(带有外露散热焊盘)(顶视图)

图 3-2 BQA 封装14 引脚 WQFN(带有外露散热焊盘)(顶视图)表 3-1 引脚功能

| 引脚 | I/O(1) | 说明 | |

|---|---|---|---|

| 名称 | SOIC、TSSOP、VQFN | ||

| 1CLK | 3 | I | 通道 1 时钟输入 |

| 1 CLR | 1 | I | 通道 1 清零输入。拉低可将 Q 输出设置为低电平。 |

| 1D | 2 | I | 通道 1 数据输入 |

| 1 PRE | 4 | I | 通道 1 预设输入。拉低可将 Q 输出设置为高电平。 |

| 1Q | 5 | O | 通道 1 输出 |

| 1 Q | 6 | O | 通道 1 反相输出 |

| 2CLK | 11 | I | 通道 2 时钟输入 |

| 2 CLR | 13 | I | 通道 2 清零输入。拉低可将 Q 输出设置为低电平。 |

| 2D | 12 | I | 通道 2 数据输入 |

| 2 PRE | 10 | I | 通道 2 预设输入。拉低可将 Q 输出设置为高电平。 |

| 2Q | 9 | O | 通道 2 输出 |

| 2 Q | 8 | O | 通道 2 反相输出 |

| GND | 7 | — | 接地 |

| NC | — | — | 无连接 |

| VCC | 14 | — | 电源 |

| 散热焊盘 | — | 将 GND 引脚连接到裸露的散热焊盘以确保正确操作。使用多个过孔将散热焊盘连接到任何内部 PCB 接地平面,以获得良好的热性能。 | |

(1) I = 输入、O = 输出、P = 电源、FB = 反馈、GND = 接地、N/A = 不适用