ZHCSEH3B December 2015 – September 2018 TAS5411-Q1

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3 Feature Description

- 9.4 Device Functional Modes

- 9.5 Register Maps

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13器件和文档支持

- 14机械、封装和可订购信息

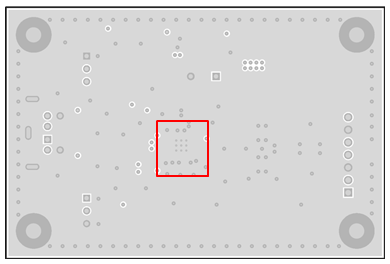

12.2.4 Bottom Layer – Ground Layer

The device has an exposed thermal pad on the bottom side for improved thermal performance. Conducting heat from the thermal pad to other layers requires thermal vias. Because the bottom layer is the secondary heat exchange surface to ambient, the thermal vias area must have low thermal resistance, that is, no signal vias or traces that can increase thermal resistance from the thermal vias to the bottom copper.

Figure 21. Bottom Layer

Figure 21. Bottom Layer