ZHCSBC3F July 2013 – February 2020 TAS5760M

PRODUCTION DATA.

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 Pin Configuration and Functions

-

6 Specifications

- 6.1 Absolute Maximum Ratings

- 6.2 ESD Ratings

- 6.3 Recommended Operating Conditions

- 6.4 Digital I/O Pins

- 6.5 Master Clock

- 6.6 Serial Audio Port

- 6.7 Protection Circuitry

- 6.8 Speaker Amplifier in All Modes

- 6.9 Speaker Amplifier in Stereo Bridge Tied Load (BTL) Mode

- 6.10 Speaker Amplifier in Mono Parallel Bridge Tied Load (PBTL) Mode

- 6.11 I²C Control Port

- 6.12 Typical Idle, Mute, Shutdown, Operational Power Consumption

- 6.13 Typical Characteristics (Stereo BTL Mode): fSPK_AMP = 384 kHz

- 6.14 Typical Characteristics (Stereo BTL Mode): fSPK_AMP = 768 kHz

- 6.15 Typical Characteristics (Mono PBTL Mode): fSPK_AMP = 384 kHz

- 6.16 Typical Characteristics (Mono PBTL Mode): fSPK_AMP = 768 kHz

- 7 Parameter Measurement Information

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3 Feature Description

- 8.4

Device Functional Modes

- 8.4.1

Hardware Control Mode

- 8.4.1.1 Speaker Amplifier Shut Down (SPK_SD Pin)

- 8.4.1.2 Serial Audio Port in Hardware Control Mode

- 8.4.1.3 Soft Clipper Control (SFT_CLIP Pin)

- 8.4.1.4 Speaker Amplifier Switching Frequency Select (FREQ/SDA Pin)

- 8.4.1.5 Parallel Bridge Tied Load Mode Select (PBTL/SCL Pin)

- 8.4.1.6 Speaker Amplifier Sleep Enable (SPK_SLEEP/ADR Pin)

- 8.4.1.7 Speaker Amplifier Gain Select (SPK_GAIN [1:0] Pins)

- 8.4.1.8 Considerations for Setting the Speaker Amplifier Gain Structure

- 8.4.2 Software Control Mode

- 8.4.1

Hardware Control Mode

- 8.5

Register Maps

- 8.5.1 Control Port Registers - Quick Reference

- 8.5.2

Control Port Registers - Detailed Description

- 8.5.2.1 Device Identification Register (0x00)

- 8.5.2.2 Power Control Register (0x01)

- 8.5.2.3 Digital Control Register (0x02)

- 8.5.2.4 Volume Control Configuration Register (0x03)

- 8.5.2.5 Left Channel Volume Control Register (0x04)

- 8.5.2.6 Right Channel Volume Control Register (0x05)

- 8.5.2.7 Analog Control Register (0x06)

- 8.5.2.8 Reserved Register (0x07)

- 8.5.2.9 Fault Configuration and Error Status Register (0x08)

- 8.5.2.10 Reserved Controls (9 / 0x09) - (15 / 0x0F)

- 8.5.2.11 Digital Clipper Control 2 Register (0x10)

- 8.5.2.12 Digital Clipper Control 1 Register (0x11)

-

9 Application and Implementation

- 9.1 Application Information

- 9.2

Typical Applications

- 9.2.1 Stereo BTL Using Software Control

- 9.2.2 Stereo BTL Using Software Control, 32-Pin DAP Package Option

- 9.2.3 Stereo BTL Using Hardware Control, 32-Pin DAP Package Option

- 9.2.4 Mono PBTL Using Software Control, 32-Pin DAP Package Option

- 9.2.5 Mono PBTL Using Hardware Control, 32-Pin DAP Package Option

- 10Power Supply Recommendations

- 11Layout

- 12器件和文档支持

- 13机械、封装和可订购信息

封装选项

机械数据 (封装 | 引脚)

散热焊盘机械数据 (封装 | 引脚)

订购信息

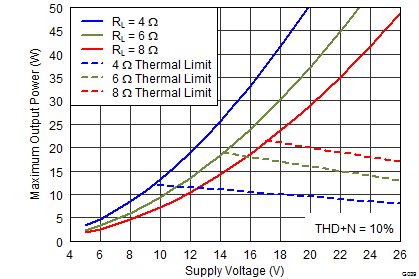

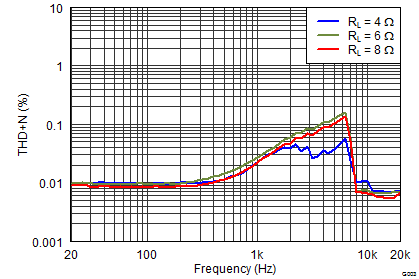

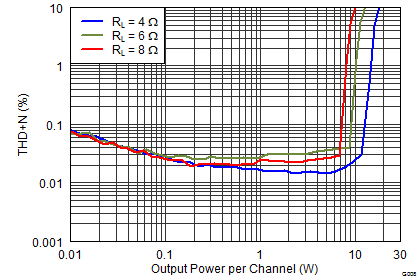

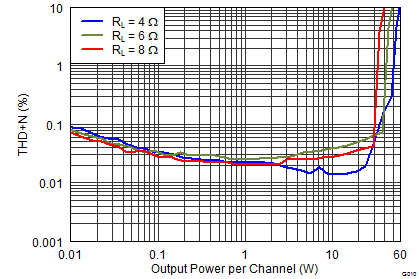

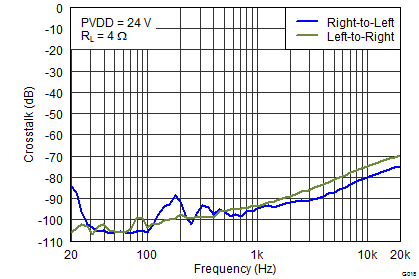

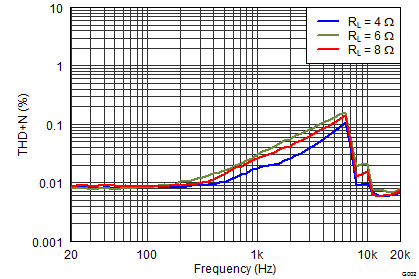

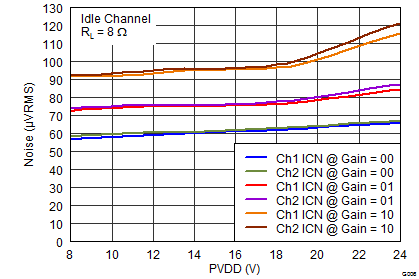

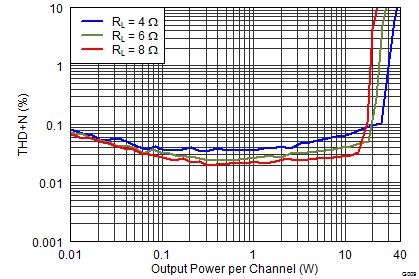

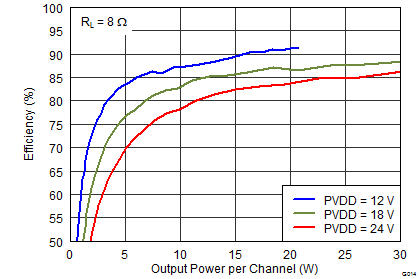

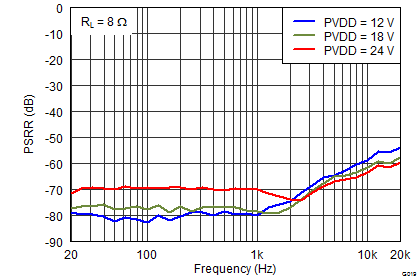

6.14 Typical Characteristics (Stereo BTL Mode): fSPK_AMP = 768 kHz

At TA = 25°C, fSPK_AMP = 768 kHz, input signal is 1 kHz Sine, unless otherwise noted. Filter used for 8 Ω = 22 µH + 0.68 µF, Filter used for 6 Ω = 15 µH + 0.68 µF, Filter used for 4 Ω = 10 µH + 0.68 µF unless otherwise noted.

Thermal Limits are referenced to TAS5760xxEVM Rev D

Figure 15. Output Power vs PVDD

PVDD = 24 V, POSPK = 1 W

Figure 17. THD+N vs Frequency

PVDD = 12 V, Both Channels Driven

Figure 19. THD+N vs Output Power

PVDD = 24 V, Both Channels Driven

Figure 21. THD+N vs Output Power  Figure 23. Crosstalk vs Frequency

Figure 23. Crosstalk vs Frequency  Figure 25. Idle Current Draw vs PVDD (Filterless)

Figure 25. Idle Current Draw vs PVDD (Filterless)  Figure 27. Shutdown Current Draw vs PVDD (Filterless)

Figure 27. Shutdown Current Draw vs PVDD (Filterless)

PVDD = 12 V, POSPK = 1 W

Figure 16. THD+N vs Frequency  Figure 18. Idle Channel Noise vs PVDD

Figure 18. Idle Channel Noise vs PVDD

PVDD = 18 V, Both Channels Driven

Figure 20. THD+N vs Output Power  Figure 22. Efficiency vs Output Power

Figure 22. Efficiency vs Output Power  Figure 24. PVDD PSRR vs Frequency

Figure 24. PVDD PSRR vs Frequency

With LC Filter as Shown on EVM

Figure 26. Idle Current Draw vs PVDD