ZHCSMV1 December 2020 TAS5822M

PRODUCTION DATA

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

-

7 Detailed Description

- 7.1 Overview

- 7.2 Functional Block Diagram

- 7.3 Feature Description

- 7.4 Device Functional Modes

- 7.5 Programming and Control

- 7.6 Register Maps

- 8 Application and Implementation

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

8.2.2.3 Application Performance Plots

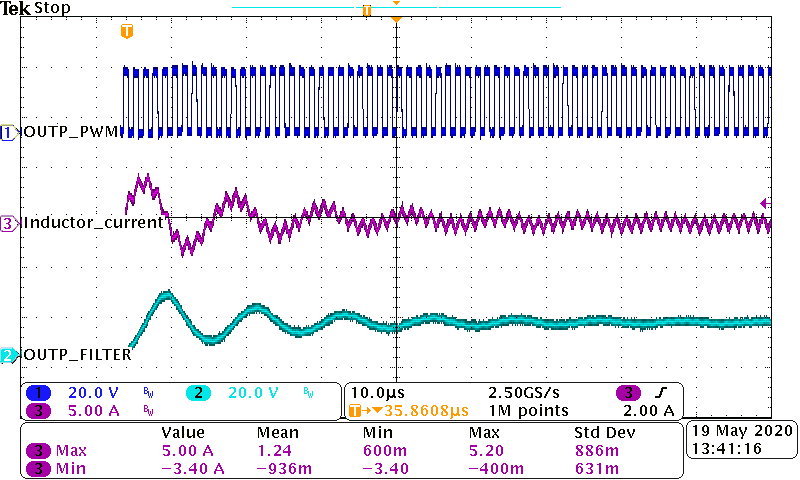

Figure 8-3 Start-up Current

Figure 8-3 Start-up Current (Fsw = 768 kHz, LC filter = 4.7 µH + 0.68 µF, PVDD = 24 V, BD Modulation)

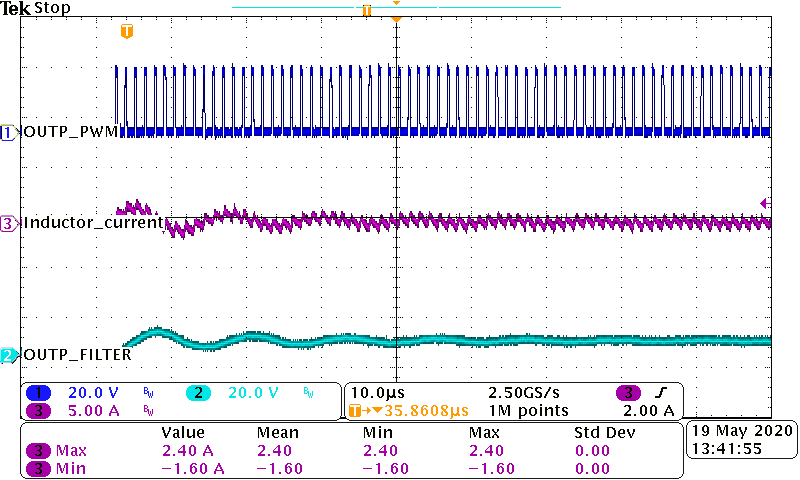

Figure 8-4 Start-up Current

Figure 8-4 Start-up Current (Fsw = 768 kHz, LC filter = 4.7 µH + 0.68 µF, PVDD = 24 V, 1SPW Modulation)