SLAS520E February 2007 – December 2014 TLV320AIC3101

PRODUCTION DATA.

- 1 Features

- 2 Applications

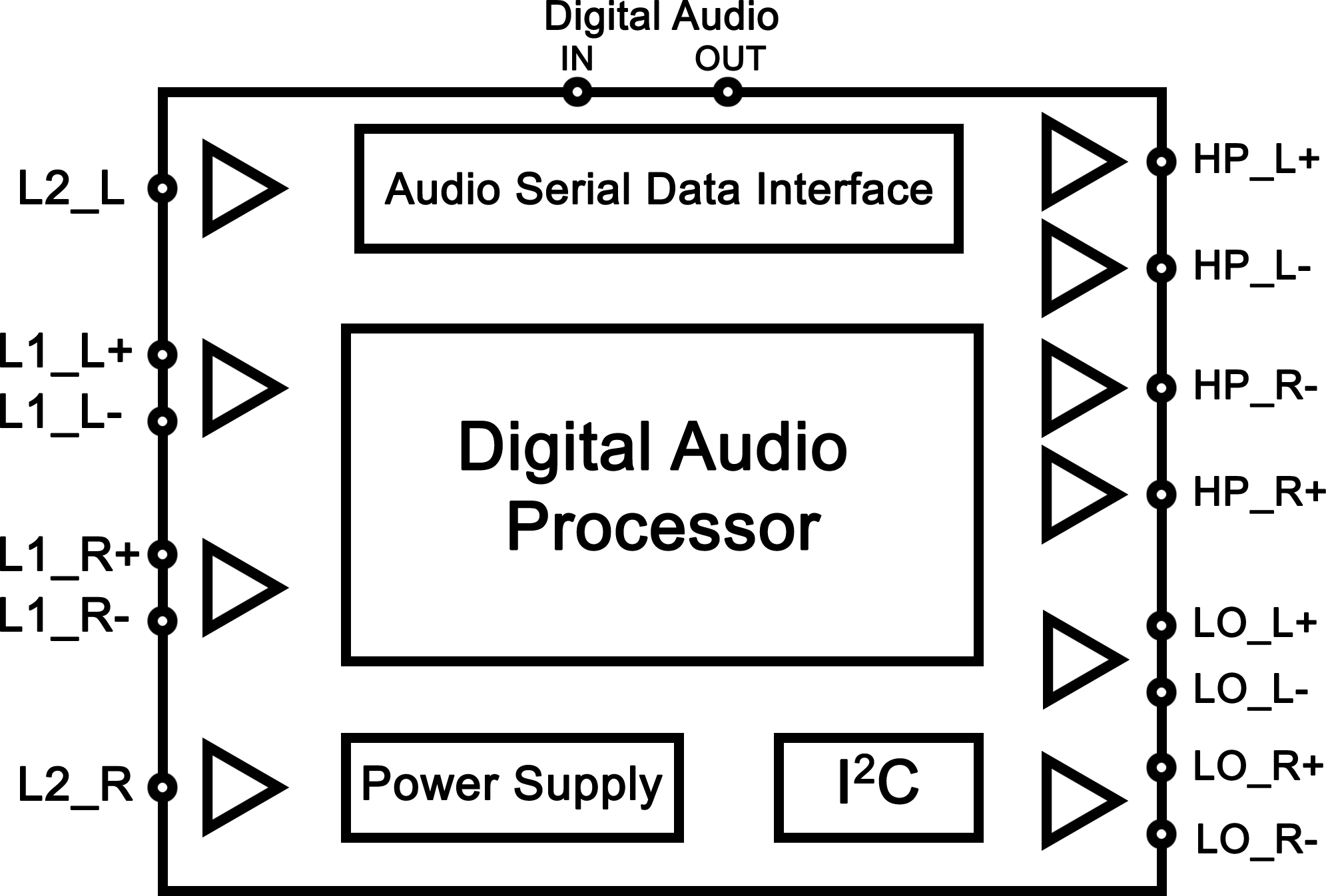

- 3 Description

- 4 Simplified Diagram

- 5 Revision History

- 6 Description (continued)

- 7 Device Comparison Table

- 8 Pin Configuration and Functions

- 9 Specifications

- 10Parameter Measurement Information

-

11Detailed Description

- 11.1 Overview

- 11.2 Functional Block Diagram

- 11.3

Feature Description

- 11.3.1 Hardware Reset

- 11.3.2 Digital Audio Data Serial Interface

- 11.3.3 Audio Data Converters

- 11.3.4 Audio Analog Inputs

- 11.3.5 Analog Fully Differential Line Output Drivers

- 11.3.6 Analog High-Power Output Drivers

- 11.3.7 Input Impedance and VCM Control

- 11.3.8 MICBIAS Generation

- 11.3.9 Short-Circuit Output Protection

- 11.3.10 Jack/Headset Detection

- 11.4 Device Functional Modes

- 11.5 Programming

- 11.6 Register Maps

- 11.7 Output Stage Volume Controls

- 12Application and Implementation

- 13Power Supply Recommendations

- 14Layout

- 15Device and Documentation Support

- 16Mechanical, Packaging, and Orderable Information

1 Features

- Stereo Audio DAC

- 102-dBA Signal-to-Noise Ratio

- 16/20/24/32-Bit Data

- Supports Sample Rates From 8 kHz to 96 kHz

- 3D/Bass/Treble/EQ/De-Emphasis Effects

- Flexible Power Saving Modes and Performance are Available

- Stereo Audio ADC

- 92-dBA Signal-to-Noise Ratio

- Supports Sample Rates From 8 kHz to 96 kHz

- Digital Signal Processing and Noise Filtering Available During Record

- Six Audio Input Pins

- One Stereo Pair of Single-Ended Inputs

- One Stereo Pair of Fully Differential Inputs

- Six Audio Output Drivers

- Stereo Fully Differential or Single-Ended Headphone Drivers

- Fully Differential Stereo Line Outputs

- Stereo 8-Ω, 500-mW/Channel Speaker Drive Capability

- Low Power: 14-mW Stereo 48-kHz Playback With 3.3-V Analog Supply

- Ultralow-Power Mode With Passive Analog Bypass

- Programmable Input/Output Analog Gains

- Automatic Gain Control (AGC) for Record

- Programmable Microphone Bias Level

- Programmable PLL for Flexible Clock Generation

- I2C Control Bus

- Audio Serial Data Bus Supports I2S, Left/Right-Justified, DSP, and TDM Modes

- Extensive Modular Power Control

- Power Supplies:

- Analog: 2.7 V–3.6 V.

- Digital Core: 1.525 V–1.95 V

- Digital I/O: 1.1 V–3.6 V

- Package: 5-mm × 5-mm 32-Pin QFN

2 Applications

- Digital Cameras

- Smart Cellular Phones

3 Description

The TLV320AIC3101 is a low-power stereo audio codec with stereo headphone amplifier, as well as multiple inputs and outputs that are programmable in single-ended or fully differential configurations. Extensive register-based power control is included, enabling stereo 48-kHz DAC playback as low as 14 mW from a 3.3-V analog supply, making it ideal for portable battery-powered audio and telephony applications.

The record path of the TLV320AIC3101 contains integrated microphone bias, digitally controlled stereo microphone preamplifier, and automatic gain control (AGC), with mix/mux capability among the multiple analog inputs. Programmable filters are available during record which can remove audible noise that can occur during optical zooming in digital cameras. The playback path includes mix/mux capability from the stereo DAC and selected inputs, through programmable volume controls, to the various outputs.

Device Information(1)

| PART NUMBER | PACKAGE | BODY SIZE (NOM) |

|---|---|---|

| TLV320AIC3101 | VQFN (32) | 5.00 mm x 5.00 mm |

- For all available packages, see the orderable addendum at the end of the datasheet.

4 Simplified Diagram