ZHCSJS3E may 2019 – june 2023 TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S

PRODUCTION DATA

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 修订历史记录

- 5 器件比较

- 6 终端配置和功能

-

7 规格

- 7.1 绝对最大额定值

- 7.2 ESD 等级 - 商用

- 7.3 ESD 等级 - 汽车

- 7.4 建议运行条件

- 7.5 功耗摘要

- 7.6 电气特性

- 7.7 ZWT 封装的热阻特性

- 7.8 PTP 封装的热阻特性

- 7.9 散热设计注意事项

- 7.10

系统

- 7.10.1 电源管理模块 (PMM)

- 7.10.2 复位时序

- 7.10.3 时钟规格

- 7.10.4 闪存参数

- 7.10.5 RAM 规格

- 7.10.6 ROM 规格

- 7.10.7 仿真/JTAG

- 7.10.8 GPIO 电气数据和时序

- 7.10.9 中断

- 7.10.10 低功率模式

- 7.10.11 外部存储器接口 (EMIF)

- 7.11

C28x 模拟外设

- 7.11.1 模拟子系统

- 7.11.2

模数转换器 (ADC)

- 7.11.2.1 结果寄存器映射

- 7.11.2.2 ADC 可配置性

- 7.11.2.3 ADC 电气数据和时序

- 7.11.2.4 温度传感器电气数据和时序

- 7.11.3 比较器子系统 (CMPSS)

- 7.11.4 缓冲数模转换器 (DAC)

- 7.12 C28x 控制外设

- 7.13

C28x 通信外设

- 7.13.1 控制器局域网 (CAN)

- 7.13.2 快速串行接口 (FSI)

- 7.13.3 内部集成电路 (I2C)

- 7.13.4 多通道缓冲串行端口 (McBSP)

- 7.13.5 电源管理总线 (PMBus)

- 7.13.6 串行通信接口 (SCI)

- 7.13.7 串行外设接口 (SPI)

- 7.13.8 EtherCAT 从站控制器 (ESC)

- 7.13.9 通用串行总线(USB)控制器

- 7.14 连接管理器 (CM) 外设

-

8 详细说明

- 8.1 概述

- 8.2 功能方框图

- 8.3 存储器

- 8.4 标识

- 8.5 总线架构 - 外设连接

- 8.6 引导 ROM 和外设引导

- 8.7 双代码安全模块 (DCSM)

- 8.8 C28x (CPU1/CPU2) 子系统

- 8.9 连接管理器 (CM) 子系统

- 8.10 功能安全

- 9 应用、实施和布局

- 10器件和文档支持

- 11机械、封装和可订购信息

封装选项

请参考 PDF 数据表获取器件具体的封装图。

机械数据 (封装 | 引脚)

- ZWT|337

- PTP|176

散热焊盘机械数据 (封装 | 引脚)

订购信息

8.8.11 可配置逻辑块 (CLB)

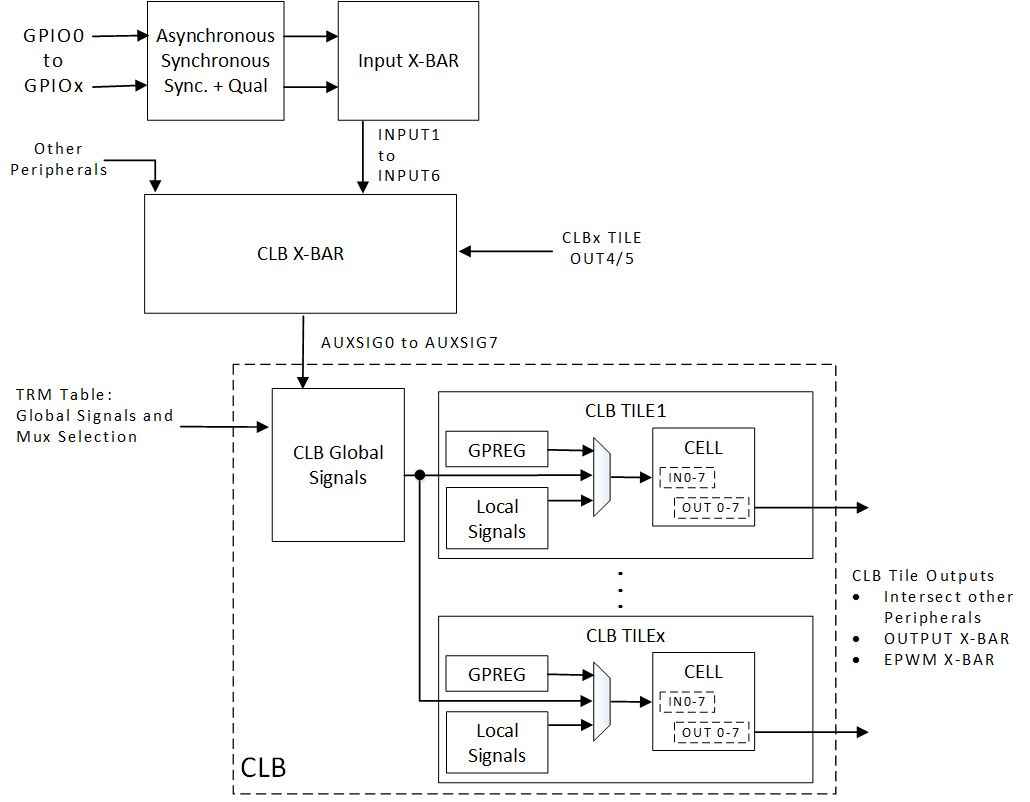

C2000 可配置逻辑块 (CLB) 是一组模块的集合,这些模块使用软件进行互连,以实现自定义数字逻辑功能或增强现有的片上外设。CLB 能够通过一组交叉开关互连来增强现有的外设,为现有的控制外设(例如增强型脉宽调制器 (ePWM)、增强型采集模块 (eCAP) 和增强型正交编码器脉冲模块 (eQEP))提供高度连接性。交叉开关还允许将 CLB 连接到外部 GPIO 引脚。通过这种方式,CLB 可以配置为与器件外设交互以执行小型逻辑功能(例如比较器),或实现自定义串行数据交换协议。通过 CLB,原本需要使用外部逻辑器件实现的功能现在可在 MCU 内实现。

在正常运行情况下,CLB 外设的时钟频率源自器件 SYSCLK,并且可在 100MHz 的最大频率下运行。如果需要更高的频率,则可以启用 CLB 流水线模式,从而使 CLB 时钟能够在高达 150MHz 的频率下运行。(此流水线模式需要将 SYSCLK 降低至 150MHz 的最大频率以支持该 CLB 操作)。HLC 被视为 CLB 的一个组成部分,并具有一组相同的频率规则。工作频率不随同步器或边缘认证而变化。没有为 CLB 输入和输出提供延迟。是否需要打开输入端的同步器或流水线滤波器路径,完全取决于器件级联接表,其中的输入标记为需要同步或不需要同步。

CLB 外设是通过 CLB 工具进行配置的。有关 CLB 工具、可用示例、应用报告和用户指南的更多信息,请参阅 C2000Ware 软件包(C2000Ware_2_00_00_03 及更高版本)中的以下位置:

C2000WARE_INSTALL_LOCATION\utilities\clb_tool\clb_syscfg\doc

- C2000WARE_INSTALL_LOCATION\utilities\clb_tool\clb_syscfg\doc

- CLB 工具用户指南

- “使用 C2000™ 可配置逻辑块 (CLB) 进行设计”应用报告

- “如何将自定义逻辑从 FPGA/CPLD 迁移到 C2000™ 微控制器”应用报告

CLB 模块及其互连如图 8-9 所示。

图 8-9 CLB 概述

图 8-9 CLB 概述绝对编码器协议接口现在作为 C2000Ware MotorControl SDK 中的 位置管理器 解决方案提供。C2000Ware MotorControl SDK 提供了此类解决方案的配置文件、应用程序接口 (API) 和使用示例。在某些解决方案中,TI 配置的 CLB 与其他片上资源(例如 SPI 端口或 C28x CPU)一起使用,以执行更复杂的功能。