ZHCSO95B june 2022 – may 2023 TPS1641

PRODUCTION DATA

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 Enable and Shutdown Input (EN/SHDN)

- 8.3.2 Overvoltage Protection (OVP)

- 8.3.3 Output Slew Rate and Inrush Current Control (dVdt)

- 8.3.4 Active Current Limiting (ILIM) With the TPS16412, TPS16413, TPS16416, and TPS16417

- 8.3.5 Active Power Limiting (PLIM) With the TPS16410, TPS16411, TPS16414, and TPS16415

- 8.3.6 Overcurrent Protection (IOCP) and Blanking Time (IDLY or PDLY) for Transient Loads

- 8.3.7 Fast-Trip and Short-Circuit Protection

- 8.3.8 Analog Load Current Monitor (IMON) on the IOCP Pin

- 8.3.9 IN to OUT Short Detection (TPS16410, TPS16411, TPS16412, and TPS16413)

- 8.3.10 Thermal Shutdown and Overtemperature Protection

- 8.3.11 Fault Response and Indication (FLT)

- 8.4 Device Functional Modes

- 9 Application and Implementation

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

8.3.2 Overvoltage Protection (OVP)

The TPS1641x implements overvoltage

protection to protect the load from input overvoltage conditions. A resistor divider

can be connected from the IN pin of device to configure the overvoltage protection

setpoint. The device turns off the internal FET and asserts the

FLT pin as the voltage at OVP pin goes above

VOVPR, and as the OVP pin voltage falls below VOVPF, the

internal FET is turned ON and FLT pin is de-asserted. See the

SLVSGF4-TPS1641-TPS1641x:具有输入至输出短路检测功能的 40V、1.8A 功率和电流限制型电子保险丝

TPS1641x 具有输入至输出短路检测功能的 40V、1.8A 功率和电流限制型电子保险丝

TPS1641x 具有输入至输出短路检测功能的 40V、1.8A 功率和电流限制型电子保险丝

特性

特性

应用

应用

说明

说明

Table of Contents

Table of Contents

Revision History

Revision History

Revision History

Revision History

Device Comparison Table

Device Comparison Table

Pin Configuration and Functions

Pin Configuration and Functions

Specifications

Specifications

Absolute Maximum Ratings

Absolute Maximum Ratings

ESD Ratings

ESD Ratings

Recommended Operating Conditions

Recommended Operating Conditions

Thermal Information

Thermal Information

Electrical Characteristics

Electrical Characteristics

Timing Requirements

Timing Requirements

Typical Characteristics

Typical Characteristics

Detailed Description

Detailed Description

Overview

Overview

Functional Block Diagram

Functional Block Diagram

Feature Description

Feature Description

Enable and Shutdown Input (EN/SHDN)

Enable and Shutdown Input (EN/SHDN)

Overvoltage Protection (OVP)

Overvoltage Protection (OVP)

Output Slew Rate and Inrush Current Control (dVdt)

Output Slew Rate and Inrush Current Control (dVdt)

Active Current Limiting (ILIM) With the TPS16412, TPS16413, TPS16416, and TPS16417

Active Current Limiting (ILIM) With the TPS16412, TPS16413, TPS16416, and TPS16417

Active Power Limiting (PLIM) With the TPS16410, TPS16411, TPS16414, and TPS16415

Active Power Limiting (PLIM) With the TPS16410, TPS16411, TPS16414, and TPS16415

Internal Current Limit for the TPS16410 and TPS16411

Internal Current Limit for the TPS16410 and TPS16411

Overcurrent Protection (IOCP) and Blanking Time (IDLY or PDLY) for Transient Loads

Overcurrent Protection (IOCP) and Blanking Time (IDLY or PDLY) for Transient Loads

Fast-Trip and Short-Circuit Protection

Fast-Trip and Short-Circuit Protection

Analog Load Current Monitor (IMON) on the IOCP Pin

Analog Load Current Monitor (IMON) on the IOCP Pin

IN to OUT Short Detection (TPS16410, TPS16411, TPS16412, and TPS16413)

IN to OUT Short Detection (TPS16410, TPS16411, TPS16412, and TPS16413)

Thermal Shutdown and Overtemperature Protection

Thermal Shutdown and Overtemperature Protection

Fault Response and Indication (FLT)

Fault Response and Indication (FLT)

Device Functional Modes

Device Functional Modes

Application and Implementation

Application and Implementation

Application Information

Application Information

Typical Application: 15-W Power Limiting for Low Power Circuits (LPCs)

Typical Application: 15-W Power Limiting for Low Power Circuits (LPCs)

Design Requirements

Design Requirements

Detailed Design Procedure

Detailed Design Procedure

Setting Overvoltage Setpoints

Setting Overvoltage Setpoints

Setting the Output Overcurrent Setpoint (IOCP)

Setting the Output Overcurrent Setpoint (IOCP)

Setting the Output Power Limit

Setting the Output Power Limit

Monitoring the Output Current

Monitoring the Output Current

Limiting the Inrush Current and Setting the Output Slew Rate

Limiting the Inrush Current and Setting the Output Slew Rate

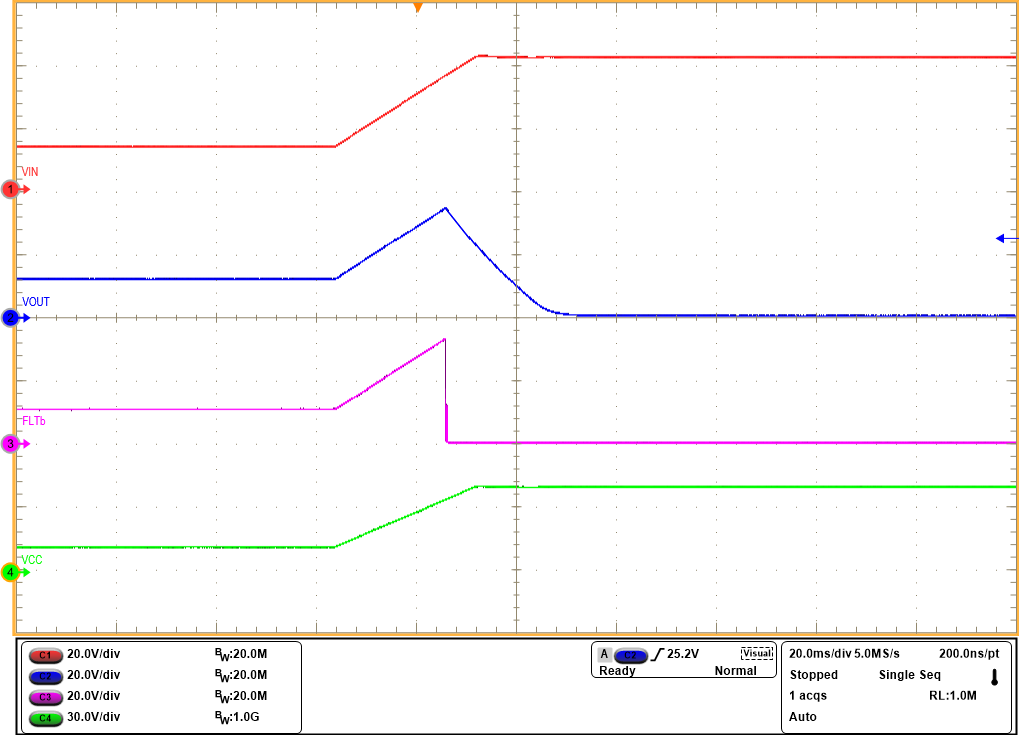

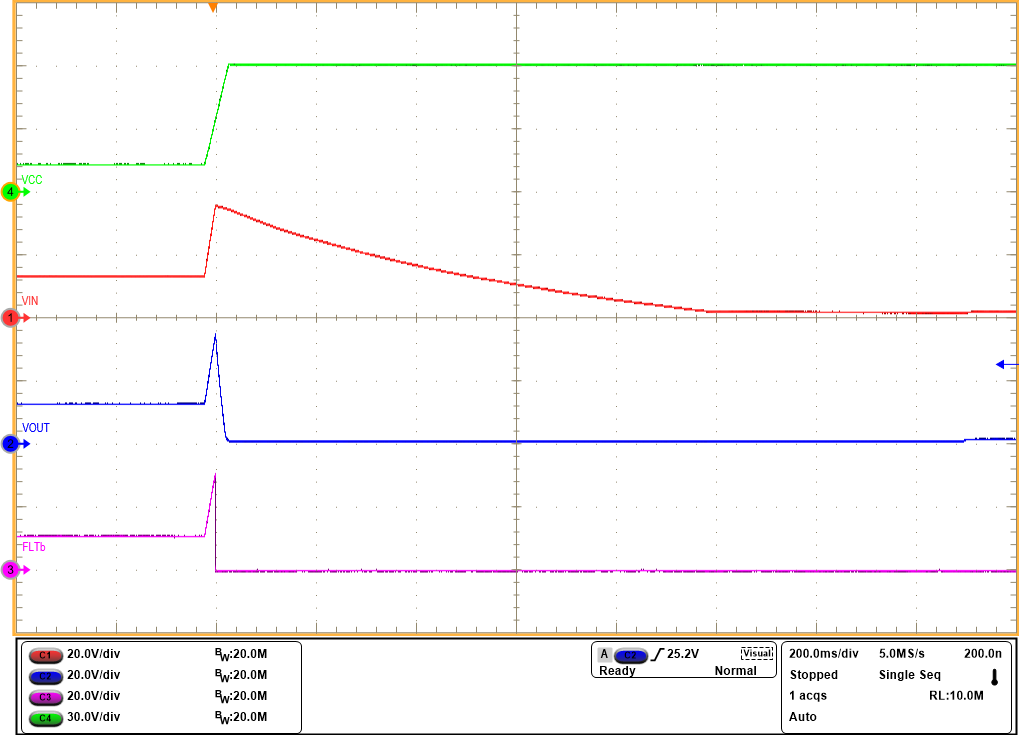

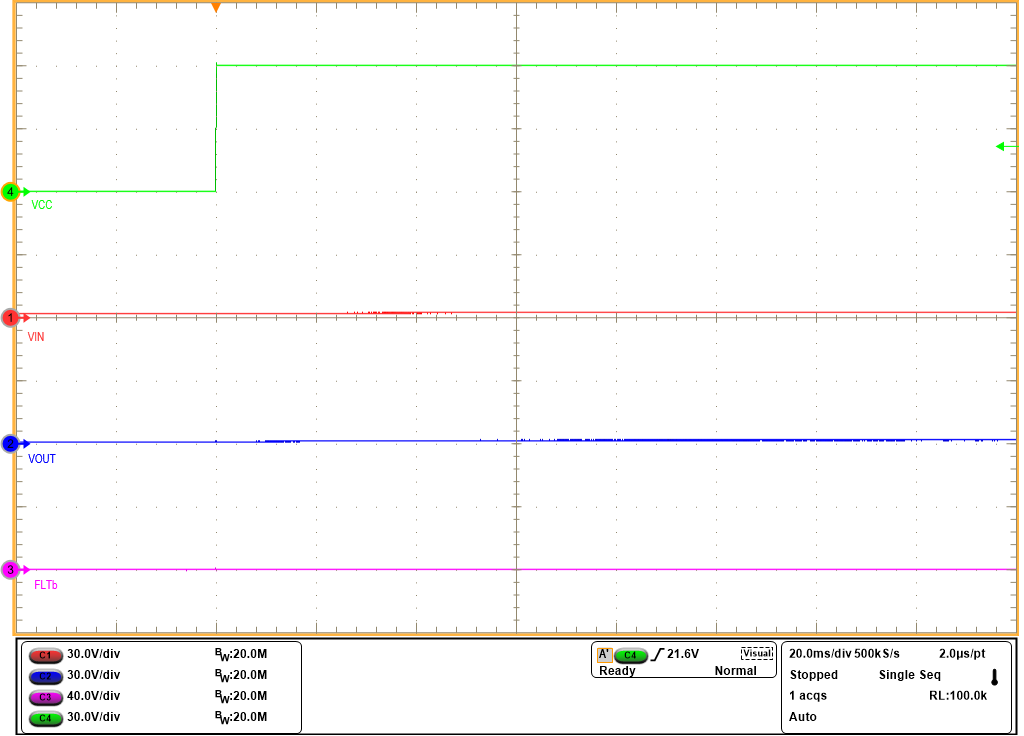

Application Curves

Application Curves

System Examples

System Examples

Accurate Power or Current Limiting at the Output of DC/DC or Flyback Converter

Accurate Power or Current Limiting at the Output of DC/DC or Flyback Converter

Best Design Practices

Best Design Practices

Power Supply Recommendations

Power Supply Recommendations

Transient Protection

Transient Protection

Layout

Layout

Layout Guidelines

Layout Guidelines

Layout Example

Layout Example

Device and Documentation Support

Device and Documentation Support

接收文档更新通知

接收文档更新通知

支持资源

支持资源

Trademarks

Trademarks

静电放电警告

静电放电警告

术语表

术语表

Mechanical, Packaging, and Orderable Information

Mechanical, Packaging, and Orderable Information

重要声明和免责声明

重要声明和免责声明

TPS1641x 具有输入至输出短路检测功能的 40V、1.8A 功率和

电流限制型电子保险丝

TPS1641x 具有输入至输出短路检测功能的 40V、1.8A 功率和

电流限制型电子保险丝

特性

B

20230421

在整个文档中添加了有关新器件型号的信息

yes

工作电压范围 (IN):

4.5V 至 40V(功率限制器件)

2.7V 至 40V(电流限制器件)

输出端可耐受高达 -1V 的负电压

超低导通电阻:RON = 152mΩ(典型值)

2W 至 64W 功率限制

0.03A 至 1.8A 电流限制

FLT引脚上的 IN 到 OUT 短路检测和指示

用于诊断和驱动外部 PFET 的 FLT 输出

15W 时 ±5% 精确功率限制(功率限制器件)

1A 时 ±6% 精确电流限制(电流限制器件)

可配置的过压保护

可配置过流保护 (IOCP)

可针对瞬态电流配置消隐时间

通过外部 FET 提供高达 60V 的过压保护

可调节输出压摆率控制 (dVdt),用于提供浪涌电流保护

使能和关断控制

IOCP 引脚上的输出负载电流监控

具有热关断功能的过热保护 (OTP)

小尺寸: QFN 3 × 3mm,0.5mm 间距

特性

B

20230421

在整个文档中添加了有关新器件型号的信息

yes

B

20230421

在整个文档中添加了有关新器件型号的信息

yes

B

20230421

在整个文档中添加了有关新器件型号的信息

yes

B20230421在整个文档中添加了有关新器件型号的信息yes

工作电压范围 (IN):

4.5V 至 40V(功率限制器件)

2.7V 至 40V(电流限制器件)

输出端可耐受高达 -1V 的负电压

超低导通电阻:RON = 152mΩ(典型值)

2W 至 64W 功率限制

0.03A 至 1.8A 电流限制

FLT引脚上的 IN 到 OUT 短路检测和指示

用于诊断和驱动外部 PFET 的 FLT 输出

15W 时 ±5% 精确功率限制(功率限制器件)

1A 时 ±6% 精确电流限制(电流限制器件)

可配置的过压保护

可配置过流保护 (IOCP)

可针对瞬态电流配置消隐时间

通过外部 FET 提供高达 60V 的过压保护

可调节输出压摆率控制 (dVdt),用于提供浪涌电流保护

使能和关断控制

IOCP 引脚上的输出负载电流监控

具有热关断功能的过热保护 (OTP)

小尺寸: QFN 3 × 3mm,0.5mm 间距

工作电压范围 (IN):

4.5V 至 40V(功率限制器件)

2.7V 至 40V(电流限制器件)

输出端可耐受高达 -1V 的负电压

超低导通电阻:RON = 152mΩ(典型值)

2W 至 64W 功率限制

0.03A 至 1.8A 电流限制

FLT引脚上的 IN 到 OUT 短路检测和指示

用于诊断和驱动外部 PFET 的 FLT 输出

15W 时 ±5% 精确功率限制(功率限制器件)

1A 时 ±6% 精确电流限制(电流限制器件)

可配置的过压保护

可配置过流保护 (IOCP)

可针对瞬态电流配置消隐时间

通过外部 FET 提供高达 60V 的过压保护

可调节输出压摆率控制 (dVdt),用于提供浪涌电流保护

使能和关断控制

IOCP 引脚上的输出负载电流监控

具有热关断功能的过热保护 (OTP)

小尺寸: QFN 3 × 3mm,0.5mm 间距

工作电压范围 (IN):

4.5V 至 40V(功率限制器件)

2.7V 至 40V(电流限制器件)

输出端可耐受高达 -1V 的负电压

超低导通电阻:RON = 152mΩ(典型值)

2W 至 64W 功率限制

0.03A 至 1.8A 电流限制

FLT引脚上的 IN 到 OUT 短路检测和指示

用于诊断和驱动外部 PFET 的 FLT 输出

15W 时 ±5% 精确功率限制(功率限制器件)

1A 时 ±6% 精确电流限制(电流限制器件)

可配置的过压保护

可配置过流保护 (IOCP)

可针对瞬态电流配置消隐时间

通过外部 FET 提供高达 60V 的过压保护

可调节输出压摆率控制 (dVdt),用于提供浪涌电流保护

使能和关断控制

IOCP 引脚上的输出负载电流监控

具有热关断功能的过热保护 (OTP)

小尺寸: QFN 3 × 3mm,0.5mm 间距

工作电压范围 (IN):

4.5V 至 40V(功率限制器件)

2.7V 至 40V(电流限制器件)

4.5V 至 40V(功率限制器件)

2.7V 至 40V(电流限制器件)

4.5V 至 40V(功率限制器件)2.7V 至 40V(电流限制器件)输出端可耐受高达 -1V 的负电压超低导通电阻:RON = 152mΩ(典型值)ON2W 至 64W 功率限制0.03A 至 1.8A 电流限制

FLT引脚上的 IN 到 OUT 短路检测和指示FLT用于诊断和驱动外部 PFET 的 FLT 输出FLT15W 时 ±5% 精确功率限制(功率限制器件)1A 时 ±6% 精确电流限制(电流限制器件)可配置的过压保护可配置过流保护 (IOCP)OCP可针对瞬态电流配置消隐时间通过外部 FET 提供高达 60V 的过压保护可调节输出压摆率控制 (dVdt),用于提供浪涌电流保护使能和关断控制IOCP 引脚上的输出负载电流监控具有热关断功能的过热保护 (OTP)小尺寸: QFN 3 × 3mm,0.5mm 间距

应用

冰箱和冷冻柜

烤箱

洗碗机

HVAC 阀门和传动器控制

呼吸机

麻醉给药系统

应用

冰箱和冷冻柜

烤箱

洗碗机

HVAC 阀门和传动器控制

呼吸机

麻醉给药系统

冰箱和冷冻柜

烤箱

洗碗机

HVAC 阀门和传动器控制

呼吸机

麻醉给药系统

冰箱和冷冻柜

烤箱

洗碗机

HVAC 阀门和传动器控制

呼吸机

麻醉给药系统

冰箱和冷冻柜

冰箱和冷冻柜

烤箱

烤箱

洗碗机

洗碗机

HVAC 阀门和传动器控制

HVAC 阀门和传动器控制

呼吸机

呼吸机

麻醉给药系统

麻醉给药系统

说明

A

将器件状态从预告信息 更改为量产数据

yes

B

20230421

添加了新的器件型号

no

TPS1641x 系列是具有精确功率限值或电流限值的集成电子保险丝器件。该器件系列通过集成的过流保护、过压保护、输入至输出短路检测和过热保护提供强大的保护功能。

TPS16410、TPS16411、TPS16414 和 TPS16415 器件在 15W 下为负载提供 ±5% 的功率限制,并且还针对瞬态过载或过流事件提供可配置的消隐时间。TPS16410、TPS16411、TPS16414 和 TPS16415 可用于低功耗电路 (LPC),从而实现符合 IEC60335 和 UL60730 标准的 15W 功率限制。TPS1641x 器件可针对相邻引脚短路和引脚短路到 GND 故障提供保护。

PLC 和 DCS 模块中的背板电源保护等应用通过 ILIM 引脚上的电阻器配置电流限制。TPS16412、TPS16413、TPS16416 和 TPS16417 器件在 1A 时为负载提供 ±6% 的电流限制,而且还通过 dVdT 引脚提供输出压摆率控制,以便在上电时为大容性负载充电。

TPS1641x 具有输入至输出短路检测功能,并会在 FLT 引脚上指示输入至输出短路。FLT 引脚既可作为数字输入提供给 MCU,也可用于驱动外部 PFET。

此类器件的额定工作结温范围为 –40°C 至 +125°C。

封装信息

器件型号

封装#GUID-2FDB0C6F-DE70-4B29-80CD-054FD157EA75/GUID-3653871F-5AF1-4A52-A35A-0F101150B230

封装尺寸(标称值)

TPS1641x

VSON (10)

3.00mm × 3.00mm

有关所有的可用封装,请参阅数据表末尾的可订购米6体育平台手机版_好二三四附录。

简化原理图

可针对瞬态负载配置消隐时间

说明

A

将器件状态从预告信息 更改为量产数据

yes

B

20230421

添加了新的器件型号

no

A

将器件状态从预告信息 更改为量产数据

yes

B

20230421

添加了新的器件型号

no

A

将器件状态从预告信息 更改为量产数据

yes

A将器件状态从预告信息 更改为量产数据

预告信息量产数据yes

B

20230421

添加了新的器件型号

no

B20230421添加了新的器件型号no

TPS1641x 系列是具有精确功率限值或电流限值的集成电子保险丝器件。该器件系列通过集成的过流保护、过压保护、输入至输出短路检测和过热保护提供强大的保护功能。

TPS16410、TPS16411、TPS16414 和 TPS16415 器件在 15W 下为负载提供 ±5% 的功率限制,并且还针对瞬态过载或过流事件提供可配置的消隐时间。TPS16410、TPS16411、TPS16414 和 TPS16415 可用于低功耗电路 (LPC),从而实现符合 IEC60335 和 UL60730 标准的 15W 功率限制。TPS1641x 器件可针对相邻引脚短路和引脚短路到 GND 故障提供保护。

PLC 和 DCS 模块中的背板电源保护等应用通过 ILIM 引脚上的电阻器配置电流限制。TPS16412、TPS16413、TPS16416 和 TPS16417 器件在 1A 时为负载提供 ±6% 的电流限制,而且还通过 dVdT 引脚提供输出压摆率控制,以便在上电时为大容性负载充电。

TPS1641x 具有输入至输出短路检测功能,并会在 FLT 引脚上指示输入至输出短路。FLT 引脚既可作为数字输入提供给 MCU,也可用于驱动外部 PFET。

此类器件的额定工作结温范围为 –40°C 至 +125°C。

封装信息

器件型号

封装#GUID-2FDB0C6F-DE70-4B29-80CD-054FD157EA75/GUID-3653871F-5AF1-4A52-A35A-0F101150B230

封装尺寸(标称值)

TPS1641x

VSON (10)

3.00mm × 3.00mm

有关所有的可用封装,请参阅数据表末尾的可订购米6体育平台手机版_好二三四附录。

简化原理图

可针对瞬态负载配置消隐时间

TPS1641x 系列是具有精确功率限值或电流限值的集成电子保险丝器件。该器件系列通过集成的过流保护、过压保护、输入至输出短路检测和过热保护提供强大的保护功能。

TPS16410、TPS16411、TPS16414 和 TPS16415 器件在 15W 下为负载提供 ±5% 的功率限制,并且还针对瞬态过载或过流事件提供可配置的消隐时间。TPS16410、TPS16411、TPS16414 和 TPS16415 可用于低功耗电路 (LPC),从而实现符合 IEC60335 和 UL60730 标准的 15W 功率限制。TPS1641x 器件可针对相邻引脚短路和引脚短路到 GND 故障提供保护。

PLC 和 DCS 模块中的背板电源保护等应用通过 ILIM 引脚上的电阻器配置电流限制。TPS16412、TPS16413、TPS16416 和 TPS16417 器件在 1A 时为负载提供 ±6% 的电流限制,而且还通过 dVdT 引脚提供输出压摆率控制,以便在上电时为大容性负载充电。

TPS1641x 具有输入至输出短路检测功能,并会在 FLT 引脚上指示输入至输出短路。FLT 引脚既可作为数字输入提供给 MCU,也可用于驱动外部 PFET。

此类器件的额定工作结温范围为 –40°C 至 +125°C。

封装信息

器件型号

封装#GUID-2FDB0C6F-DE70-4B29-80CD-054FD157EA75/GUID-3653871F-5AF1-4A52-A35A-0F101150B230

封装尺寸(标称值)

TPS1641x

VSON (10)

3.00mm × 3.00mm

有关所有的可用封装,请参阅数据表末尾的可订购米6体育平台手机版_好二三四附录。

简化原理图

可针对瞬态负载配置消隐时间

TPS1641x 系列是具有精确功率限值或电流限值的集成电子保险丝器件。该器件系列通过集成的过流保护、过压保护、输入至输出短路检测和过热保护提供强大的保护功能。TPS16410、TPS16411、TPS16414 和 TPS16415 器件在 15W 下为负载提供 ±5% 的功率限制,并且还针对瞬态过载或过流事件提供可配置的消隐时间。TPS16410、TPS16411、TPS16414 和 TPS16415 可用于低功耗电路 (LPC),从而实现符合 IEC60335 和 UL60730 标准的 15W 功率限制。TPS1641x 器件可针对相邻引脚短路和引脚短路到 GND 故障提供保护。PLC 和 DCS 模块中的背板电源保护等应用通过 ILIM 引脚上的电阻器配置电流限制。TPS16412、TPS16413、TPS16416 和 TPS16417 器件在 1A 时为负载提供 ±6% 的电流限制,而且还通过 dVdT 引脚提供输出压摆率控制,以便在上电时为大容性负载充电。TPS1641x 具有输入至输出短路检测功能,并会在 FLT 引脚上指示输入至输出短路。FLT 引脚既可作为数字输入提供给 MCU,也可用于驱动外部 PFET。FLTFLT此类器件的额定工作结温范围为 –40°C 至 +125°C。

封装信息

器件型号

封装#GUID-2FDB0C6F-DE70-4B29-80CD-054FD157EA75/GUID-3653871F-5AF1-4A52-A35A-0F101150B230

封装尺寸(标称值)

TPS1641x

VSON (10)

3.00mm × 3.00mm

封装信息

器件型号

封装#GUID-2FDB0C6F-DE70-4B29-80CD-054FD157EA75/GUID-3653871F-5AF1-4A52-A35A-0F101150B230

封装尺寸(标称值)

TPS1641x

VSON (10)

3.00mm × 3.00mm

器件型号

封装#GUID-2FDB0C6F-DE70-4B29-80CD-054FD157EA75/GUID-3653871F-5AF1-4A52-A35A-0F101150B230

封装尺寸(标称值)

器件型号

封装#GUID-2FDB0C6F-DE70-4B29-80CD-054FD157EA75/GUID-3653871F-5AF1-4A52-A35A-0F101150B230

封装尺寸(标称值)

器件型号封装#GUID-2FDB0C6F-DE70-4B29-80CD-054FD157EA75/GUID-3653871F-5AF1-4A52-A35A-0F101150B230

#GUID-2FDB0C6F-DE70-4B29-80CD-054FD157EA75/GUID-3653871F-5AF1-4A52-A35A-0F101150B230封装尺寸(标称值)

TPS1641x

VSON (10)

3.00mm × 3.00mm

TPS1641x

VSON (10)

3.00mm × 3.00mm

TPS1641xVSON (10)3.00mm × 3.00mm

有关所有的可用封装,请参阅数据表末尾的可订购米6体育平台手机版_好二三四附录。

有关所有的可用封装,请参阅数据表末尾的可订购米6体育平台手机版_好二三四附录。

简化原理图

可针对瞬态负载配置消隐时间

简化原理图

简化原理图

可针对瞬态负载配置消隐时间

可针对瞬态负载配置消隐时间

Table of Contents

yes

2

Table of Contents

yes

2

yes

2

yes2

Revision History

yes

December 2022

April 2023

A

B

Revision History

yes

December 2022

April 2023

A

B

yes

December 2022

April 2023

A

B

yesDecember 2022April 2023AB

Revision History

yes

June 2022

December 2022

*

A

Revision History

yes

June 2022

December 2022

*

A

yes

June 2022

December 2022

*

A

yesJune 2022December 2022*A

Device Comparison Table

B

20230421

Added new device variants

no

Part Number

Power or Current Limit

Fault Behavior

IN-OUT Short Detection

TPS16410

Power limit

Auto-retry

Y

TPS16411

Power limit

Latch-off

Y

TPS16412

Current limit

Auto-retry

Y

TPS16413

Current limit

Latch-off

Y

TPS16414

Power limit

Auto-retry

N

TPS16415

Power limit

Latch-off

N

TPS16416

Current limit

Auto-retry

N

TPS16417

Current limit

Latch-off

N

See

IN to OUT Short Detection (TPS16410, TPS16411,

TPS16412, and TPS16413)

section for recommended device variants.

Device Comparison Table

B

20230421

Added new device variants

no

B

20230421

Added new device variants

no

B

20230421

Added new device variants

no

B20230421Added new device variantsno

Part Number

Power or Current Limit

Fault Behavior

IN-OUT Short Detection

TPS16410

Power limit

Auto-retry

Y

TPS16411

Power limit

Latch-off

Y

TPS16412

Current limit

Auto-retry

Y

TPS16413

Current limit

Latch-off

Y

TPS16414

Power limit

Auto-retry

N

TPS16415

Power limit

Latch-off

N

TPS16416

Current limit

Auto-retry

N

TPS16417

Current limit

Latch-off

N

See

IN to OUT Short Detection (TPS16410, TPS16411,

TPS16412, and TPS16413)

section for recommended device variants.

Part Number

Power or Current Limit

Fault Behavior

IN-OUT Short Detection

TPS16410

Power limit

Auto-retry

Y

TPS16411

Power limit

Latch-off

Y

TPS16412

Current limit

Auto-retry

Y

TPS16413

Current limit

Latch-off

Y

TPS16414

Power limit

Auto-retry

N

TPS16415

Power limit

Latch-off

N

TPS16416

Current limit

Auto-retry

N

TPS16417

Current limit

Latch-off

N

See

IN to OUT Short Detection (TPS16410, TPS16411,

TPS16412, and TPS16413)

section for recommended device variants.

Part Number

Power or Current Limit

Fault Behavior

IN-OUT Short Detection

TPS16410

Power limit

Auto-retry

Y

TPS16411

Power limit

Latch-off

Y

TPS16412

Current limit

Auto-retry

Y

TPS16413

Current limit

Latch-off

Y

TPS16414

Power limit

Auto-retry

N

TPS16415

Power limit

Latch-off

N

TPS16416

Current limit

Auto-retry

N

TPS16417

Current limit

Latch-off

N

Part Number

Power or Current Limit

Fault Behavior

IN-OUT Short Detection

TPS16410

Power limit

Auto-retry

Y

TPS16411

Power limit

Latch-off

Y

TPS16412

Current limit

Auto-retry

Y

TPS16413

Current limit

Latch-off

Y

TPS16414

Power limit

Auto-retry

N

TPS16415

Power limit

Latch-off

N

TPS16416

Current limit

Auto-retry

N

TPS16417

Current limit

Latch-off

N

Part Number

Power or Current Limit

Fault Behavior

IN-OUT Short Detection

Part Number

Power or Current Limit

Fault Behavior

IN-OUT Short Detection

Part NumberPower or Current LimitFault BehaviorIN-OUT Short Detection

TPS16410

Power limit

Auto-retry

Y

TPS16411

Power limit

Latch-off

Y

TPS16412

Current limit

Auto-retry

Y

TPS16413

Current limit

Latch-off

Y

TPS16414

Power limit

Auto-retry

N

TPS16415

Power limit

Latch-off

N

TPS16416

Current limit

Auto-retry

N

TPS16417

Current limit

Latch-off

N

TPS16410

Power limit

Auto-retry

Y

TPS16410Power limitAuto-retryY

TPS16411

Power limit

Latch-off

Y

TPS16411Power limitLatch-offY

TPS16412

Current limit

Auto-retry

Y

TPS16412Current limitAuto-retryY

TPS16413

Current limit

Latch-off

Y

TPS16413Current limitLatch-offY

TPS16414

Power limit

Auto-retry

N

TPS16414Power limitAuto-retryN

TPS16415

Power limit

Latch-off

N

TPS16415Power limitLatch-offN

TPS16416

Current limit

Auto-retry

N

TPS16416Current limitAuto-retryN

TPS16417

Current limit

Latch-off

N

TPS16417Current limitLatch-offNSee

IN to OUT Short Detection (TPS16410, TPS16411,

TPS16412, and TPS16413)

section for recommended device variants.

IN to OUT Short Detection (TPS16410, TPS16411,

TPS16412, and TPS16413)

IN to OUT Short Detection (TPS16410, TPS16411,

TPS16412, and TPS16413)

Pin Configuration and Functions

B

20230421

Added new

device variants

no

TPS16410,

TPS16411, TPS16414 and TPS16415 10-Pin DRC VSON

Package

(Top View)

TPS16412,

TPS16413, TPS16416 and TPS16417 10-Pin DRC VSON

Package

(Top View)

Pin Functions

PIN

I/O

#GUID-7CD8F0E2-2565-41C1-A379-B1DE756A4972/GUID-5271DA12-D57C-46F2-8BEA-2C409D73BCF1

DESCRIPTION

NAME

NO.

IN

1

P

Power input for internal

FET.

Vcc

2

P

Supply input for internal circuits of the

device.

OVP

3

I

Overvoltage protection input. This pin can be

connected to GND for disabling OVP.

FLT

4

O

Active low fault output. See the

FLT Pin

Indication for Different Events

section for different

FLT pin indications.

EN/SHDN

5

I

Enable or shutdown

input.

PDLY

6

I/O

TPS16410, TPS16411: Input for blanking time for

power limiting. Connect a capacitor to set PDLY blanking

time.

IDLY

TPS16412, TPS16413: Input for blanking time for

current limiting. Connect a capacitor to set IDLY blanking

time.

dVdT

7

I/O

Output slew control input. Connect a capacitor to

set the output slew rate. If not used, this pin can be left

open.

PLIM

8

I/O

TPS16410, TPS16411: Power limit input. Connect a

resistor to set PLIM setpoint.

ILIM

TPS16412, TPS16413: Current limit input. Connect

a resistor to set ILIM setpoint.

IOCP/IMON

9

I/O

Overcurrent protection input and current

monitoring output for output current. Output current can be sensed

by reading voltage on this pin. Connect a resistor to set IOCP

set-point and for reading output current.

OUT

10

P

Power output from internal

FET.

PowerPAD/GND

—

G

GND connection for the device.

PowerPAD must be connected to GND of input power

supply.

Connect PowerPAD to GND plane on PCB using multiple vias for

enhanced thermal performance.

I = Input, O = Output, I/O =

Input or Output, G = Ground, P = Power

Pin Configuration and Functions

B

20230421

Added new

device variants

no

B

20230421

Added new

device variants

no

B

20230421

Added new

device variants

no

B20230421Added new

device variantsno

TPS16410,

TPS16411, TPS16414 and TPS16415 10-Pin DRC VSON

Package

(Top View)

TPS16412,

TPS16413, TPS16416 and TPS16417 10-Pin DRC VSON

Package

(Top View)

Pin Functions

PIN

I/O

#GUID-7CD8F0E2-2565-41C1-A379-B1DE756A4972/GUID-5271DA12-D57C-46F2-8BEA-2C409D73BCF1

DESCRIPTION

NAME

NO.

IN

1

P

Power input for internal

FET.

Vcc

2

P

Supply input for internal circuits of the

device.

OVP

3

I

Overvoltage protection input. This pin can be

connected to GND for disabling OVP.

FLT

4

O

Active low fault output. See the

FLT Pin

Indication for Different Events

section for different

FLT pin indications.

EN/SHDN

5

I

Enable or shutdown

input.

PDLY

6

I/O

TPS16410, TPS16411: Input for blanking time for

power limiting. Connect a capacitor to set PDLY blanking

time.

IDLY

TPS16412, TPS16413: Input for blanking time for

current limiting. Connect a capacitor to set IDLY blanking

time.

dVdT

7

I/O

Output slew control input. Connect a capacitor to

set the output slew rate. If not used, this pin can be left

open.

PLIM

8

I/O

TPS16410, TPS16411: Power limit input. Connect a

resistor to set PLIM setpoint.

ILIM

TPS16412, TPS16413: Current limit input. Connect

a resistor to set ILIM setpoint.

IOCP/IMON

9

I/O

Overcurrent protection input and current

monitoring output for output current. Output current can be sensed

by reading voltage on this pin. Connect a resistor to set IOCP

set-point and for reading output current.

OUT

10

P

Power output from internal

FET.

PowerPAD/GND

—

G

GND connection for the device.

PowerPAD must be connected to GND of input power

supply.

Connect PowerPAD to GND plane on PCB using multiple vias for

enhanced thermal performance.

I = Input, O = Output, I/O =

Input or Output, G = Ground, P = Power

TPS16410,

TPS16411, TPS16414 and TPS16415 10-Pin DRC VSON

Package

(Top View)

TPS16412,

TPS16413, TPS16416 and TPS16417 10-Pin DRC VSON

Package

(Top View)

Pin Functions

PIN

I/O

#GUID-7CD8F0E2-2565-41C1-A379-B1DE756A4972/GUID-5271DA12-D57C-46F2-8BEA-2C409D73BCF1

DESCRIPTION

NAME

NO.

IN

1

P

Power input for internal

FET.

Vcc

2

P

Supply input for internal circuits of the

device.

OVP

3

I

Overvoltage protection input. This pin can be

connected to GND for disabling OVP.

FLT

4

O

Active low fault output. See the

FLT Pin

Indication for Different Events

section for different

FLT pin indications.

EN/SHDN

5

I

Enable or shutdown

input.

PDLY

6

I/O

TPS16410, TPS16411: Input for blanking time for

power limiting. Connect a capacitor to set PDLY blanking

time.

IDLY

TPS16412, TPS16413: Input for blanking time for

current limiting. Connect a capacitor to set IDLY blanking

time.

dVdT

7

I/O

Output slew control input. Connect a capacitor to

set the output slew rate. If not used, this pin can be left

open.

PLIM

8

I/O

TPS16410, TPS16411: Power limit input. Connect a

resistor to set PLIM setpoint.

ILIM

TPS16412, TPS16413: Current limit input. Connect

a resistor to set ILIM setpoint.

IOCP/IMON

9

I/O

Overcurrent protection input and current

monitoring output for output current. Output current can be sensed

by reading voltage on this pin. Connect a resistor to set IOCP

set-point and for reading output current.

OUT

10

P

Power output from internal

FET.

PowerPAD/GND

—

G

GND connection for the device.

PowerPAD must be connected to GND of input power

supply.

Connect PowerPAD to GND plane on PCB using multiple vias for

enhanced thermal performance.

I = Input, O = Output, I/O =

Input or Output, G = Ground, P = Power

TPS16410,

TPS16411, TPS16414 and TPS16415 10-Pin DRC VSON

Package

(Top View)

TPS16412,

TPS16413, TPS16416 and TPS16417 10-Pin DRC VSON

Package

(Top View)

TPS16410,

TPS16411, TPS16414 and TPS16415 10-Pin DRC VSON

Package

(Top View)

TPS16410,

TPS16411, TPS16414 and TPS16415 10-Pin DRC VSON

Package

(Top View)

TPS16412,

TPS16413, TPS16416 and TPS16417 10-Pin DRC VSON

Package

(Top View)

TPS16412,

TPS16413, TPS16416 and TPS16417 10-Pin DRC VSON

Package

(Top View)

Pin Functions

PIN

I/O

#GUID-7CD8F0E2-2565-41C1-A379-B1DE756A4972/GUID-5271DA12-D57C-46F2-8BEA-2C409D73BCF1

DESCRIPTION

NAME

NO.

IN

1

P

Power input for internal

FET.

Vcc

2

P

Supply input for internal circuits of the

device.

OVP

3

I

Overvoltage protection input. This pin can be

connected to GND for disabling OVP.

FLT

4

O

Active low fault output. See the

FLT Pin

Indication for Different Events

section for different

FLT pin indications.

EN/SHDN

5

I

Enable or shutdown

input.

PDLY

6

I/O

TPS16410, TPS16411: Input for blanking time for

power limiting. Connect a capacitor to set PDLY blanking

time.

IDLY

TPS16412, TPS16413: Input for blanking time for

current limiting. Connect a capacitor to set IDLY blanking

time.

dVdT

7

I/O

Output slew control input. Connect a capacitor to

set the output slew rate. If not used, this pin can be left

open.

PLIM

8

I/O

TPS16410, TPS16411: Power limit input. Connect a

resistor to set PLIM setpoint.

ILIM

TPS16412, TPS16413: Current limit input. Connect

a resistor to set ILIM setpoint.

IOCP/IMON

9

I/O

Overcurrent protection input and current

monitoring output for output current. Output current can be sensed

by reading voltage on this pin. Connect a resistor to set IOCP

set-point and for reading output current.

OUT

10

P

Power output from internal

FET.

PowerPAD/GND

—

G

GND connection for the device.

PowerPAD must be connected to GND of input power

supply.

Connect PowerPAD to GND plane on PCB using multiple vias for

enhanced thermal performance.

Pin Functions

PIN

I/O

#GUID-7CD8F0E2-2565-41C1-A379-B1DE756A4972/GUID-5271DA12-D57C-46F2-8BEA-2C409D73BCF1

DESCRIPTION

NAME

NO.

IN

1

P

Power input for internal

FET.

Vcc

2

P

Supply input for internal circuits of the

device.

OVP

3

I

Overvoltage protection input. This pin can be

connected to GND for disabling OVP.

FLT

4

O

Active low fault output. See the

FLT Pin

Indication for Different Events

section for different

FLT pin indications.

EN/SHDN

5

I

Enable or shutdown

input.

PDLY

6

I/O

TPS16410, TPS16411: Input for blanking time for

power limiting. Connect a capacitor to set PDLY blanking

time.

IDLY

TPS16412, TPS16413: Input for blanking time for

current limiting. Connect a capacitor to set IDLY blanking

time.

dVdT

7

I/O

Output slew control input. Connect a capacitor to

set the output slew rate. If not used, this pin can be left

open.

PLIM

8

I/O

TPS16410, TPS16411: Power limit input. Connect a

resistor to set PLIM setpoint.

ILIM

TPS16412, TPS16413: Current limit input. Connect

a resistor to set ILIM setpoint.

IOCP/IMON

9

I/O

Overcurrent protection input and current

monitoring output for output current. Output current can be sensed

by reading voltage on this pin. Connect a resistor to set IOCP

set-point and for reading output current.

OUT

10

P

Power output from internal

FET.

PowerPAD/GND

—

G

GND connection for the device.

PowerPAD must be connected to GND of input power

supply.

Connect PowerPAD to GND plane on PCB using multiple vias for

enhanced thermal performance.

PIN

I/O

#GUID-7CD8F0E2-2565-41C1-A379-B1DE756A4972/GUID-5271DA12-D57C-46F2-8BEA-2C409D73BCF1

DESCRIPTION

NAME

NO.

PIN

I/O

#GUID-7CD8F0E2-2565-41C1-A379-B1DE756A4972/GUID-5271DA12-D57C-46F2-8BEA-2C409D73BCF1

DESCRIPTION

PINI/O

#GUID-7CD8F0E2-2565-41C1-A379-B1DE756A4972/GUID-5271DA12-D57C-46F2-8BEA-2C409D73BCF1

#GUID-7CD8F0E2-2565-41C1-A379-B1DE756A4972/GUID-5271DA12-D57C-46F2-8BEA-2C409D73BCF1

#GUID-7CD8F0E2-2565-41C1-A379-B1DE756A4972/GUID-5271DA12-D57C-46F2-8BEA-2C409D73BCF1DESCRIPTION

NAME

NO.

NAMENO.

IN

1

P

Power input for internal

FET.

Vcc

2

P

Supply input for internal circuits of the

device.

OVP

3

I

Overvoltage protection input. This pin can be

connected to GND for disabling OVP.

FLT

4

O

Active low fault output. See the

FLT Pin

Indication for Different Events

section for different

FLT pin indications.

EN/SHDN

5

I

Enable or shutdown

input.

PDLY

6

I/O

TPS16410, TPS16411: Input for blanking time for

power limiting. Connect a capacitor to set PDLY blanking

time.

IDLY

TPS16412, TPS16413: Input for blanking time for

current limiting. Connect a capacitor to set IDLY blanking

time.

dVdT

7

I/O

Output slew control input. Connect a capacitor to

set the output slew rate. If not used, this pin can be left

open.

PLIM

8

I/O

TPS16410, TPS16411: Power limit input. Connect a

resistor to set PLIM setpoint.

ILIM

TPS16412, TPS16413: Current limit input. Connect

a resistor to set ILIM setpoint.

IOCP/IMON

9

I/O

Overcurrent protection input and current

monitoring output for output current. Output current can be sensed

by reading voltage on this pin. Connect a resistor to set IOCP

set-point and for reading output current.

OUT

10

P

Power output from internal

FET.

PowerPAD/GND

—

G

GND connection for the device.

PowerPAD must be connected to GND of input power

supply.

Connect PowerPAD to GND plane on PCB using multiple vias for

enhanced thermal performance.

IN

1

P

Power input for internal

FET.

IN

IN1PPower input for internal

FET.

Vcc

2

P

Supply input for internal circuits of the

device.

Vcc

cc2PSupply input for internal circuits of the

device.

OVP

3

I

Overvoltage protection input. This pin can be

connected to GND for disabling OVP.

OVP

OVP3IOvervoltage protection input. This pin can be

connected to GND for disabling OVP.

FLT

4

O

Active low fault output. See the

FLT Pin

Indication for Different Events

section for different

FLT pin indications.

FLT

FLT4OActive low fault output. See the

FLT Pin

Indication for Different Events

section for different

FLT pin indications.

FLT Pin

Indication for Different Events

FLT Pin

Indication for Different Events

FLT Pin

Indication for Different EventsFLTFLT

EN/SHDN

5

I

Enable or shutdown

input.

EN/SHDN

EN/SHDN

SHDN5IEnable or shutdown

input.

PDLY

6

I/O

TPS16410, TPS16411: Input for blanking time for

power limiting. Connect a capacitor to set PDLY blanking

time.

PDLY6I/OTPS16410, TPS16411: Input for blanking time for

power limiting. Connect a capacitor to set PDLY blanking

time.

IDLY

TPS16412, TPS16413: Input for blanking time for

current limiting. Connect a capacitor to set IDLY blanking

time.

IDLYTPS16412, TPS16413: Input for blanking time for

current limiting. Connect a capacitor to set IDLY blanking

time.

dVdT

7

I/O

Output slew control input. Connect a capacitor to

set the output slew rate. If not used, this pin can be left

open.

dVdT

dVdT 7I/OOutput slew control input. Connect a capacitor to

set the output slew rate. If not used, this pin can be left

open.

PLIM

8

I/O

TPS16410, TPS16411: Power limit input. Connect a

resistor to set PLIM setpoint.

PLIM8I/OTPS16410, TPS16411: Power limit input. Connect a

resistor to set PLIM setpoint.

ILIM

TPS16412, TPS16413: Current limit input. Connect

a resistor to set ILIM setpoint.

ILIMTPS16412, TPS16413: Current limit input. Connect

a resistor to set ILIM setpoint.

IOCP/IMON

9

I/O

Overcurrent protection input and current

monitoring output for output current. Output current can be sensed

by reading voltage on this pin. Connect a resistor to set IOCP

set-point and for reading output current.

IOCP/IMON9I/OOvercurrent protection input and current

monitoring output for output current. Output current can be sensed

by reading voltage on this pin. Connect a resistor to set IOCP

set-point and for reading output current.

OUT

10

P

Power output from internal

FET.

OUT10PPower output from internal

FET.

PowerPAD/GND

—

G

GND connection for the device.

PowerPAD must be connected to GND of input power

supply.

Connect PowerPAD to GND plane on PCB using multiple vias for

enhanced thermal performance.

PowerPAD/GND—GGND connection for the device.

PowerPAD must be connected to GND of input power

supply.

Connect PowerPAD to GND plane on PCB using multiple vias for

enhanced thermal performance.

PowerPAD must be connected to GND of input power

supply. PowerPADConnect PowerPAD to GND plane on PCB using multiple vias for

enhanced thermal performance.

I = Input, O = Output, I/O =

Input or Output, G = Ground, P = Power

I = Input, O = Output, I/O =

Input or Output, G = Ground, P = Power

Specifications

Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315321/A_6534948C_E24A_405C_8CF7_C493A4C1CD37_TPS1641X_SF_UPLOAD_TABLE_1_ABSMAX_FOOTER1

MIN

MAX

UNIT

Vcc, FLT

Input Voltage

–0.3

67

V

OVP

Input Voltage

–0.3

62

V

IN, IN-OUT, IOCP

Input Voltage

–0.3

42

V

OUT

Input Voltage

–1

42

V

EN/SHDN, PDLY/IDLY

Input Voltage

–0.3

5.5

V

dVdT, PLIM/ILIM

Input Voltage

–0.3

5.5

V

IIOCP,IPDLY,IPLIM, IdVdT, IILIM

Source Current

Internally Limited

TJ

Junction temperature

–40

150

°C

Transient Junction Temperature

–40

TTSD

°C

Tstg

Storage temperature

–65

150

°C

Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

ESD Ratings

VALUE

UNIT

V(ESD)

Electrostatic discharge

Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315322/A_6534948C_E24A_405C_8CF7_C493A4C1CD37_TPS1641X_SF_UPLOAD_TABLE_2_ESDRATINGS_COMMERCIAL_FOOTER1

±1500

V

Charged device model (CDM), per JEDEC specification JS-002, all pins#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315322/A_6534948C_E24A_405C_8CF7_C493A4C1CD37_TPS1641X_SF_UPLOAD_TABLE_2_ESDRATINGS_COMMERCIAL_FOOTER2

±500

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

MIN

NOM

MAX

UNIT

Vcc

Supply voltage

VIN

60

V

FLT

Input Voltage

0

60

V

IN

Input Voltage (TPS16410, TPS16411, TPS16414, TPS16415)

4.5

40

V

IN

Input Voltage (TPS16412, TPS16413, TPS16416, TPS16417)

2.7

40

V

OUT

Input Voltage

0

40

V

EN/SHDN, OVP

Input Voltage

0

5.5

V

PDLY/IDLY

External capacitor

0.012

10

µF

dVdT

External capacitor

0.01

5

µF

IOCP

External resistor

6.34

80.6

kΩ

PLIM

External resistor

12.4

412

kΩ

ILIM

External resistor

5.1

348

kΩ

TJ

Junction temperature

–40

125

°C

Thermal Information

THERMAL METRIC#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315335/A_TPS2661X_SF_OTHER_TABLES_4_THERMAL_1PKG_FOOTER1

TPS1641

UNIT

DRC (VSON)

10 PINS

RθJA

Junction-to-ambient thermal resistance

43.7

°C/W

RθJC(top)

Junction-to-case (top) thermal resistance

50.0

°C/W

RθJB

Junction-to-board thermal resistance

15.8

°C/W

ΨJT

Junction-to-top characterization parameter

1.1

°C/W

ΨJB

Junction-to-board characterization parameter

15.8

°C/W

RθJC(bot)

Junction-to-case (bottom) thermal resistance

2.1

°C/W

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Electrical Characteristics

–40°C ≤ TA = TJ ≤ +125°C, VIN = 3 V to 40 V (TPS16412, TPS16413, TPS16416, TPS16417), VIN = 4.5 V to 40 V (TPS16410, TPS16411, TPS16414, TPS16415), Vcc = VIN, RILIM = 5.49 kΩ RPLIM = 255 kΩ RIOCP = 7.32 kΩ , FLT = Open, COUT = 100 nF, CIN = 10 nF CdVdT = Open, PDLY/IDLY = Open. , EN/SHDN = Open(Allvoltages referenced to GND, (unless otherwise noted))

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

OPERATING INPUT AND SUPPLY VOLTAGE

Vcc

Operating Supply voltage

VIN

60

V

VIN

Operating Input voltage

TPS16410, TPS16411, TPS16414 ,TPS16415

4.5

40

V

VIN

Operating Input voltage

TPS16412, TPS16413, TPS16416, TPS16417

2.7

40

V

IQ

Operting Supply curent (Vcc)

EN/SHDN = 2 V, Vcc = 40 V, VIN = Open, RILIM or RPLIM = Open

1.2

2.1

mA

IQSD

Shutdown Supply current (Vcc)

EN/SHDN = GND, Vcc = 40 V, VIN = Open, RILIM or RPLIM = Open, RIOCP = Open

14

36

µA

IINLKG

IN Leakage Current in ON State

EN/SHDN = 2 V, VIN = Vcc = 40 V, Open, RILIM or RPLIM = Open

0.025

0.52

mA

IINLKG-SD

IN Leakage Current in Shutdown

EN/SHDN = GND,VIN = Vcc = 40 V, RILIM or RPLIM = Open, RIOCP = Open

0.7

2.8

µA

OVER-VOLTAGE PROTECTION (OVP) INPUT

VOVPR

OVP rising threshold

1.48

1.53

1.58

V

VOVPF

OVP falling threshold

1.34

1.40

1.46

V

IOVP

OVP leakage current

0 V ≤ VOVP ≤ 4 V

–350

–265

–200

nA

EN/SHDN INPUT

VENR

Enable rising threshold

1.2

V

VENF

Enable falling threshold

0.59

V

IEN

Enable leakage current

0 V ≤ VEN ≤ 4 V

–10

µA

VEN-Open

Open circuit Enable Voltage

IEN = 0.1 µA, VCC ≥ 5 V

4.9

V

OUTPUT POWER LIMITING (PLIM)

POUT

Output Power Limit

RPLIM = 26.7 kΩ

3

3.66

4.5

W

POUT

Output Power Limit

RPLIM = 95.3 kΩ, –40°C ≤ TA ≤ +85°C

12.94

13.69

14.44

W

POUT

Output Power Limit

RPLIM = 255 kΩ, –40°C ≤ TA ≤ +85°C

34

37

39.8

W

OUTPUT CURRENT LIMITING (ILIM)

IOUT

Output Current Limit

RILIM = 332 kΩ

0.024

0.032

0.039

A

IOUT

Output Current Limit

RILIM = 10 kΩ, –40°C ≤ TA ≤ +85°C

0.918

0.987

1.035

A

IOUT

Output Current Limit

RILIM = 5.49 kΩ, –40°C ≤ TA ≤ +85°C

1.671

1.77

1.881

A

POWER OUTPUT (OUT)

RON

IN to OUT On resistance

–40°C ≤ TJ ≤ 125°C

96

153

260

mΩ

RON

IN to OUT On resistance

0°C ≤ TJ ≤ 85°C

153

215

mΩ

RON

IN to OUT On resistance

TJ = 25°C

153

160

mΩ

ILKG-OUT

Output Leakage current in OFF state

VIN = 40 V, VOUT = 0 V, EN = Low

–15

–1.2

µA

CURRENT MONITORING OUTPUT (IMON)

GIMON

Gain : IMON/IOUT

IOUT = 0.05 to 1.8 A

45

50

55

µA/A

OSIMON

IMON Offset current

IOUT = 0.3 to 0.8 A

–0.8

0.05

0.8

µA

OVER CURRENT PROTECTION (IOCP) AND SHORT CIRCUIT PROTECTION (ISCP)

IOCP

Over curret protection set-point

RIOCP = 7.32 kΩ

2.11

2.23

2.35

A

IOCP

Over curret protection set-point

RIOCP = 16.2 kΩ

0.95

1.01

1.07

A

IFasttrip

Fast Trip protection threshold

1.9 × IOCP

A

ISCP

Short circuit protection threshold

6.7

A

ILIM-Internal

Internal Current Limit

TPS16410, TPS16411, TPS16414, TPS16415

0.81 × IOCP

A

THERMAL PROTECTION and SHUTDOWN (TTSD)

TTSD

Thermal shutdown temperature

155

°C

TTSD-hyst

Thermal shutdown temperature hysteresis

12

°C

Output slew rate control (dVdT)

IdVdT

dVdT charging current

1.78

2

2.23

µA

GdVdT

dVdT Gain

50

V/V

FLT Output (FLTb) (Open Drain Output)

RFLTb

Fault pin pull down resistance

73

Ω

IFLTb-LKG

Fault pin leakage current

FLT is High, V

FLT

≤ 25 V

–1

0.005

1

µA

IN to OUT Short Detection (TPS16410, TPS16411, TPS16412 , TPS16413)

Rshort

Resistance for IN to OUT short detection

30

mΩ

Timing Requirements

–40°C ≤ TA = TJ ≤ +125°C, VIN = 3 V to 40 V (TPS16412, TPS16413), VIN = 4.5 V to 40 V (TPS16410, TPS16411), VCC = VIN, VEN = 2 V, RILIM = 5.49 kΩ RPLIM = 255 kΩ RIOCP = 7.32 kΩ , FLT = Open, COUT = 100 nF, CIN = 10 nF CdVdT = Open, PDLY = Open. (Allvoltages referenced to GND, (unless otherwise noted))

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

Enable/SHDN and Vcc Input

tON_DLY

Turn on delay with VCC

VEN = VENR + 0.1 V , RLOAD = Open

500

µs

tEN_ON_DLY

Enable on delay

Fast turn-on with Enable when device is not in shutdown, VEN = VENR + 0.1 V , RLOAD = Open

270

µs

tEN_OFF_DLY

Enable off delay

VEN < VENF to VOUT = 0.9 × VIN, , RLOAD = 100

1.2

µs

tLOW_SHDN

Min low pulse for entering shutdown

RLOAD = 100

24

ms

OVP Input

tOVP_ENTRY_DLY

OVP entry delay

VOVP = VOVPR + 25 mV to FLT Low

0.75

µs

tOVP_EXIT_DLY

OVP exit delay

VOVP = VOVPF - 25 mV to to FLT High

0.6

µs

Over Current Protection and Short-circuit protection

tFASTTRIP_DLY

Fast Trip protection delay

IFASTTRIP < IOUT < ISCP to FET OFF

5.65

µs

tSCP_DLY

Short-Circuit protection delay

IOUT = ISCP + 500 mA to FET OFF

280

ns

Power Limiting

tPDLY

Blanking time before power limiting

IOUT < IOCP, POUT = 1.2 x PLIM, CDLY = 12 nF

6.5

ms

tPLIM-RES

Power Limit response time

IOUT < IOCP, IOUT = 1.2 x ILIM, CDLY = OPEN

215

µs

tPLIM-DUR

PowerLimit Duration

2 x tPDLY

s

Current Limiting

tIDLY

Blanking time before current limiting

IOUT < IOCP, IOUT = 1.2 x ILIM, CDLY = 12 nF

6.5

ms

tILIM-RES

Current Limit response time

IOUT < IOCP, IOUT = 1.2 x ILIM, CDLY = OPEN

280

µs

tILIM-DUR

Current Limit Duration

2 x tPDLY

s

Auto-Retry and Thermal Shutdown

tRETRY

Retry Delay

8 x tPDLY

s

Output Ramp Control (dVdT)

tdVdT

Output Ramp Time

CdVdT = Open, VIN = VCC = 24 V

105

µs

IN to OUT Short (TPS16410, TPS16411, TPS16412, TPS16413) and FLT Output

tIN_OUT_Short_Detect

IN to OUT short detection time when FET is ON

IN-OUT Short to FLT Low

135

ms

tIN_OUT_Short_Detect

IN to OUT short detection time when FET is OFF

IN-OUT Short to FLT Low

20

ms

Typical Characteristics

–40 °C ≤ TA = TJ

≤ +125 °C, VIN = 4.5 V to 40 V, Vcc = VIN, RILIM = 5.49 kΩ

RPLIM = 255 kΩ RIOCP = 7.32 kΩ , FLT

= Open, COUT = 100 nF, CIN = 100 nF CdVdT = Open,

PDLY = Open. , EN/SHDN = Open (All voltages referenced to GND, (unless otherwise

noted))

IQ-ON vs

Temperature

IQSD vs

Temperature

ILKG-VIN vs

Temperature

ILKG-VIN-SD vs

Temperature

RDS-ON vs

Temperature

GdVdT vs

Temperature

IdVdT vs

Temperature

GIMON vs

Temperature

IOCP vs

Temperature

Output Current Limit vs

Temperature for TPS16412 and TPS16413

Output Power Limit vs

Temperature for TPS16410 and TPS16411 with VIN = 12 V

TDLY vs Temperature

Output Power Limit vs

Temperature for TPS16410 and TPS16411 with VIN = 24 V

Thermal Shutdown Time vs Power Dissipation with VIN = 12

V

Thermal Shutdown Time vs Power Dissipation with VIN = 24

V

Specifications

Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315321/A_6534948C_E24A_405C_8CF7_C493A4C1CD37_TPS1641X_SF_UPLOAD_TABLE_1_ABSMAX_FOOTER1

MIN

MAX

UNIT

Vcc, FLT

Input Voltage

–0.3

67

V

OVP

Input Voltage

–0.3

62

V

IN, IN-OUT, IOCP

Input Voltage

–0.3

42

V

OUT

Input Voltage

–1

42

V

EN/SHDN, PDLY/IDLY

Input Voltage

–0.3

5.5

V

dVdT, PLIM/ILIM

Input Voltage

–0.3

5.5

V

IIOCP,IPDLY,IPLIM, IdVdT, IILIM

Source Current

Internally Limited

TJ

Junction temperature

–40

150

°C

Transient Junction Temperature

–40

TTSD

°C

Tstg

Storage temperature

–65

150

°C

Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315321/A_6534948C_E24A_405C_8CF7_C493A4C1CD37_TPS1641X_SF_UPLOAD_TABLE_1_ABSMAX_FOOTER1

MIN

MAX

UNIT

Vcc, FLT

Input Voltage

–0.3

67

V

OVP

Input Voltage

–0.3

62

V

IN, IN-OUT, IOCP

Input Voltage

–0.3

42

V

OUT

Input Voltage

–1

42

V

EN/SHDN, PDLY/IDLY

Input Voltage

–0.3

5.5

V

dVdT, PLIM/ILIM

Input Voltage

–0.3

5.5

V

IIOCP,IPDLY,IPLIM, IdVdT, IILIM

Source Current

Internally Limited

TJ

Junction temperature

–40

150

°C

Transient Junction Temperature

–40

TTSD

°C

Tstg

Storage temperature

–65

150

°C

Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

over operating free-air temperature range (unless otherwise noted)#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315321/A_6534948C_E24A_405C_8CF7_C493A4C1CD37_TPS1641X_SF_UPLOAD_TABLE_1_ABSMAX_FOOTER1

MIN

MAX

UNIT

Vcc, FLT

Input Voltage

–0.3

67

V

OVP

Input Voltage

–0.3

62

V

IN, IN-OUT, IOCP

Input Voltage

–0.3

42

V

OUT

Input Voltage

–1

42

V

EN/SHDN, PDLY/IDLY

Input Voltage

–0.3

5.5

V

dVdT, PLIM/ILIM

Input Voltage

–0.3

5.5

V

IIOCP,IPDLY,IPLIM, IdVdT, IILIM

Source Current

Internally Limited

TJ

Junction temperature

–40

150

°C

Transient Junction Temperature

–40

TTSD

°C

Tstg

Storage temperature

–65

150

°C

over operating free-air temperature range (unless otherwise noted)#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315321/A_6534948C_E24A_405C_8CF7_C493A4C1CD37_TPS1641X_SF_UPLOAD_TABLE_1_ABSMAX_FOOTER1

#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315321/A_6534948C_E24A_405C_8CF7_C493A4C1CD37_TPS1641X_SF_UPLOAD_TABLE_1_ABSMAX_FOOTER1

MIN

MAX

UNIT

Vcc, FLT

Input Voltage

–0.3

67

V

OVP

Input Voltage

–0.3

62

V

IN, IN-OUT, IOCP

Input Voltage

–0.3

42

V

OUT

Input Voltage

–1

42

V

EN/SHDN, PDLY/IDLY

Input Voltage

–0.3

5.5

V

dVdT, PLIM/ILIM

Input Voltage

–0.3

5.5

V

IIOCP,IPDLY,IPLIM, IdVdT, IILIM

Source Current

Internally Limited

TJ

Junction temperature

–40

150

°C

Transient Junction Temperature

–40

TTSD

°C

Tstg

Storage temperature

–65

150

°C

MIN

MAX

UNIT

MIN

MAX

UNIT

MINMAXUNIT

Vcc, FLT

Input Voltage

–0.3

67

V

OVP

Input Voltage

–0.3

62

V

IN, IN-OUT, IOCP

Input Voltage

–0.3

42

V

OUT

Input Voltage

–1

42

V

EN/SHDN, PDLY/IDLY

Input Voltage

–0.3

5.5

V

dVdT, PLIM/ILIM

Input Voltage

–0.3

5.5

V

IIOCP,IPDLY,IPLIM, IdVdT, IILIM

Source Current

Internally Limited

TJ

Junction temperature

–40

150

°C

Transient Junction Temperature

–40

TTSD

°C

Tstg

Storage temperature

–65

150

°C

Vcc, FLT

Input Voltage

–0.3

67

V

Vcc, FLT

ccFLTInput Voltage–0.367V

OVP

Input Voltage

–0.3

62

V

OVPInput Voltage–0.362V

IN, IN-OUT, IOCP

Input Voltage

–0.3

42

V

IN, IN-OUT, IOCPInput Voltage–0.342V

OUT

Input Voltage

–1

42

V

OUTInput Voltage–142V

EN/SHDN, PDLY/IDLY

Input Voltage

–0.3

5.5

V

EN/SHDN, PDLY/IDLYSHDNInput Voltage–0.35.5V

dVdT, PLIM/ILIM

Input Voltage

–0.3

5.5

V

dVdT, PLIM/ILIMInput Voltage–0.35.5V

IIOCP,IPDLY,IPLIM, IdVdT, IILIM

Source Current

Internally Limited

IIOCP,IPDLY,IPLIM, IdVdT, IILIM

IOCPPDLYPLIMdVdTILIMSource CurrentInternally Limited

TJ

Junction temperature

–40

150

°C

TJ

JJunction temperature–40150°C

Transient Junction Temperature

–40

TTSD

°C

Transient Junction Temperature–40TTSD

TSD°C

Tstg

Storage temperature

–65

150

°C

Tstg

stgStorage temperature–65150°C

Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

Operation outside the Absolute Maximum Ratings may cause permanent device damage. Absolute Maximum Ratings do not imply functional operation of the device at these or any other conditions beyond those listed under Recommended Operating Conditions. If used outside the Recommended Operating Conditions but within the Absolute Maximum Ratings, the device may not be fully functional, and this may affect device reliability, functionality, performance, and shorten the device lifetime.

ESD Ratings

VALUE

UNIT

V(ESD)

Electrostatic discharge

Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315322/A_6534948C_E24A_405C_8CF7_C493A4C1CD37_TPS1641X_SF_UPLOAD_TABLE_2_ESDRATINGS_COMMERCIAL_FOOTER1

±1500

V

Charged device model (CDM), per JEDEC specification JS-002, all pins#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315322/A_6534948C_E24A_405C_8CF7_C493A4C1CD37_TPS1641X_SF_UPLOAD_TABLE_2_ESDRATINGS_COMMERCIAL_FOOTER2

±500

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

ESD Ratings

VALUE

UNIT

V(ESD)

Electrostatic discharge

Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315322/A_6534948C_E24A_405C_8CF7_C493A4C1CD37_TPS1641X_SF_UPLOAD_TABLE_2_ESDRATINGS_COMMERCIAL_FOOTER1

±1500

V

Charged device model (CDM), per JEDEC specification JS-002, all pins#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315322/A_6534948C_E24A_405C_8CF7_C493A4C1CD37_TPS1641X_SF_UPLOAD_TABLE_2_ESDRATINGS_COMMERCIAL_FOOTER2

±500

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

VALUE

UNIT

V(ESD)

Electrostatic discharge

Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315322/A_6534948C_E24A_405C_8CF7_C493A4C1CD37_TPS1641X_SF_UPLOAD_TABLE_2_ESDRATINGS_COMMERCIAL_FOOTER1

±1500

V

Charged device model (CDM), per JEDEC specification JS-002, all pins#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315322/A_6534948C_E24A_405C_8CF7_C493A4C1CD37_TPS1641X_SF_UPLOAD_TABLE_2_ESDRATINGS_COMMERCIAL_FOOTER2

±500

VALUE

UNIT

V(ESD)

Electrostatic discharge

Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315322/A_6534948C_E24A_405C_8CF7_C493A4C1CD37_TPS1641X_SF_UPLOAD_TABLE_2_ESDRATINGS_COMMERCIAL_FOOTER1

±1500

V

Charged device model (CDM), per JEDEC specification JS-002, all pins#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315322/A_6534948C_E24A_405C_8CF7_C493A4C1CD37_TPS1641X_SF_UPLOAD_TABLE_2_ESDRATINGS_COMMERCIAL_FOOTER2

±500

VALUE

UNIT

VALUE

UNIT

VALUEUNIT

V(ESD)

Electrostatic discharge

Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315322/A_6534948C_E24A_405C_8CF7_C493A4C1CD37_TPS1641X_SF_UPLOAD_TABLE_2_ESDRATINGS_COMMERCIAL_FOOTER1

±1500

V

Charged device model (CDM), per JEDEC specification JS-002, all pins#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315322/A_6534948C_E24A_405C_8CF7_C493A4C1CD37_TPS1641X_SF_UPLOAD_TABLE_2_ESDRATINGS_COMMERCIAL_FOOTER2

±500

V(ESD)

Electrostatic discharge

Human body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315322/A_6534948C_E24A_405C_8CF7_C493A4C1CD37_TPS1641X_SF_UPLOAD_TABLE_2_ESDRATINGS_COMMERCIAL_FOOTER1

±1500

V

V(ESD)

(ESD)Electrostatic dischargeHuman body model (HBM), per ANSI/ESDA/JEDEC JS-001, all pins#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315322/A_6534948C_E24A_405C_8CF7_C493A4C1CD37_TPS1641X_SF_UPLOAD_TABLE_2_ESDRATINGS_COMMERCIAL_FOOTER1

#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315322/A_6534948C_E24A_405C_8CF7_C493A4C1CD37_TPS1641X_SF_UPLOAD_TABLE_2_ESDRATINGS_COMMERCIAL_FOOTER1±1500V

Charged device model (CDM), per JEDEC specification JS-002, all pins#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315322/A_6534948C_E24A_405C_8CF7_C493A4C1CD37_TPS1641X_SF_UPLOAD_TABLE_2_ESDRATINGS_COMMERCIAL_FOOTER2

±500

Charged device model (CDM), per JEDEC specification JS-002, all pins#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315322/A_6534948C_E24A_405C_8CF7_C493A4C1CD37_TPS1641X_SF_UPLOAD_TABLE_2_ESDRATINGS_COMMERCIAL_FOOTER2

#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315322/A_6534948C_E24A_405C_8CF7_C493A4C1CD37_TPS1641X_SF_UPLOAD_TABLE_2_ESDRATINGS_COMMERCIAL_FOOTER2±500

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

MIN

NOM

MAX

UNIT

Vcc

Supply voltage

VIN

60

V

FLT

Input Voltage

0

60

V

IN

Input Voltage (TPS16410, TPS16411, TPS16414, TPS16415)

4.5

40

V

IN

Input Voltage (TPS16412, TPS16413, TPS16416, TPS16417)

2.7

40

V

OUT

Input Voltage

0

40

V

EN/SHDN, OVP

Input Voltage

0

5.5

V

PDLY/IDLY

External capacitor

0.012

10

µF

dVdT

External capacitor

0.01

5

µF

IOCP

External resistor

6.34

80.6

kΩ

PLIM

External resistor

12.4

412

kΩ

ILIM

External resistor

5.1

348

kΩ

TJ

Junction temperature

–40

125

°C

Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

MIN

NOM

MAX

UNIT

Vcc

Supply voltage

VIN

60

V

FLT

Input Voltage

0

60

V

IN

Input Voltage (TPS16410, TPS16411, TPS16414, TPS16415)

4.5

40

V

IN

Input Voltage (TPS16412, TPS16413, TPS16416, TPS16417)

2.7

40

V

OUT

Input Voltage

0

40

V

EN/SHDN, OVP

Input Voltage

0

5.5

V

PDLY/IDLY

External capacitor

0.012

10

µF

dVdT

External capacitor

0.01

5

µF

IOCP

External resistor

6.34

80.6

kΩ

PLIM

External resistor

12.4

412

kΩ

ILIM

External resistor

5.1

348

kΩ

TJ

Junction temperature

–40

125

°C

over operating free-air temperature range (unless otherwise noted)

MIN

NOM

MAX

UNIT

Vcc

Supply voltage

VIN

60

V

FLT

Input Voltage

0

60

V

IN

Input Voltage (TPS16410, TPS16411, TPS16414, TPS16415)

4.5

40

V

IN

Input Voltage (TPS16412, TPS16413, TPS16416, TPS16417)

2.7

40

V

OUT

Input Voltage

0

40

V

EN/SHDN, OVP

Input Voltage

0

5.5

V

PDLY/IDLY

External capacitor

0.012

10

µF

dVdT

External capacitor

0.01

5

µF

IOCP

External resistor

6.34

80.6

kΩ

PLIM

External resistor

12.4

412

kΩ

ILIM

External resistor

5.1

348

kΩ

TJ

Junction temperature

–40

125

°C

over operating free-air temperature range (unless otherwise noted)

MIN

NOM

MAX

UNIT

Vcc

Supply voltage

VIN

60

V

FLT

Input Voltage

0

60

V

IN

Input Voltage (TPS16410, TPS16411, TPS16414, TPS16415)

4.5

40

V

IN

Input Voltage (TPS16412, TPS16413, TPS16416, TPS16417)

2.7

40

V

OUT

Input Voltage

0

40

V

EN/SHDN, OVP

Input Voltage

0

5.5

V

PDLY/IDLY

External capacitor

0.012

10

µF

dVdT

External capacitor

0.01

5

µF

IOCP

External resistor

6.34

80.6

kΩ

PLIM

External resistor

12.4

412

kΩ

ILIM

External resistor

5.1

348

kΩ

TJ

Junction temperature

–40

125

°C

MIN

NOM

MAX

UNIT

MIN

NOM

MAX

UNIT

MINNOMMAXUNIT

Vcc

Supply voltage

VIN

60

V

FLT

Input Voltage

0

60

V

IN

Input Voltage (TPS16410, TPS16411, TPS16414, TPS16415)

4.5

40

V

IN

Input Voltage (TPS16412, TPS16413, TPS16416, TPS16417)

2.7

40

V

OUT

Input Voltage

0

40

V

EN/SHDN, OVP

Input Voltage

0

5.5

V

PDLY/IDLY

External capacitor

0.012

10

µF

dVdT

External capacitor

0.01

5

µF

IOCP

External resistor

6.34

80.6

kΩ

PLIM

External resistor

12.4

412

kΩ

ILIM

External resistor

5.1

348

kΩ

TJ

Junction temperature

–40

125

°C

Vcc

Supply voltage

VIN

60

V

VccSupply voltageVIN

IN60V

FLT

Input Voltage

0

60

V

FLT

FLTInput Voltage060V

IN

Input Voltage (TPS16410, TPS16411, TPS16414, TPS16415)

4.5

40

V

INInput Voltage (TPS16410, TPS16411, TPS16414, TPS16415)4.540V

IN

Input Voltage (TPS16412, TPS16413, TPS16416, TPS16417)

2.7

40

V

INInput Voltage (TPS16412, TPS16413, TPS16416, TPS16417)2.740V

OUT

Input Voltage

0

40

V

OUTInput Voltage040V

EN/SHDN, OVP

Input Voltage

0

5.5

V

EN/SHDN, OVPSHDNInput Voltage05.5V

PDLY/IDLY

External capacitor

0.012

10

µF

PDLY/IDLYExternal capacitor0.01210µF

dVdT

External capacitor

0.01

5

µF

dVdTExternal capacitor0.015µF

IOCP

External resistor

6.34

80.6

kΩ

IOCPExternal resistor6.3480.6kΩ

PLIM

External resistor

12.4

412

kΩ

PLIMExternal resistor12.4412kΩ

ILIM

External resistor

5.1

348

kΩ

ILIMExternal resistor5.1348kΩ

TJ

Junction temperature

–40

125

°C

TJ

JJunction temperature–40125°C

Thermal Information

THERMAL METRIC#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315335/A_TPS2661X_SF_OTHER_TABLES_4_THERMAL_1PKG_FOOTER1

TPS1641

UNIT

DRC (VSON)

10 PINS

RθJA

Junction-to-ambient thermal resistance

43.7

°C/W

RθJC(top)

Junction-to-case (top) thermal resistance

50.0

°C/W

RθJB

Junction-to-board thermal resistance

15.8

°C/W

ΨJT

Junction-to-top characterization parameter

1.1

°C/W

ΨJB

Junction-to-board characterization parameter

15.8

°C/W

RθJC(bot)

Junction-to-case (bottom) thermal resistance

2.1

°C/W

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

Thermal Information

THERMAL METRIC#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315335/A_TPS2661X_SF_OTHER_TABLES_4_THERMAL_1PKG_FOOTER1

TPS1641

UNIT

DRC (VSON)

10 PINS

RθJA

Junction-to-ambient thermal resistance

43.7

°C/W

RθJC(top)

Junction-to-case (top) thermal resistance

50.0

°C/W

RθJB

Junction-to-board thermal resistance

15.8

°C/W

ΨJT

Junction-to-top characterization parameter

1.1

°C/W

ΨJB

Junction-to-board characterization parameter

15.8

°C/W

RθJC(bot)

Junction-to-case (bottom) thermal resistance

2.1

°C/W

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

THERMAL METRIC#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315335/A_TPS2661X_SF_OTHER_TABLES_4_THERMAL_1PKG_FOOTER1

TPS1641

UNIT

DRC (VSON)

10 PINS

RθJA

Junction-to-ambient thermal resistance

43.7

°C/W

RθJC(top)

Junction-to-case (top) thermal resistance

50.0

°C/W

RθJB

Junction-to-board thermal resistance

15.8

°C/W

ΨJT

Junction-to-top characterization parameter

1.1

°C/W

ΨJB

Junction-to-board characterization parameter

15.8

°C/W

RθJC(bot)

Junction-to-case (bottom) thermal resistance

2.1

°C/W

THERMAL METRIC#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315335/A_TPS2661X_SF_OTHER_TABLES_4_THERMAL_1PKG_FOOTER1

TPS1641

UNIT

DRC (VSON)

10 PINS

RθJA

Junction-to-ambient thermal resistance

43.7

°C/W

RθJC(top)

Junction-to-case (top) thermal resistance

50.0

°C/W

RθJB

Junction-to-board thermal resistance

15.8

°C/W

ΨJT

Junction-to-top characterization parameter

1.1

°C/W

ΨJB

Junction-to-board characterization parameter

15.8

°C/W

RθJC(bot)

Junction-to-case (bottom) thermal resistance

2.1

°C/W

THERMAL METRIC#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315335/A_TPS2661X_SF_OTHER_TABLES_4_THERMAL_1PKG_FOOTER1

TPS1641

UNIT

DRC (VSON)

10 PINS

THERMAL METRIC#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315335/A_TPS2661X_SF_OTHER_TABLES_4_THERMAL_1PKG_FOOTER1

TPS1641

UNIT

THERMAL METRIC#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315335/A_TPS2661X_SF_OTHER_TABLES_4_THERMAL_1PKG_FOOTER1

#GUID-XXXXXXXX-SF0T-XXXX-XXXX-000000315335/A_TPS2661X_SF_OTHER_TABLES_4_THERMAL_1PKG_FOOTER1TPS1641UNIT

DRC (VSON)

DRC (VSON)

10 PINS

10 PINS

RθJA

Junction-to-ambient thermal resistance

43.7

°C/W

RθJC(top)

Junction-to-case (top) thermal resistance

50.0

°C/W

RθJB

Junction-to-board thermal resistance

15.8

°C/W

ΨJT

Junction-to-top characterization parameter

1.1

°C/W

ΨJB

Junction-to-board characterization parameter

15.8

°C/W

RθJC(bot)

Junction-to-case (bottom) thermal resistance

2.1

°C/W

RθJA

Junction-to-ambient thermal resistance

43.7

°C/W

RθJA

θJA Junction-to-ambient thermal resistance43.7°C/W

RθJC(top)

Junction-to-case (top) thermal resistance

50.0

°C/W

RθJC(top)

θJC(top)Junction-to-case (top) thermal resistance50.0°C/W

RθJB

Junction-to-board thermal resistance

15.8

°C/W

RθJB

θJBJunction-to-board thermal resistance15.8°C/W

ΨJT

Junction-to-top characterization parameter

1.1

°C/W

ΨJT

JTJunction-to-top characterization parameter1.1°C/W

ΨJB

Junction-to-board characterization parameter

15.8

°C/W

ΨJB

JBJunction-to-board characterization parameter15.8°C/W

RθJC(bot)

Junction-to-case (bottom) thermal resistance

2.1

°C/W

RθJC(bot)

θJC(bot)Junction-to-case (bottom) thermal resistance2.1°C/W

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.Semiconductor and IC Package Thermal Metrics

Electrical Characteristics

–40°C ≤ TA = TJ ≤ +125°C, VIN = 3 V to 40 V (TPS16412, TPS16413, TPS16416, TPS16417), VIN = 4.5 V to 40 V (TPS16410, TPS16411, TPS16414, TPS16415), Vcc = VIN, RILIM = 5.49 kΩ RPLIM = 255 kΩ RIOCP = 7.32 kΩ , FLT = Open, COUT = 100 nF, CIN = 10 nF CdVdT = Open, PDLY/IDLY = Open. , EN/SHDN = Open(Allvoltages referenced to GND, (unless otherwise noted))

PARAMETER

TEST CONDITIONS

MIN

TYP

MAX

UNIT

OPERATING INPUT AND SUPPLY VOLTAGE

Vcc

Operating Supply voltage

VIN

60

V

VIN

Operating Input voltage

TPS16410, TPS16411, TPS16414 ,TPS16415

4.5

40

V

VIN

Operating Input voltage

TPS16412, TPS16413, TPS16416, TPS16417

2.7

40

V

IQ

Operting Supply curent (Vcc)

EN/SHDN = 2 V, Vcc = 40 V, VIN = Open, RILIM or RPLIM = Open

1.2

2.1

mA

IQSD

Shutdown Supply current (Vcc)

EN/SHDN = GND, Vcc = 40 V, VIN = Open, RILIM or RPLIM = Open, RIOCP = Open

14

36

µA

IINLKG

IN Leakage Current in ON State

EN/SHDN = 2 V, VIN = Vcc = 40 V, Open, RILIM or RPLIM = Open

0.025

0.52

mA

IINLKG-SD

IN Leakage Current in Shutdown

EN/SHDN = GND,VIN = Vcc = 40 V, RILIM or RPLIM = Open, RIOCP = Open

0.7

2.8

µA

OVER-VOLTAGE PROTECTION (OVP) INPUT

VOVPR

OVP rising threshold

1.48

1.53

1.58

V

VOVPF

OVP falling threshold

1.34

1.40

1.46

V

IOVP

OVP leakage current

0 V ≤ VOVP ≤ 4 V

–350

–265

–200

nA

EN/SHDN INPUT

VENR

Enable rising threshold

1.2

V

VENF

Enable falling threshold

0.59

V

IEN

Enable leakage current

0 V ≤ VEN ≤ 4 V

–10

µA

VEN-Open

Open circuit Enable Voltage

IEN = 0.1 µA, VCC ≥ 5 V

4.9

V

OUTPUT POWER LIMITING (PLIM)

POUT

Output Power Limit

RPLIM = 26.7 kΩ

3

3.66

4.5

W

POUT

Output Power Limit

RPLIM = 95.3 kΩ, –40°C ≤ TA ≤ +85°C

12.94

13.69

14.44

W

POUT

Output Power Limit

RPLIM = 255 kΩ, –40°C ≤ TA ≤ +85°C

34

37

39.8

W

OUTPUT CURRENT LIMITING (ILIM)

IOUT

Output Current Limit

RILIM = 332 kΩ

0.024

0.032

0.039

A

IOUT

Output Current Limit

RILIM = 10 kΩ, –40°C ≤ TA ≤ +85°C

0.918

0.987

1.035

A

IOUT

Output Current Limit

RILIM = 5.49 kΩ, –40°C ≤ TA ≤ +85°C

1.671

1.77

1.881

A

POWER OUTPUT (OUT)

RON

IN to OUT On resistance

–40°C ≤ TJ ≤ 125°C

96

153

260

mΩ

RON

IN to OUT On resistance

0°C ≤ TJ ≤ 85°C

153

215

mΩ

RON

IN to OUT On resistance

TJ = 25°C

153

160

mΩ

ILKG-OUT

Output Leakage current in OFF state

VIN = 40 V, VOUT = 0 V, EN = Low

–15

–1.2

µA