ZHCSIV1F September 2018 – February 2023 TPS1663

PRODUCTION DATA

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 Device Comparison Table

- 6 Pin Configuration and Functions

- 7 Specifications

- 8 Parameter Measurement Information

-

9 Detailed Description

- 9.1 Overview

- 9.2 Functional Block Diagram

- 9.3

Feature Description

- 9.3.1 Hot Plug-In and In-Rush Current Control

- 9.3.2 Undervoltage Lockout (UVLO)

- 9.3.3 Overvoltage Protection (OVP)

- 9.3.4 Overload and Short Circuit Protection

- 9.3.5 Output Power Limiting, PLIM (TPS16632 Only)

- 9.3.6 Current Monitoring Output (IMON)

- 9.3.7 FAULT Response (FLT)

- 9.3.8 Power Good Output (PGOOD)

- 9.3.9 IN, P_IN, OUT and GND Pins

- 9.3.10 Thermal Shutdown

- 9.3.11 Low Current Shutdown Control (SHDN)

- 9.4 Device Functional Modes

- 10Application and Implementation

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

9.3.5 Output Power Limiting, PLIM (TPS16632 Only)

In TPS16630, with a fixed overcurrent limit threshold the maximum output power limit increases linearly with supply input. Electrical Industrial process control equipment such as PLC CPU must comply with standards like IEC61010-1 and UL1310 for fire safety which require limited energy and power circuits. Limiting the output power becomes a challenge in such high power applications where the operating supply voltage range is wide. The TPS16632 integrate adjustable output power limiting functionality that simplifies the system design requiring compliance in accordance to this standard.

Connect a resistor from PLIM to GND as shown in Figure 9-10 to set the output power limiting value. If output power limiting is not required, then connect PLIM to GND directly. This connection disables the PLIM functionality.

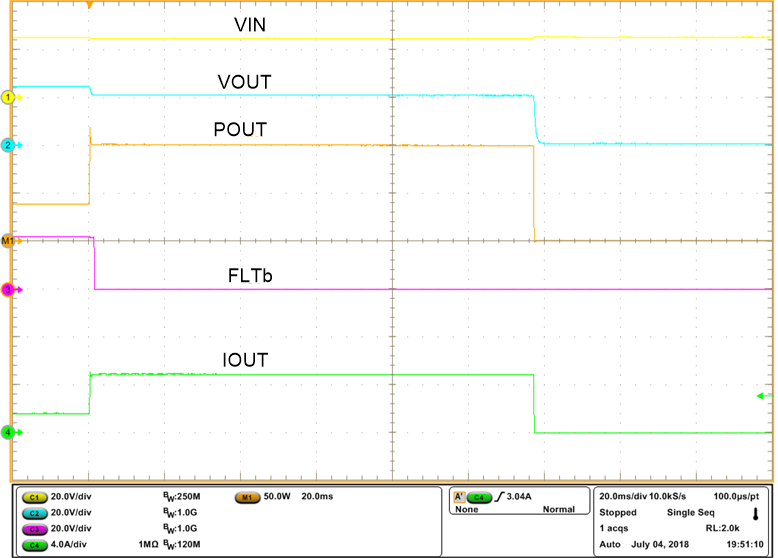

During an over-power load event, the TPS16632 limits the output power at the programmed value set by PLIM resistor. This limit indirectly results in the device operation in current limiting mode with steady state output voltage and current set by the load characteristics and PLIM = VOUT × IOUT. Figure 7-8 shows the output power limit and current limit characteristics of TPS16632 with 100-W power limit setting. The maximum duration for the device in power limiting mode is 162 msec (typical), tCL_PLIM(dly). After this time, the device operates either in auto-retry or latch off mode based on MODE pin configuration in Table 9-1.

Here, P(PLIM) is output power limit in watts, and R(PLIM) is the power limit setting resistor in kΩ.

During the output power limiting operation, FLT asserts after a delay of tCL_PLIM_FLT(dly). The FLT signal remains asserted until the over power load condition is removed and the device resumes normal operation.

Figure 9-11 illustrates output power limiting performance of TPS16632 with 100-W setting for class-2 power supply designs . Figure 9-10 TPS16632 Typical Application Schematic

Figure 9-10 TPS16632 Typical Application Schematic

| RPLIM = 100 kΩ | RILIM = 3 kΩ |