ZHCSNX8B December 2020 – September 2023 TPS6593-Q1

PRODUCTION DATA

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 说明(续)

- 6 Pin Configuration and Functions

-

7 Specifications

- 7.1 Absolute Maximum Ratings

- 7.2 ESD Ratings

- 7.3 Recommended Operating Conditions

- 7.4 Thermal Information

- 7.5 General Purpose Low Drop-Out Regulators (LDO1, LDO2, LDO3)

- 7.6 Low Noise Low Drop-Out Regulator (LDO4)

- 7.7 Internal Low Drop-Out Regulators (LDOVRTC, LDOVINT)

- 7.8 BUCK1, BUCK2, BUCK3, BUCK4 and BUCK5 Regulators

- 7.9 Reference Generator (BandGap)

- 7.10 Monitoring Functions

- 7.11 Clocks, Oscillators, and PLL

- 7.12 Thermal Monitoring and Shutdown

- 7.13 System Control Thresholds

- 7.14 Current Consumption

- 7.15 Backup Battery Charger

- 7.16 Digital Input Signal Parameters

- 7.17 Digital Output Signal Parameters

- 7.18 I/O Pullup and Pulldown Resistance

- 7.19 I2C Interface

- 7.20 Serial Peripheral Interface (SPI)

- 7.21 Typical Characteristics

-

8 Detailed Description

- 8.1 Overview

- 8.2 Functional Block Diagram

- 8.3

Feature Description

- 8.3.1 System Supply Voltage Monitor

- 8.3.2

Power Resources (Bucks and LDOs)

- 8.3.2.1

Buck Regulators

- 8.3.2.1.1 BUCK Regulator Overview

- 8.3.2.1.2 Multi-Phase Operation and Phase-Adding or Shedding

- 8.3.2.1.3 Transition Between PWM and PFM Modes

- 8.3.2.1.4 Multi-Phase BUCK Regulator Configurations

- 8.3.2.1.5 Spread-Spectrum Mode

- 8.3.2.1.6 Adaptive Voltage Scaling (AVS) and Dynamic Voltage Scaling (DVS) Support

- 8.3.2.1.7 BUCK Output Voltage Setting

- 8.3.2.1.8 BUCK Regulator Current Limit

- 8.3.2.1.9 SW_Bx Short-to-Ground Detection

- 8.3.2.1.10 Sync Clock Functionality

- 49

- 8.3.2.2 Low Dropout Regulators (LDOs)

- 8.3.2.1

Buck Regulators

- 8.3.3 Output Voltage Monitor and PGOOD Generation

- 8.3.4 Thermal Monitoring

- 8.3.5 Backup Supply Power-Path

- 8.3.6 General-Purpose I/Os (GPIO Pins)

- 8.3.7 nINT, EN_DRV, and nRSTOUT Pins

- 8.3.8 Interrupts

- 8.3.9 RTC

- 8.3.10

Watchdog (WDOG)

- 8.3.10.1 Watchdog Fail Counter and Status

- 8.3.10.2 Watchdog Start-Up and Configuration

- 8.3.10.3 MCU to Watchdog Synchronization

- 8.3.10.4 Watchdog Disable Function

- 8.3.10.5 Watchdog Sequence

- 8.3.10.6 Watchdog Trigger Mode

- 8.3.10.7 WatchDog Flow Chart and Timing Diagrams in Trigger Mode

- 79

- 8.3.10.8 Watchdog Question-Answer Mode

- 8.3.11 Error Signal Monitor (ESM)

- 8.4

Device Functional Modes

- 8.4.1

Device State Machine

- 8.4.1.1 Fixed Device Power FSM

- 8.4.1.2

Pre-Configurable Mission States

- 8.4.1.2.1

PFSM Commands

- 8.4.1.2.1.1 REG_WRITE_IMM Command

- 8.4.1.2.1.2 REG_WRITE_MASK_IMM Command

- 8.4.1.2.1.3 REG_WRITE_MASK_PAGE0_IMM Command

- 8.4.1.2.1.4 REG_WRITE_BIT_PAGE0_IMM Command

- 8.4.1.2.1.5 REG_WRITE_WIN_PAGE0_IMM Command

- 8.4.1.2.1.6 REG_WRITE_VOUT_IMM Command

- 8.4.1.2.1.7 REG_WRITE_VCTRL_IMM Command

- 8.4.1.2.1.8 REG_WRITE_MASK_SREG Command

- 8.4.1.2.1.9 SREG_READ_REG Command

- 8.4.1.2.1.10 SREG_WRITE_IMM Command

- 8.4.1.2.1.11 WAIT Command

- 8.4.1.2.1.12 DELAY_IMM Command

- 8.4.1.2.1.13 DELAY_SREG Command

- 8.4.1.2.1.14 TRIG_SET Command

- 8.4.1.2.1.15 TRIG_MASK Command

- 8.4.1.2.1.16 END Command

- 8.4.1.2.2 Configuration Memory Organization and Sequence Execution

- 8.4.1.2.3 Mission State Configuration

- 8.4.1.2.4 Pre-Configured Hardware Transitions

- 8.4.1.2.1

PFSM Commands

- 8.4.1.3 Error Handling Operations

- 8.4.1.4 Device Start-up Timing

- 8.4.1.5 Power Sequences

- 8.4.1.6 First Supply Detection

- 8.4.1.7 Register Power Domains and Reset Levels

- 8.4.2 Multi-PMIC Synchronization

- 8.4.1

Device State Machine

- 8.5 Control Interfaces

- 8.6 Configurable Registers

- 8.7 Register Maps

- 9 Application and Implementation

- 10Device and Documentation Support

- 11Mechanical, Packaging, and Orderable Information

9.4.1 Layout Guidelines

The high frequency and large switching currents of the TPS6593-Q1 device make the choice of layout important. Good power supply results only occur when care is given to correct design and layout. Layout affects noise pickup and generation and can cause a good design to perform with less-than-expected results.

With a range of buck output currents from a few milliampere to 10 A and over, good power supply layout is much more difficult than most general PCB design. Use the following steps as a reference to ensure the buck regulators are stable and maintain correct voltage and current regulation across its intended operating voltage and current range.

- Place CIN as close as possible to the PVIN_Bx pin and the PGND/Thermal Pad. Route the VIN trace wide and thick to avoid IR drops. The DCR of the trace from the source to the pin must be less than 2 mΩ. The trace between the positive node of the input capacitor and the PVIN_Bx pins of the device, as well as the trace between the negative node of the input capacitor and PGND/Thermal Pad, must be kept as short as possible. The input capacitance provides a low-impedance voltage source for the switching converter. The inductance of the connection is the most important parameter of a local decoupling capacitor — parasitic inductance on these traces must be kept as small as possible for correct device operation. The parasitic inductance can be reduced by using a ground plane as close as possible to top layer by using thin dielectric layer between top layer and ground plane.

- The output filter, consisting of COUT and L, converts the switching signal at SW_Bx to the noiseless output voltage. This output filter must be placed as close as possible to the device keeping the switch node small, for best EMI behavior. Note that the PVIN_Bx pin is directly adjacent to the SW_Bx pin. The inductor and capacitor placement must be made as close as possible without compromising PVIN_Bx. Route the traces between the output capacitors of the device and the load direct and wide to avoid losses due to the IR drop.

- Input for analog blocks (VCCA and REFGND1/2) must be isolated from noisy signals. Connect VCCA directly to a quiet system voltage node and REFGND1/2 to a quiet ground point where no IR drop occurs. Place the decoupling capacitor as close as possible to the VCCA pin.

- If the processor load supports remote voltage sensing, connect the feedback pins FB_Bx of the device to the respective sense pins on the processor. If the processor does not support remote voltage sensing, then connect the FB_Bx pin to a representative load capacitor. With differential feedback, also connect the negative feedback pin to the negative terminal of the same load capacitor. The minimum recommended trace width is 6 mils. The sense lines are susceptible to noise. They must be kept away from noisy signals such as PGND, PVIN_Bx, and SW_Bx, as well as high bandwidth signals such as the I2C. Avoid capacitive and inductive coupling by keeping the sense lines short, direct, and close to each other. Run the lines in a quiet layer. Isolate them from noisy signals by a voltage or ground plane if possible. Running the signal as a differential pair is recommended. If series resistors are used for load current measurement, place them after connection of the voltage feedback.

- PGND, PVIN_Bx and SW_Bx must be routed on thick layers. They must not surround inner signal layers, which are not able to withstand interference from noisy PGND, PVIN_Bx and SW_Bx.

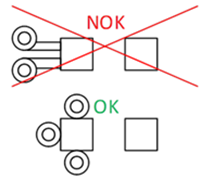

For the LDO regulators, the feedback connection is internal. Therefore, it is important to keep the PCB resistance between LDO output and target load in the range of the acceptable voltage drop for LDOs. Similar to the buck regulators, the input capacitor at the PVIN_LDOx pins and the VCCA pin must be placed as close as possible to the PMIC. The impedance from the source of the PVIN_LDOx pins and the VCCA pin must be low and the DCR less than 2 mΩ. The output capacitor at the VOUT_LDOx, VOUT_LDOVINT and VOUT_LDOVRTC pins must be as close (0.5mm) to the PMIC as possible. The ground connection of these capacitors, especially for the capacitor at the VOUT_LDOVINT pin, must have a low impedance of less than 2 mΩ to the ground (Thermal Pad) of the TPS6593-Q1. For the ground connection of this capacitor at the VOUT_LDOVINT pin, use multiple vias (at least three) directly at the ground landing pad of the capacitor. See illustration below:

Figure 9-69 Ground connection of capacitor at VOUT_LDOVINT pin

Figure 9-69 Ground connection of capacitor at VOUT_LDOVINT pinDue to the overall small solution size, the thermal performance of the PCB layout is important. Many system-dependent parameters, such as thermal coupling, airflow, added heat sinks and convection surfaces, and the presence of other heat-generating components affect the power dissipation limits of a given component. Proper PCB layout, focusing on thermal performance, results in lower die temperatures. Wide and thick power traces come with the ability to sink dissipated heat. The capability to sink dissipated heat can be improved further on multi-layer PCB designs with vias to different planes. Improved heat-sinking capability results in reduced junction-to-ambient (RθJA) and junction-to-board (RθJB) thermal resistances and thereby reduces the device junction temperature, TJ. TI strongly recommends to perform a careful system-level 2D or full 3D dynamic thermal analysis at the beginning product design process, by using a thermal modeling analysis software.

Overall recommendation for the PCB is to use at least 12 layers with 60 to 90 mil thickness, and with following weights for the Copper layers:

- 0.5oz for signal layers

- at least 1.5oz for top layer and other plane layers

A more complete list of layout recommendations can be found in the Schematic and layout checklist.