ZHCSN49N January 2007 – June 2024

PRODUCTION DATA

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 Pin Configuration and Functions

- 5 Specifications

- 6 Detailed Description

- 7 Application and Implementation

- 8 Device and Documentation Support

- 9 Revision History

- 10Mechanical, Packaging, and Orderable Information

封装选项

机械数据 (封装 | 引脚)

散热焊盘机械数据 (封装 | 引脚)

订购信息

3 说明

TPS748 低压降 (LDO) 线性稳压器可面向多种应用提供易于使用的稳健型电源管理解决方案。用户可编程软启动通过减少启动时的电容涌入电流,最大限度地减少了输入电源上的应力。软启动具有单调性,旨在为各类处理器和 ASIC 供电。借助使能输入和电源正常输出,可通过外部稳压器轻松实现上电排序。凭借全方位的灵活性,该器件可为 FPGA、DSP 等具有特殊启动要求的应用配置可满足其时序要求的解决方案。

具有精密基准的误差放大器可在整个负载、线路、温度和过程范围内提供 1% 精度(新芯片)。该器件在使用大于或等于 2.2μF 的任何类型的电容器时都能保持稳定运行,并具有 TJ = –40°C 至 +125°C 的额定结温范围。TPS748 采用小型 3mm × 3mm VSON-10 封装,可实现高度紧凑的解决方案总尺寸。该器件还可采用 5mm × 5mm VQFN-20 封装,从而与 TPS742 兼容。

(1) 如需更多信息,请参阅机械、封装和可订购信息。

(2) 封装尺寸(长 × 宽)为标称值,并包括引脚(如适用)。

典型应用电路(可调节)

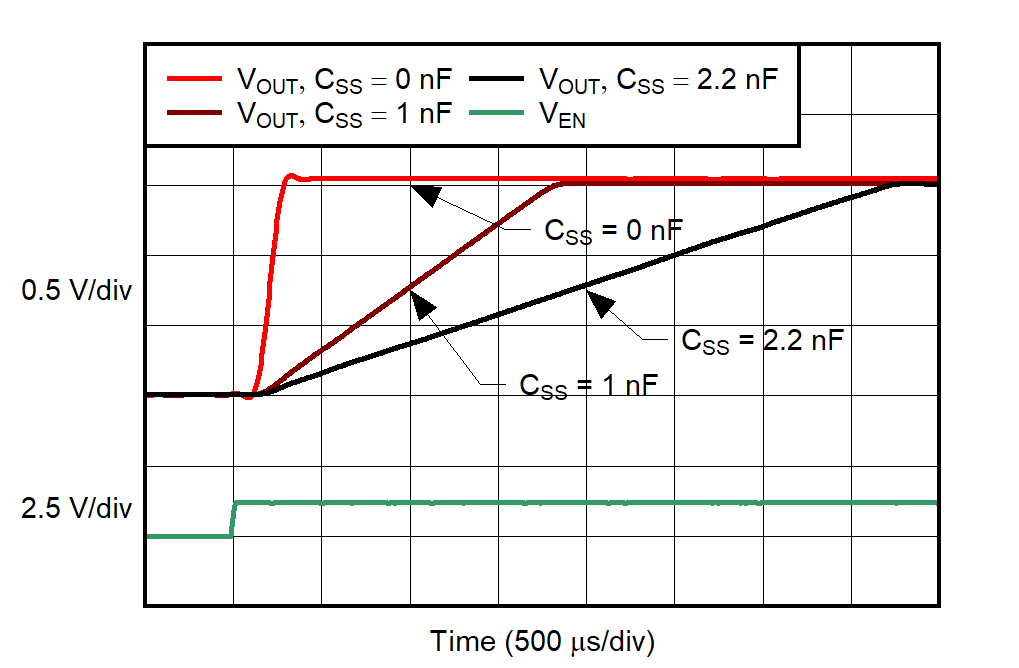

典型应用电路(可调节) 导通响应

导通响应