ZHCSN32B June 2019 – July 2024 TPS99001-Q1

PRODUCTION DATA

- 1

- 1 特性

- 2 应用

- 3 说明

- 4 Pin Configuration and Functions

-

5 Specifications

- 5.1 Absolute Maximum Ratings

- 5.2 ESD Ratings

- 5.3 Recommended Operating Conditions

- 5.4 Thermal Information

- 5.5 Electrical Characteristics—Analog to Digital Converter

- 5.6 Electrical Characteristics—Voltage Regulators

- 5.7 Electrical Characteristics—Temperature and Voltage Monitors

- 5.8 Electrical Characteristics—Current Consumption

- 5.9 Power-Up Timing Requirements

- 5.10 Power-Down Timing Requirements

- 5.11 Timing Requirements—Sequencer Clock

- 5.12 Timing Requirements—Host and Diagnostic Port SPI Interface

- 5.13 Timing Requirements—ADC Interface

- 5.14 Switching Characteristics

-

6 Detailed Description

- 6.1 Overview

- 6.2 Functional Block Diagram

- 6.3 Feature Description

- 6.4 Device Functional Modes

- 6.5 Register Maps

- 7 Application and Implementation

- 8 Power Supply Recommendations

- 9 Layout

- 10Device and Documentation Support

- 11Revision History

- 12Mechanical, Packaging, and Orderable Information

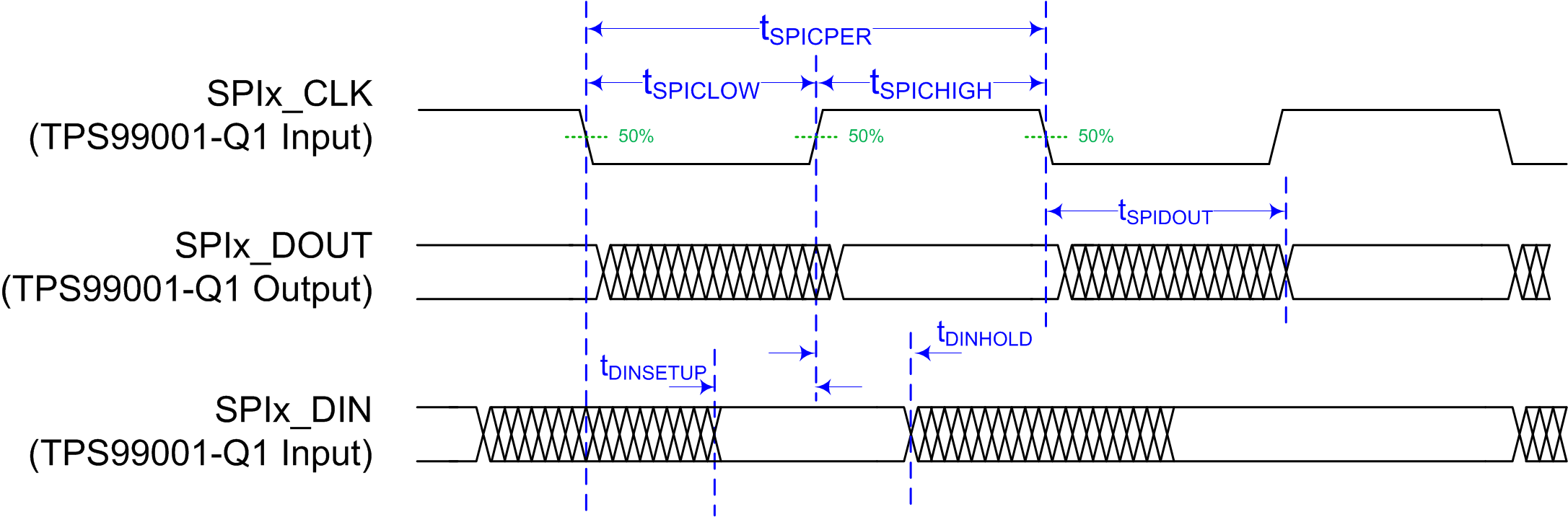

5.12 Timing Requirements—Host and Diagnostic Port SPI Interface

| MIN | NOM | MAX | UNIT | ||

|---|---|---|---|---|---|

| tSPICPER | SPI CLK Cycle Time | 31 | 33 | ns | |

| tSPICHIGH | SPI CLK High Time | 10 | ns | ||

| tSPICLOW | SPI CLK Low Time | 10 | ns | ||

| tSPIDOUT | CLK Falling to DOUT | 0 | 15 | ns | |

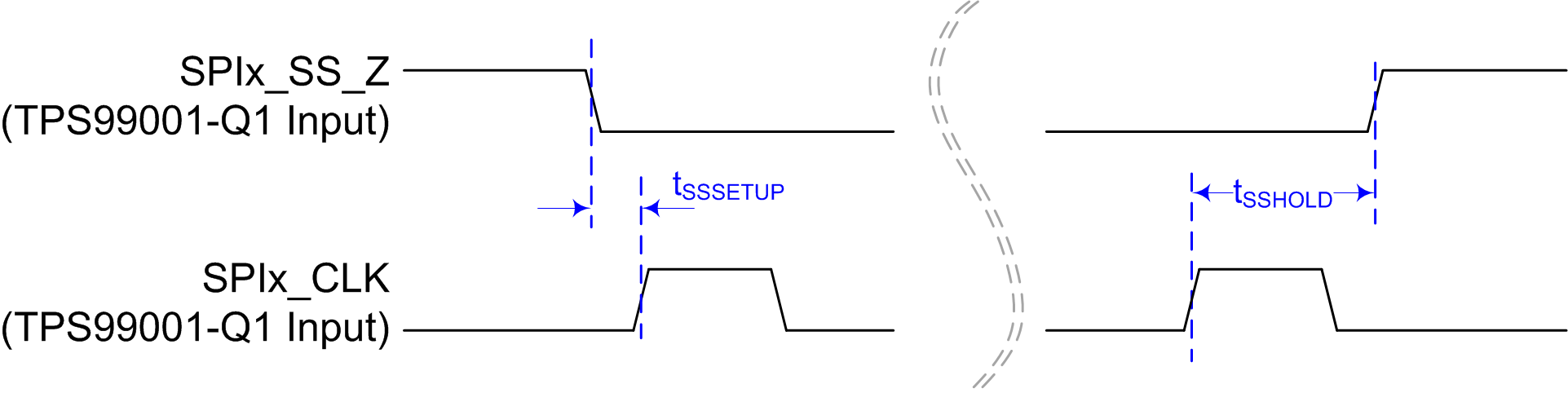

| tSSSETUP | SPI SS_Z to CLK Rising Setup Time | 5 | ns | ||

| tSSHOLD | SPI CLK Rising to SS_Z Hold Time | 5 | ns | ||

| tDINSETUP | SPI DIN to CLK Rising Setup Time | 5 | ns | ||

| tDINHOLD | SPI CLK Rising to DIN Hold Time | 5 | ns | ||

Figure 5-4 DLPC23x-Q1 Diagnostic Interface Timing

Figure 5-4 DLPC23x-Q1 Diagnostic Interface Timing Figure 5-5 Chip Select Setup and Hold

Timing

Figure 5-5 Chip Select Setup and Hold

Timing