ZHCS429J March 2012 – November 2021 UCD3138

PRODUCTION DATA

- 1 特性

- 2 应用范围

- 3 说明

- 4 功能方框图

- 5 Revision History

- 6 Device Comparison Table

- 7 Pin Configuration and Functions

- 8 Specifications

-

9 Detailed Description

- 9.1 Overview

- 9.2 ARM Processor

- 9.3 Memory

- 9.4 System Module

- 9.5

Feature Description

- 9.5.1 Sync FET Ramp and IDE Calculation

- 9.5.2 Automatic Mode Switching

- 9.5.3 DPWMC, Edge Generation, IntraMux

- 9.5.4 Filter

- 9.5.5 Communication Ports

- 9.5.6 Miscellaneous Analog

- 9.5.7 Package ID Information

- 9.5.8 Brownout

- 9.5.9 Global I/O

- 9.5.10 Temperature Sensor Control

- 9.5.11 I/O Mux Control

- 9.5.12 Current Sharing Control

- 9.5.13 Temperature Reference

- 9.6 Device Functional Modes

-

10Application and Implementation

- 10.1 Application Information

- 10.2

Typical Application

- 10.2.1 Design Requirements

- 10.2.2 Detailed Design Procedure

- 10.2.3 Application Curves

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical Packaging and Orderable Information

封装选项

机械数据 (封装 | 引脚)

散热焊盘机械数据 (封装 | 引脚)

订购信息

12.1.1 EMI and EMC Mitigation Guidelines

Every design is different in terms of EMI and EMC mitigation, and all designs require their own solution.

- Apply multiple different capacitors for different frequency range on decoupling circuits. Each capacitor has different ESL, capacitance and ESR, and different frequency responses.

- Avoid long traces close to radiation sources, and place them into an internal layer. It is preferred to have ground shielding and add a termination circuit at the end of the trace.

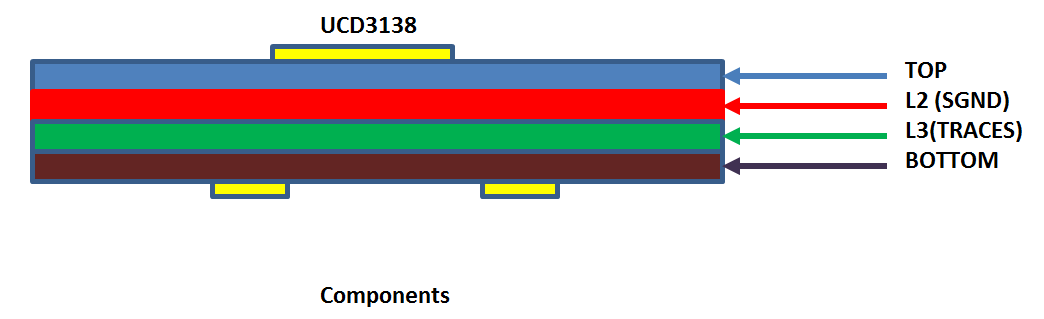

- TI recommends single ground: SGND. A multilayer such as 4

layers board is recommended so that one solid SGND is dedicated for return

current path.

- Use one whole layer (L2) for SGND plane as shown in

Figure 12-1. Use many vias (such as 9 vias) to connect the

extended power pad to the internal SGND plane layer. It is preferred to

have the vias close to AGND pins and DGND pins of the device.

Figure 12-1 Optional

Ground Layer Assignment

Figure 12-1 Optional

Ground Layer Assignment

- Use one whole layer (L2) for SGND plane as shown in

Figure 12-1. Use many vias (such as 9 vias) to connect the

extended power pad to the internal SGND plane layer. It is preferred to

have the vias close to AGND pins and DGND pins of the device.

- Add LPF on analog signals close to the header connecting the control card and the power board.

- Do not use a ferrite bead to connect V33A and V33D instead of using 1-Ω resistor.

- Avoid negative current and negative voltage on all pins. Schottky diodes may be needed to clamp the voltage; avoid the voltage spike on all pins to exceed 3.8 V or below –0.3 V; add Schottky diodes on the pins which could have voltage spikes during surge test; be aware that Schottky diode has relatively higher leakage current, which can affect the voltage sensing at high temperatures. The need for external Schottky diodes is conditional. For example, the DPWM pins only need external Schottky diodes when there is a long distance, for example, more than 3 inches, between the control card and main power stage because in this case, the trace can pick up noise and cause electrical overstress on the device pins. The same is true for GPIO and PMBus pins.

- The auxiliary supply is normally a flyback converter, and its power transformer can generate a large electromagnetic field which can interfere with other electronic circuitry. By shielding the primary side windings, the EMI can be effectively reduced so that the surrounding circuits can have a quieter working environment.