ZHCSOV0E March 2005 – November 2021 UCD7100

PRODUCTION DATA

- 1 特性

- 2 应用

- 3 说明

- 4 Revision History

- 5 说明(续)

- 6 Device Comparison Table

- 7 Pin Configuration and Functions

- 8 Specifications

- 9 Detailed Description

- 10Application and Implementation

- 11Power Supply Recommendations

- 12Layout

- 13Device and Documentation Support

- 14Mechanical, Packaging, and Orderable Information

封装选项

请参考 PDF 数据表获取器件具体的封装图。

机械数据 (封装 | 引脚)

- PWP|14

散热焊盘机械数据 (封装 | 引脚)

- PWP|14

订购信息

10.2.2 Detailed Design Procedure

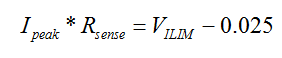

The cycle-by-cycle current protection is implemented by connecting the current sense signal to the CS pin. When the CS level is greater than the ILIM voltage minus 25 mV, the output of the driver is forced low and the current limit flag (CLF) is set high. The CLF signal is latched high until the UCD7K device receives the next rising edge on the IN pin.

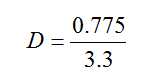

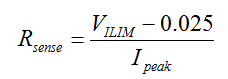

The current limit threshold can be set to any value between 0.25 V and 1.0 V, so Rsense must be between 0.045 Ω and 0.195 Ω. For example, if Rsense is 0.15 Ω, then VILIM must be 0.775 V to protect input current at 5 A. If the digital controller has an internal digital-to-analog converter, then it can generate 0.775 V and connect to ILIM directly. For a digital controller without an internal digital-to-analog converter, it can generate a PWM signal, send the PWM signal through a low pass filter, then connect to the ILIM pin. Assuming the magnitude of the PWM pulse is 3.3 V, then the duty cycle is: