GERA024 December 2022 AMC1202 , AMC1302 , AMC1306M05 , AMC22C11 , AMC22C12 , AMC23C10 , AMC23C11 , AMC23C12 , AMC23C14 , AMC23C15 , AMC3302 , AMC3306M05

- 1

- Kurzfassung

- Marken

- 1Einführung

-

2Strommessung in AC/DC-Wandlern

- 2.1 Grundlegende Hardware und Steuerungsbeschreibung von AC/DC

- 2.2 Punkt A und B – AC/DC AC-Phasenstrommessung

- 2.3 Punkt C und D – AC/DC DC-Link-Strommessung

- 2.4 Zusammenfassung der positiven und negativen Punkte an den Punkten A, B, C1/2 und D1/2 sowie Produktvorschläge

- 3Strommessung in DC/DC-Wandlern

- 4Fazit

- 5Quellennachweise

3.3 Punkt G – DC/DC-Tankstrommessung

In diesem Abschnitt werden die Strommessanforderungen am Schalttank – Punkt G beschrieben. In einem resonanten bidirektionalen isolierten CLLLC-DC/DC-Wandler ist eine Nulldurchgangserkennung (ZCD) für die synchrone Gleichrichtung erforderlich, die dazu beiträgt, den Leitungsverlust zu reduzieren und die Systemeffizienz zu verbessern.

Abbildung 3-6 Strommessung am primären oder sekundären Tank eines isolierten DC/DC-Wandlers

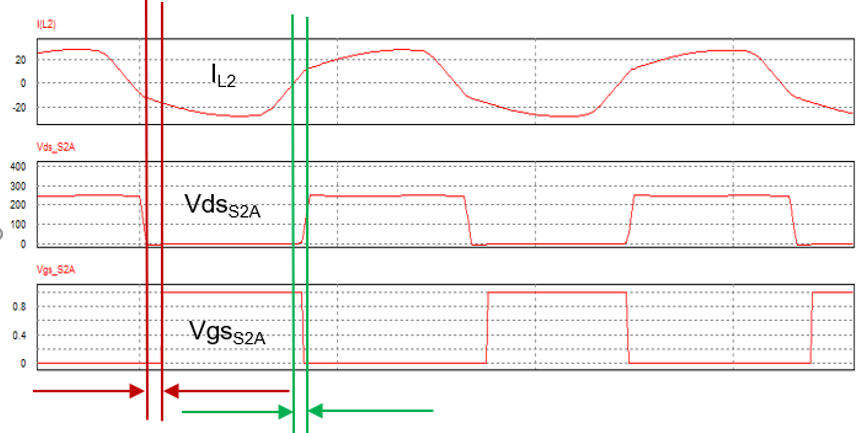

Abbildung 3-6 Strommessung am primären oder sekundären Tank eines isolierten DC/DC-WandlersIn Abbildung 3-6zeigen die zwei grünen Cursorlinien die Ausbreitungsverzögerung zwischen Nulldurchgang und sekundärseitiger FET-Einschaltung an.

Abbildung 3-7 Ausbreitungsverzögerung der Nulldurchgangserkennung

Abbildung 3-7 Ausbreitungsverzögerung der NulldurchgangserkennungEine hochmoderne Implementierung des ZCD-Schaltkreises in CLLLC-Topologie besteht darin, einen Stromwandler (CT) oder eine Rogowski-Spule an der Primär- und Sekundärseite in Reihe mit dem Resonanzkondensator zu schalten. Typische Ausbreitungsverzögerungen des CT- oder Rogowski-Spulenansatzes liegen zwischen 100 ns und 200 ns. Diese Verzögerung kann zu erheblichen Verlusten in einer CLLLC-Topologie führen, die sich negativ auf den Gesamtwirkungsgrad des DC/DC-Wandlers auswirken. Bei einem Spitzenstrom von ca. 30 A, einer Resonatschaltfrequenz von 500 kHz und einer Einschaltverzögerung von 100 ns führt die Body-Diode (bei einer Durchlassspannung von 4,5 V) 9,3 A, bis der FET eingeschaltet wird, was zu einem Energieverlust in der Spitze von ca. 42 W pro FET führt.

Ein alternativer Ansatz ist dargestellt in Abbildung 3-8. Hier wird die mitschwingended Kondensatorspannung in Verbindung mit einer Differenzierschaltung implementiert, um den sinusförmigen Strom zu erzeugen. Das neu entstehende Sinussignal wird durch einen Differential-Single-End-OPA(OPA354) und einen schnellen Komparator (TLV3501) für ZCD weiterverarbeitet.

Abbildung 3-8 ZCD-Schaltkreis mit ISOW7741, ISOW7841

Abbildung 3-8 ZCD-Schaltkreis mit ISOW7741, ISOW7841Das Nulldurchgangssignal wird durch einen digitalen Isolator (ISOW7741 oder ISOW7841) isoliert. Diese digitalen Isolatoren verfügen über integrierte isolierte DC/DC-Wandler, um eine isolierte Stromversorgung für die OPA- und Komparatorbausteine zu erzeugen. Die OPA354, TLV3501 und ISOW7741 weisen Ausbreitungsverzögerungen von 0,6 ns, 4,5 ns und 10,7 ns auf, was zu einer Gesamtausbreitungsverzögerung 15,8 ns für das gesamte Design führt, die etwa 10-mal kleiner ist als ein CT- oder Rogowski-Spulenansatz. Nehmen wir die gleiche Schaltfrequenz und den gleichen Spitzenstrom wie im vorherigen Beispiel an, so kann der Spitzenenergieverlust in einem FET von 42 W auf nur 6,7 W reduziert werden (was sich positiv auf den Gesamtwirkungsgrad auswirkt).