KOKA011 September 2020 TPS55288 , TPS55288-Q1 , TPS552882 , TPS552882-Q1

2.3.2 대칭 레이아웃 구성의 사용

EMI 성능은 임계 스위칭 루프를 최소화하고 임계 스위칭 루프 아래에그라운드 판을 추가하여 개선할 수 있습니다. 테스트 결과가 여전히 한계를 초과하는 경우, 전환 속도를 늦추거나 전원 공급 회로에 금속 쉴드를 추가하는 것과 같은 다른 해결책을 고려해야 합니다. 그러나 전환 속도를 늦추면 효율성이 저하되고, 금속 쉴딩을 추가할 경우 비용이 증가하며 시스템 조립이 더욱 복잡해집니다.

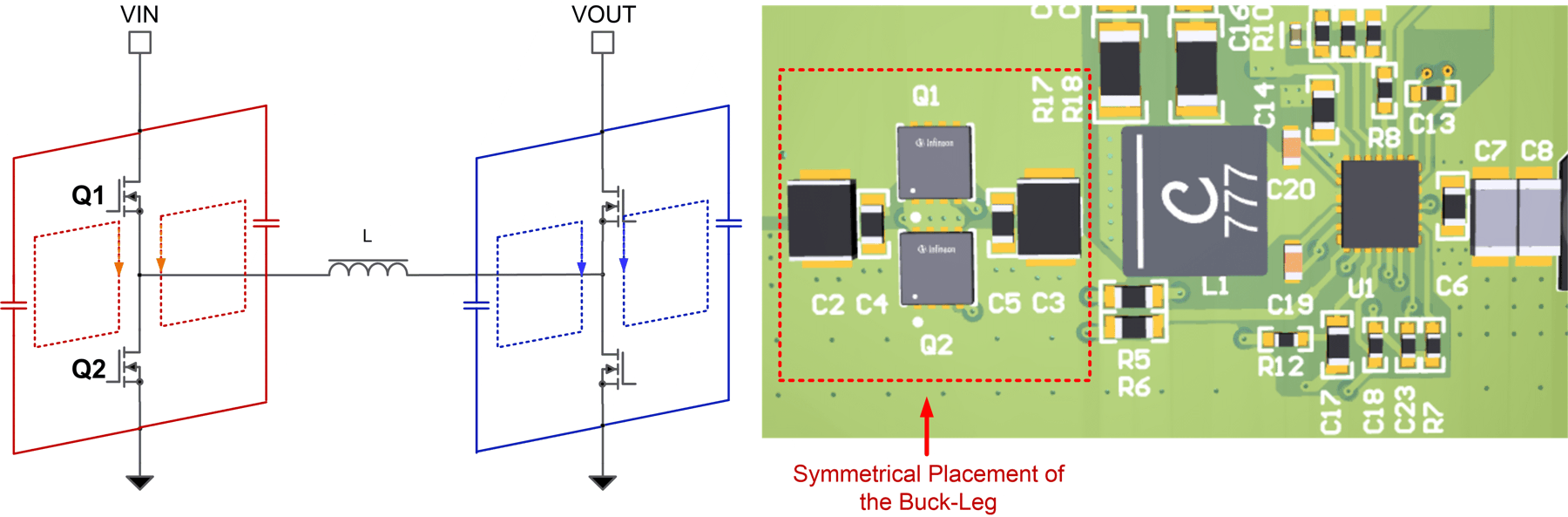

디커플링 커패시터의 대칭 배치를 사용하면 효율을 희생하거나 비용을 증가시키지 않으면서 EMI 성능을 더욱 향상시킬 수 있다. 그림 2-6 및 그림 2-7은 이 대칭 배치 개념의 회로도 및 관련 PCB 레이아웃을 보여줍니다.

그림 2-6 TPS55288 벅-부스트 컨버터의 대칭 PCB 배치

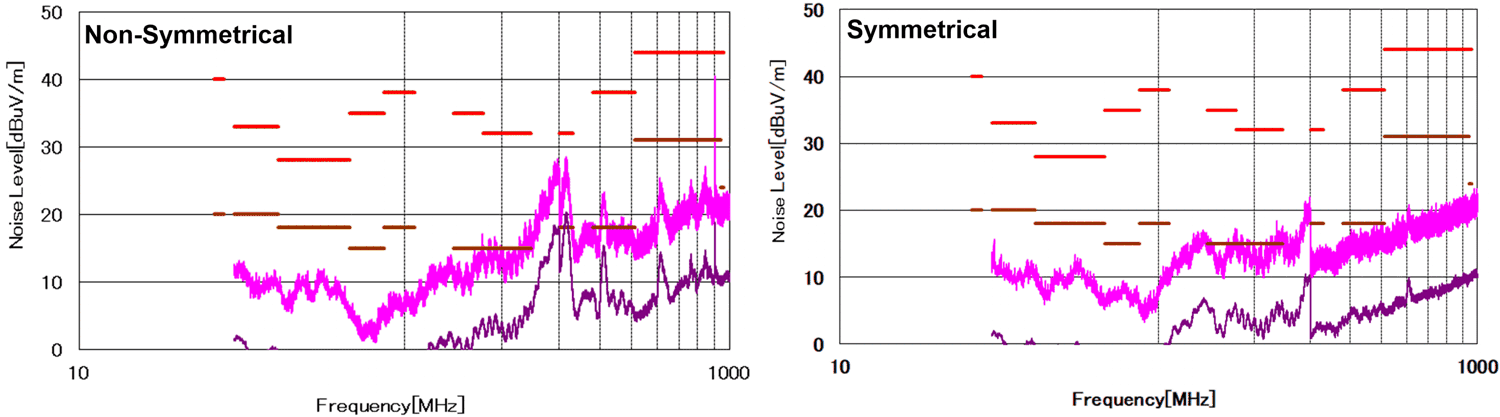

그림 2-6 TPS55288 벅-부스트 컨버터의 대칭 PCB 배치그림 2-7은 대칭 배치와 대칭 배치 없이 방사된 EMI 결과를 보여줍니다. 대칭 배치는 200MHz~600MHz 고주파 범위에서 방사 EMI를 줄이는 데 도움이 되며, 대칭 배치는 6dBuV/m 이상 개선됩니다.

그림 2-7 대칭 배치에 따른 방사 EMI 비교

그림 2-7 대칭 배치에 따른 방사 EMI 비교