KOKA011 September 2020 TPS55288 , TPS55288-Q1 , TPS552882 , TPS552882-Q1

2.3.4 스위칭 노드에 RC 스너버 추가

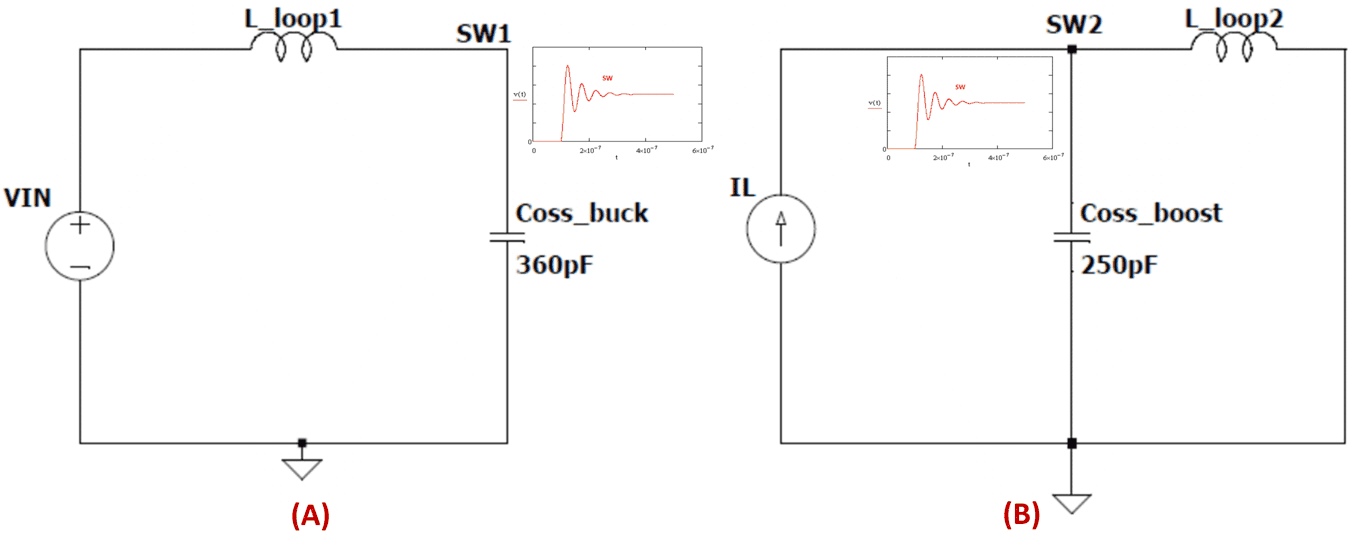

스위칭 루프는 LC 회로로 모델링할 수 있습니다. 입력 또는 출력 측 디커플링 커패시터와 하이사이드 및 로우사이드 MOSFET에 의해 형성됩니다. 벅-레그 스위칭 노드 SW1의 경우, 링잉은 하이사이드 FET가 ON이고 로우사이드 FET가 OFF일 때 발생합니다. 부스트 레그 스위칭 노드 SW2의 경우, 링잉은 로우사이드 FET가 오프이고 하이사이드 FET가 온일 때 발생합니다. 그림 2-10은 이 전환 상태 동안 스위칭 루프의 등가 모델을 보여줍니다.

등가 모델(L_loop1 및 L_loop2)의 인덕턴스는 PCB 트레이스 인덕턴스, 디커플링 커패시터의 ESL 및 MOSFET의 패키지 인덕턴스를 포함하는 스위칭 루프의 전체 루프 인덕턴스에 해당합니다. 루프의 총 캐패시턴스는 로우사이드 MOSFET의 출력 캐패시턴스에 의해 결정됩니다. 그러므로, 스위칭 노드 링잉 주파수는 기생 루프 인덕턴스와 낮은 쪽 MOSFET 출력 캐패시턴스에 의해 결정됩니다. 주어진 스위칭 속도와 주어진 MOSFET의 경우, 링잉의 최대 진폭은 또한 기생 루프 인덕턴스에 의해 결정됩니다.

이전 챕터에서, 우리는 소형 배치, 스위칭 루프 아래에 그라운드 판을 추가하거나 대칭 PCB 레이아웃을 사용하여 기생 루프 인덕턴스를 줄일 수 있다는 것을 알고 있습니다. 그러나 실제 애플리케이션에서 부품 배치는 PCB 크기에 의해 제한됩니다.

그림 2-10 스위칭 루프의 등가 모델

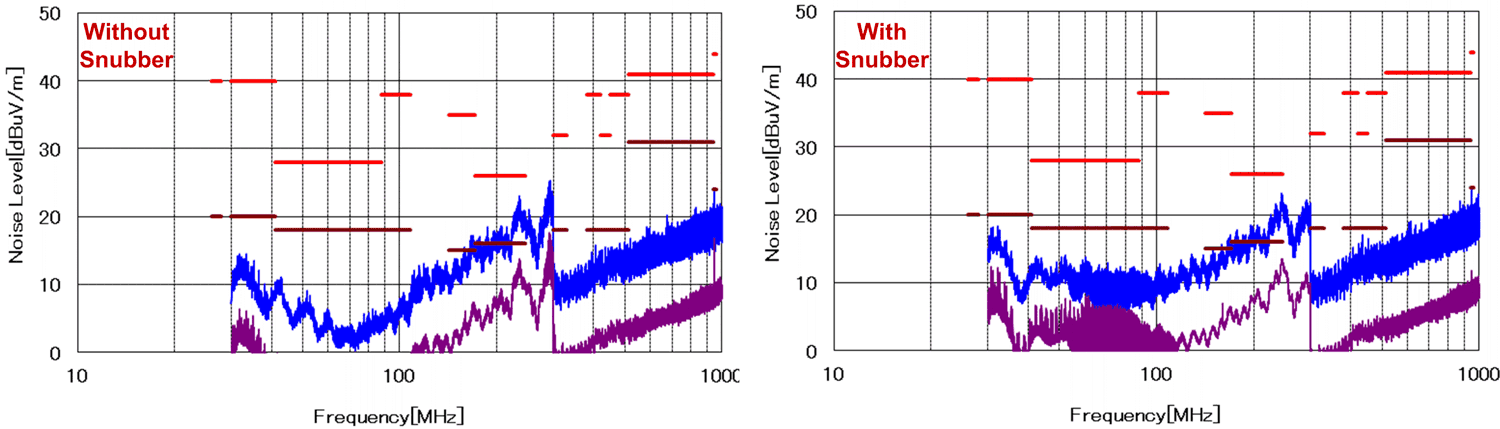

그림 2-10 스위칭 루프의 등가 모델방사선 EMI 레벨이 여전히 요구 수준을 초과하고 레이아웃을 더 이상 개선할 수 없는 경우 어떻게 해야 할까요? 스위칭 노드와 전원 그라운드에 RC 스너버를 추가하면 방사선 EMI 수준을 줄이는 데 도움이 될 수 있습니다. RC 스너버는 가능한 한 스위칭 노드와 그라운드 판에 가깝게 배치해야 합니다. 그림 2-11은 RC 스너버가 있는 경우와 없는 경우의 방사선 EMI 비교 결과를 보여줍니다. 방사선 EMI는 RC 스너버로 300MHz에서 약 6dBuV/m 향상되었습니다.

그림 2-11 RC 스너버 사용 및 미사용 시 방사선 EMI 비교

그림 2-11 RC 스너버 사용 및 미사용 시 방사선 EMI 비교