KOKA059 December 2022 AMC1202 , AMC1302 , AMC1306M05 , AMC22C11 , AMC22C12 , AMC23C10 , AMC23C11 , AMC23C12 , AMC23C14 , AMC23C15 , AMC3302 , AMC3306M05

3.3 지점 G - DC/DC 탱크 전류 감지

이 섹션에서는 스위칭 탱크 지점 G의 전류 감지 요구 사항을 설명합니다. 동기 정류에는 공진 CLLLC 양방향 절연 DC/DC 컨버터 ZCD(제로 크로싱 감지)가 필요하며, 이는 전도 손실을 줄이고 시스템 효율성을 개선하는 데 도움이 됩니다.

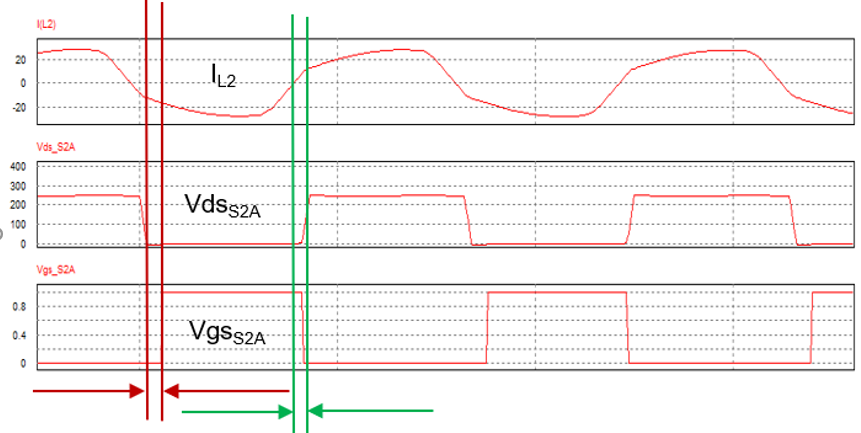

그림 3-6 절연 DC/DC 컨버터의 1차 또는 2차 탱크에서 전류 감지

그림 3-6 절연 DC/DC 컨버터의 1차 또는 2차 탱크에서 전류 감지그림 3-6에서 두 개의 녹색 커서 라인은 제로 크로싱과 2차측 FET 턴온 사이의 전파 지연을 나타냅니다.

그림 3-7 제로 크로싱 감지 전파 지연

그림 3-7 제로 크로싱 감지 전파 지연CLLLC 토폴로지에서 ZCD 회로를 최첨단으로 구현하는 방법은 1차측과 2차측에 공진 커패시터와 직렬로 전류 변압기(CT) 또는 Rogowski 코일을 배치하는 것입니다. CT 또는 Rogowski 코일 접근 방식의 일반적인 전파 지연은 100ns~200ns 사이입니다. 이러한 지연은 CLLLC 토폴로지에서 상당한 손실을 발생시킬 수 있으며 부정적인 방식으로 DC/DC 컨버터의 전체 효율에 영향을 미칩니다. 피크 전류가 약 30A라고 가정하면 공진 스위칭 주파수가 500kHz이고 턴온 지연이 100ns인 경우 바디 다이오드(순방향 전압 4.5V인 경우)가 FET가 켜질 때까지 FET는 9.3A를 운반합니다. 그 결과 FET당 약 42W의 최대 에너지 손실이 발생합니다.

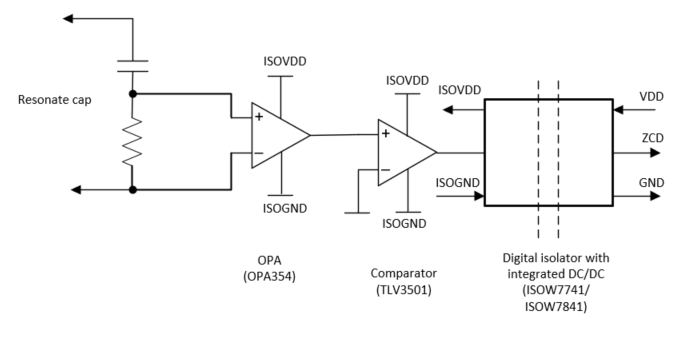

그림 3-8에 다른 접근 방식이 나와 있습니다. 여기에서 차동 회로와 함께 공명 커패시터 전압이 시누소이드 전류를 재생성하기 위해 구현됩니다. 다시 생성된 시누소이드 신호는 차동-단일 엔드 OPA(OPA354)와 ZCD용 고속 비교기(TLV3501)에 의해 추가로 처리됩니다.

그림 3-8 ISOW7741, ISOW7841을 사용하는 ZCD 회로

그림 3-8 ISOW7741, ISOW7841을 사용하는 ZCD 회로제로 크로싱 신호는 디지털 아이솔레이터(ISOW7741 또는 ISOW7841)에 의해 절연됩니다. 이러한 디지털 아이솔레이터는 절연 DC/DC 컨버터를 통합하여 OPA 및 비교기 장치에 대한 절연 전원을 생성합니다. OPA354, TLV3501 및 ISOW7741은 각각 0.6ns, 4.5ns 및 10.7ns의 전파 지연을 가지고 있어 전체 설계에 대한 총 전파 지연이 15.8ns로 CT 또는 Rogowski 코일 접근 방식보다 약 10배 작습니다. 이전 예와 동일한 스위칭 주파수 및 피크 전류를 가정하면 한 FET의 피크 에너지 손실이 42W에서 6.7W로 감소할 수 있습니다(전체 효율에 긍정적인 영향을 미침).