NESA009A november 2022 – march 2023 MSPM0G1105 , MSPM0G1106 , MSPM0G1107 , MSPM0G1505 , MSPM0G1506 , MSPM0G1507 , MSPM0G3105 , MSPM0G3106 , MSPM0G3107 , MSPM0G3505 , MSPM0G3506 , MSPM0G3507 , MSPM0L1105 , MSPM0L1106 , MSPM0L1303 , MSPM0L1304 , MSPM0L1305 , MSPM0L1306 , MSPM0L1343 , MSPM0L1344 , MSPM0L1345 , MSPM0L1346

2.3 偵錯工具

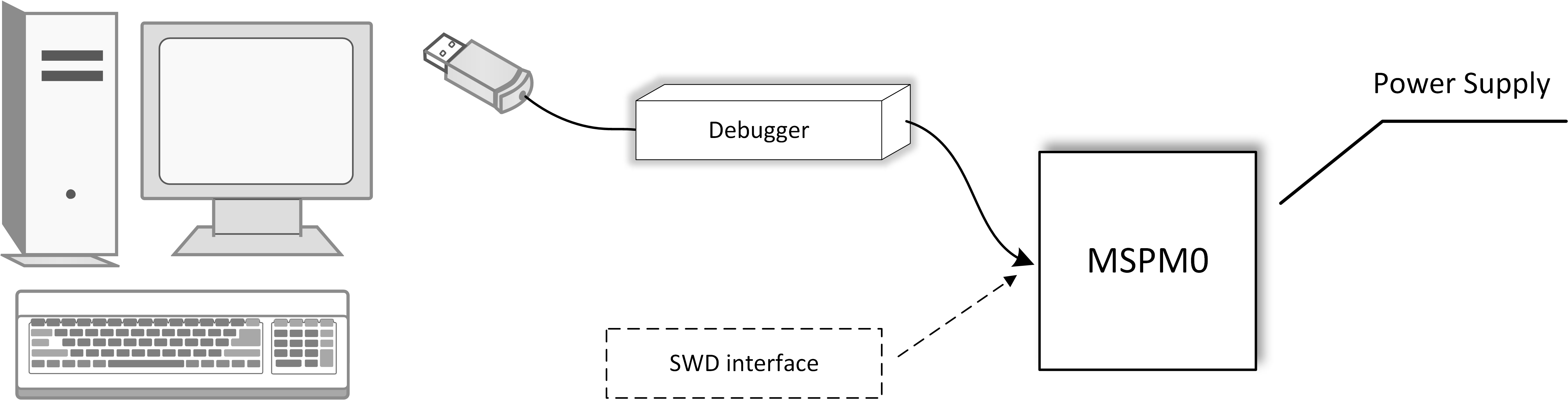

偵錯子系統 (DEBUGSS) 可將序列線偵錯 (SWD) 雙線實體介面連接至裝置內的多個偵錯功能。MSPM0 裝置支援對處理器執行、裝置狀態和電源狀態 (使用 EnergyTrace 技術) 進行偵錯。圖 2-3 顯示偵錯器的連線。

MSPM0 支援適用於標準序列線偵錯的 XDS110 和 J-Link 偵錯器。

德州儀器 XDS110 是針對 TI 嵌入式處理器而設計的。XDS110 透過 TI 20 針腳連接器 (具有適用於 TI 14 針腳和 Arm 10 針腳和 Arm 20 針腳的多重轉接器) 連接到目標電路板,並透過 USB2.0 2.0 高速 (480 Mbps) 連接到主機 PC。它支援單一 Pod 中更廣泛的標準 (IEEE1149.1、IEEE1149.7、SWD)。所有 XDS 偵錯探針都支援所有配備嵌入式追蹤緩衝器 (ETB) 的 Arm 與 DSP 處理器的核心與系統追蹤。如需詳細資訊,請參閱 XDS110 偵錯探針。

J-Link 偵錯探針是偵錯與快閃記憶體編程體驗最佳化的最受歡迎選擇。受益於破紀錄的快閃載入程式,具備高達 3 MiB/s RAM 下載速度,以及在 MCU 快閃記憶體中設定數量無限的斷點的能力。J-Link 也支援廣泛的 CPU 及架構,包含 CortexM0+。如需詳細資訊,請造訪 Segger J-Link 偵錯探針頁面。

圖 2-3 顯示 XDS110 探針至 MSPM0 目標的主要功能區和介面的高階圖。

圖 2-3 MSPM0 偵錯

圖 2-3 MSPM0 偵錯