NEST086 September 2024 ADC32RF55 , DAC39RF12

2 何謂跳頻?

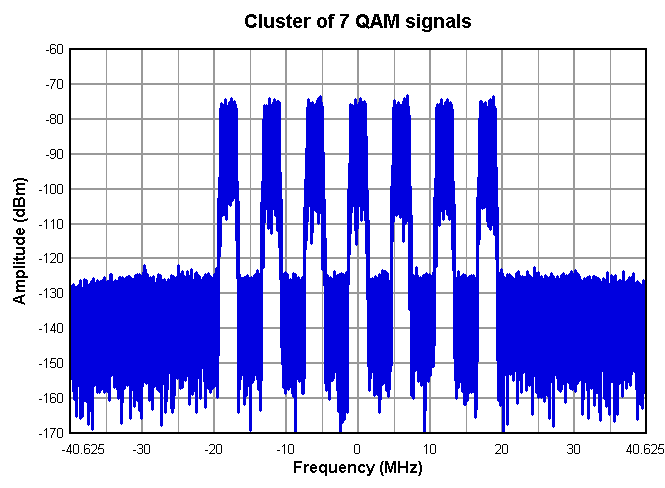

在 Wi-Fi® 6 和 7 或正交振幅調變 (QAM) 編碼訊號等現代通訊系統中,頻譜的本質為多頻帶,這意味著射頻 (RF) 域是由各頻帶內的多個通道組成。例如,Wi-Fi 6 和 7 可在同一頻帶內的多個通道間運作,以透過動態方式將頻寬和資料輸送量提升到最高,而 QAM 則是在單一通道內,將資料編碼為不同的相位偏移和振幅位準。圖 1 顯示包含 7 個 QAM 通道的頻帶範例。

圖 1 頻域中的多音訊號。

圖 1 頻域中的多音訊號。直接 RF 取樣類比轉數位轉換器 (ADC) 和數位轉類比轉換器 (DAC) 整合了許多數位功能。實現直接 RF 取樣的最重要功能之一,就是 ADC 中的數位降轉換器 (DDC),以及 DAC 中的數位上轉換器 (DUC)。

在 ADC 中,DDC 是由三個主要元件組成:NCO、數位混頻器和降頻器區塊。NCO 可做為傳統接收器訊號鏈中本機振盪器的數位同等裝置,並與輸入訊號混合,以提供基頻(奈奎斯特 1 區)的訊號,以及不必要的影像。降頻器區塊會透過有限脈衝反應 (FIR) 降頻濾波器濾除影像,然後透過降低取樣減少訊號頻寬。降頻器區塊是中頻 (IF) 濾波器的數位等效裝置。

在 DAC 中,DUC 是由內插器、NCO 和數位混頻器組成。內插器與 ADC 不同,會對較低頻寬的輸入訊號進行上取樣,然後將其傳經 FIR 濾波器,以抑制影像。在內插器級後,輸出訊號會饋入數位混頻器以與 NCO 混合,讓 DAC 能以較低的輸入訊號頻寬在較寬的奈奎斯特區中運作。

在 RF 取樣轉換器任何特定輸入上啟用的 DDC 數量,決定了轉換器是以單頻帶或多頻帶輸出運作。本文的重點會放在跳頻的 ADC 層面上。

圖 2 顯示德州儀器 (TI) ADC32RF55 的 DDC 範例,這是一款 RF 取樣 ADC,能夠以 3GSPS 進行雙通道、四頻帶運作。

圖 2 ADC32RF55 的功能原理圖(每個通道四個 DDC)。

圖 2 ADC32RF55 的功能原理圖(每個通道四個 DDC)。通常,相關頻帶會改變:相對於針對每個頻帶切換完全唯一的訊號鏈,同一個 RF 取樣轉換器只需調整 NCO 頻率,就可配合新的頻帶。這是現代 RF 取樣轉換器的主要優點。將 NCO 從某一頻率變更至不同頻率的行為,就是所謂的跳頻。

NCO 不會直接產生類比頻率,而是會以高解析度產生所需頻率的數位呈現。每個 NCO 都會接收一個數位字(通常為 48 位元或更多),將該字與 NCO 相位累加器結合後,即可呈現適合數位混頻級的訊號。編程 NCO 時,需編程的是與所需 IF 對應的數位呈現,而不是實際頻率。最常受到支援的 NCO 頻率範圍介於 –Fs/2 與 Fs/2 之間,其中 Fs 代表轉換器的取樣頻率。負頻率字用於奈奎斯特偶數區,正頻率字則用於奈奎斯特奇數區的訊號。

為了判斷更高次 NCO 頻率落在基頻中的位置,您的第一項作業就是在預期頻率和取樣率之間執行模除運算,以移除 Fs 的任何倍數。預期 NCO 頻率現在介於 0Hz 和轉換器取樣率 Fs 之間。

如果 NCO 頻率低於奈奎斯特頻率 (Fs/2),則預期 NCO 頻率會轉換至奈奎斯特奇數區,如 方程式 1 所示:

如果計算的 NCO 頻率高於奈奎斯特頻率,則頻率會落在奈奎斯特偶數區,如 方程式 2 所示:

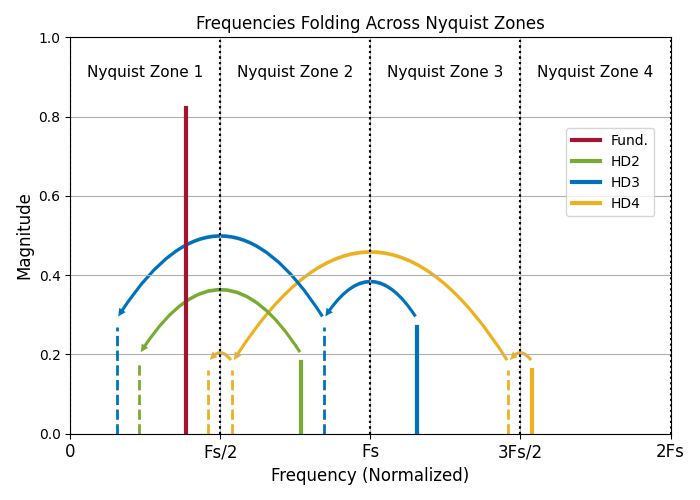

圖 3 顯示基頻訊號 (Fund.) 及其二次、三次和四次諧波(HD2、HD3 和 HD4)如何折返至奈奎斯特第一區,雖然實際頻率分量會落在更高次的奈奎斯特區中。

圖 3 諧波從高次奈奎斯特區折至奈奎斯特 1 區。

圖 3 諧波從高次奈奎斯特區折至奈奎斯特 1 區。與傳統 ADC 相比,RF 取樣 ADC 的其中一個優點是不需要變更硬體即可切換頻帶。這種固有的彈性可讓 RF 取樣 ADC 無需額外硬體元件,即可快速因應新頻帶,進而簡化系統設計並降低成本。然而,前述程序無法瞬時完成。在 RF 取樣 ADC 的早期設計中,對每個 NCO 和後續 DDC 都只提供單一的 NCO 字選項。因此,跳至另一個頻率需要進行多次暫存器寫入操作。

新的 NCO 字必須透過序列週邊介面 (SPI) 寫入,接著再進行另一個暫存器寫入,以將新的 NCO 字推送至 DDC 區塊,並在該處實際生效。有數項因素會影響跳頻所需的時間,包括 NCO 字的長度和 SPI 事務速度。通常,ADC 的暫存器大小限制為 8 位元,因此總共需要進行七次暫存器寫入來更新 48 位元 NCO:以六次暫存器寫入更新 NCO 字本身,並以另一次暫存器寫入更新 DDC。

考量每項 SPI 事務的負擔(通常每次暫存器寫入為 16 位元位址)後,事務時間會增加三倍。假定為 20MHz 序列時鐘訊號 (SCLK) 率,方程式 3 可計算跳頻時間,並假設 SPI 資料的串流不間斷: