SBAU171D May 2010 – January 2016 ADS1198 , ADS1298

-

ADS1298ECG-FE/ADS1198ECG-FE

- Trademarks

- 1 ADS1298ECG-FE/ADS1198ECG-FE Overview

- 2 Quick Start

- 3

Using the ADS1298ECG-FE Software

- 3.1 Application User Menu

- 3.2 Top-Level Application Controls

- 3.3 About Tab

- 3.4 ADC Register Tab

- 3.5 Analysis Tab

- 3.6 Save Tab

- 4 ADS1x98ECG-FE Input Signals

- 5 ADS1298ECG-FE/ADS1198ECG-FE Hardware Details

- ASchematics, BOM, Layout, and ECG Cable Details

- BExternal Optional Hardware

- CSoftware Installation

2.1 Default Jumper/Switch Configuration

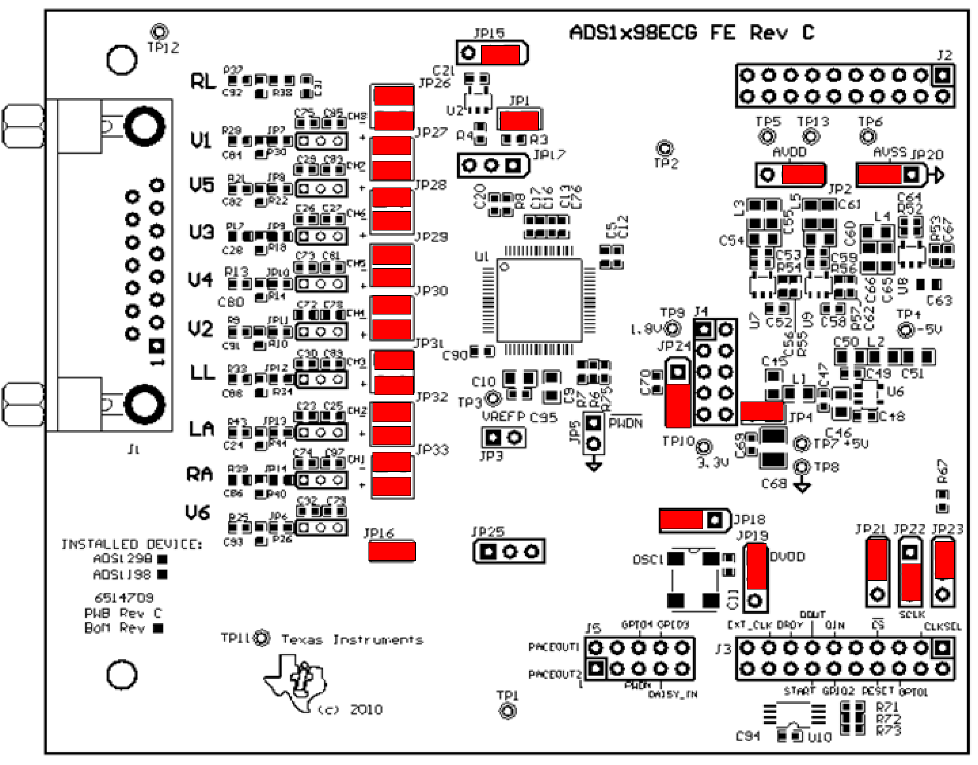

Figure 2 shows the jumpers found on the ADS1x98ECG-FE EVM and the respective factory default conditions for each.

Figure 2. ADS1x98ECG-FE Default Jumper Locations

Figure 2. ADS1x98ECG-FE Default Jumper Locations Table 1 lists the jumpers and switches and the factory default conditions.

Table 1. ADS1x98ECG-FE Default Jumper/Switch Configuration

| Jumper | Default Position | Description |

|---|---|---|

| JP1 | Installed | RLD feedback |

| JP2 | Installed 1-2 | AVDD selected for bipolar supply operation selected (AVDD = +2.5V) |

| JP3 | Header Not Installed | External Vref buffer not connected |

| JP4 | Installed | EVM +5V provided from J4 (power header) |

| JP5 | Open | PWDN pin controlled from J5 header (pulled up to DVDD) |

| JP6 to JP14 | Header Not Installed (Pins 1-2 shorted on PCB) | DC-coupled input signals |

| JP15 | Installed 2-3 | Shield drive is open |

| JP16 | Installed | Wilson Central Terminal (WCT) connected to INM for CH1 and CH4-8 |

| JP17 | Header Not Installed | ECG shield drive |

| JP18 | Installed 2-3 | CLK connected to OSC1 |

| JP19 | Installed 1-2 | OSC1 enabled |

| JP20 | Installed 2-3 | AVSS selected for bipolar supply operation (AVSS = -2.5V) |

| JP21 | Installed 1-2 | CS connected to DSP via J3.1 |

| JP22 | Installed 2-3 | START comes from J3.14 |

| JP23 | Installed 1-2 | CLKSEL set to 0 (ADS1198 uses Ext Master Clock (OSC1)) |

| JP24 | Installed 2-3 | DVDD supply = 3.3V |

| JP25 | Header Not Installed | No external reference selected |

| JP26 | Installed 1-2 (top) | WCT connected to CH8- input |

| Installed 3-4 (bottom) | ECG_V1 connected to CH8+ input | |

| JP27 | Installed 1-2 (top) | WCT connected to CH7- input |

| Installed 3-4 (bottom) | ECG_V5 connected to CH7+ input | |

| JP28 | Installed 1-2 (top) | WCT connected to CH6- input |

| Installed 3-4 (bottom) | ECG_V3 connected to CH5+ input | |

| JP29 | Installed 1-2 (top) | WCT connected to CH5- input |

| Installed 3-4 (bottom) | ECG_V4 connected to CH6+ input | |

| JP30 | Installed 1-2 (top) | WCT connected to CH4- input |

| Installed 3-4 (bottom) | ECG_V2 connected to CH4+ input | |

| JP31 | Installed 1-2 (top) | ECG_RA connected to CH3- input |

| Installed 3-4 (bottom) | ECG_LL connected to CH3+ input | |

| JP32 | Installed 1-2 (top) | ECG_RA connected to CH2- input |

| Installed 3-4 (bottom) | ECG_ LA connected to CH2+ input | |

| JP33 | Installed 1-2 (top) | WCT connected to CH1- input |

| Installed 3-4 (bottom) | ECG_V6 connected to CH1+ input |