SLAT161 June 2022 HD3SS3411 , TMUXHS4412

2.2.3 Separate Reference Clock

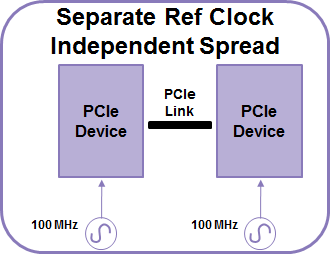

Another clocking architecture is the Separate Reference architecture where a different clock source is used at each end of the PCIe link. The advantage of this architecture is that tightly controlled reference clock distribution is no longer required over connectors and backplanes.

Figure 2-4 Seperate Clock

Architecture

Figure 2-4 Seperate Clock

ArchitectureFrom three refclk architecture, the common refclk architecture is the easiest and most commonly used method for clock distribution among PCIe devices. Only test common refclk architecture is tested in this application report.