SLUSDD4B April 2019 – December 2020

PRODUCTION DATA

- 1 Features

- 2 Applications

- 3 Description

- 4 Revision History

- 5 Pin Configuration and Functions

- 6 Specifications

- 7 Detailed Description

- 8 Application Information Disclaimer

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Mechanical, Packaging, and Orderable Information

5 Pin Configuration and Functions

Figure 5-1 HKU

Package

Figure 5-1 HKU

Package10-Pin CFP

Top View

Table 5-1 Pin Functions

| PIN | I/O | DESCRIPTION | |||

|---|---|---|---|---|---|

| NAME | NO. | ||||

| Comp | 1 | I | Error amplifier output. | ||

| VFB | 2 | I | Voltage feedback input to error amplifier. | ||

| ISENSE | 3 | I | Current sense comparator input pin. | ||

| RT/CT | 4 | I | RC time constant input to oscillator. | ||

| NC | 5, 6 | — | No connect. | ||

| Gnd | 7 | — | Ground. | ||

| Output | 8 | O | Regulated output. | ||

| VCC | 9 | — | Unregulated supply voltage. | ||

| VREF | 10 | O | 5-V internally generated reference. | ||

Table 5-2 Bare Die Information

| DIE THICKNESS | BACKSIDE FINISH | BACKSIDE POTENTIAL | BOND PAD METALLIZATION COMPOSITION | BOND PAD THICKNESS |

|---|---|---|---|---|

| 15 mils | Backgrind Si - Finish | Ground | AlCu | 2000 nm |

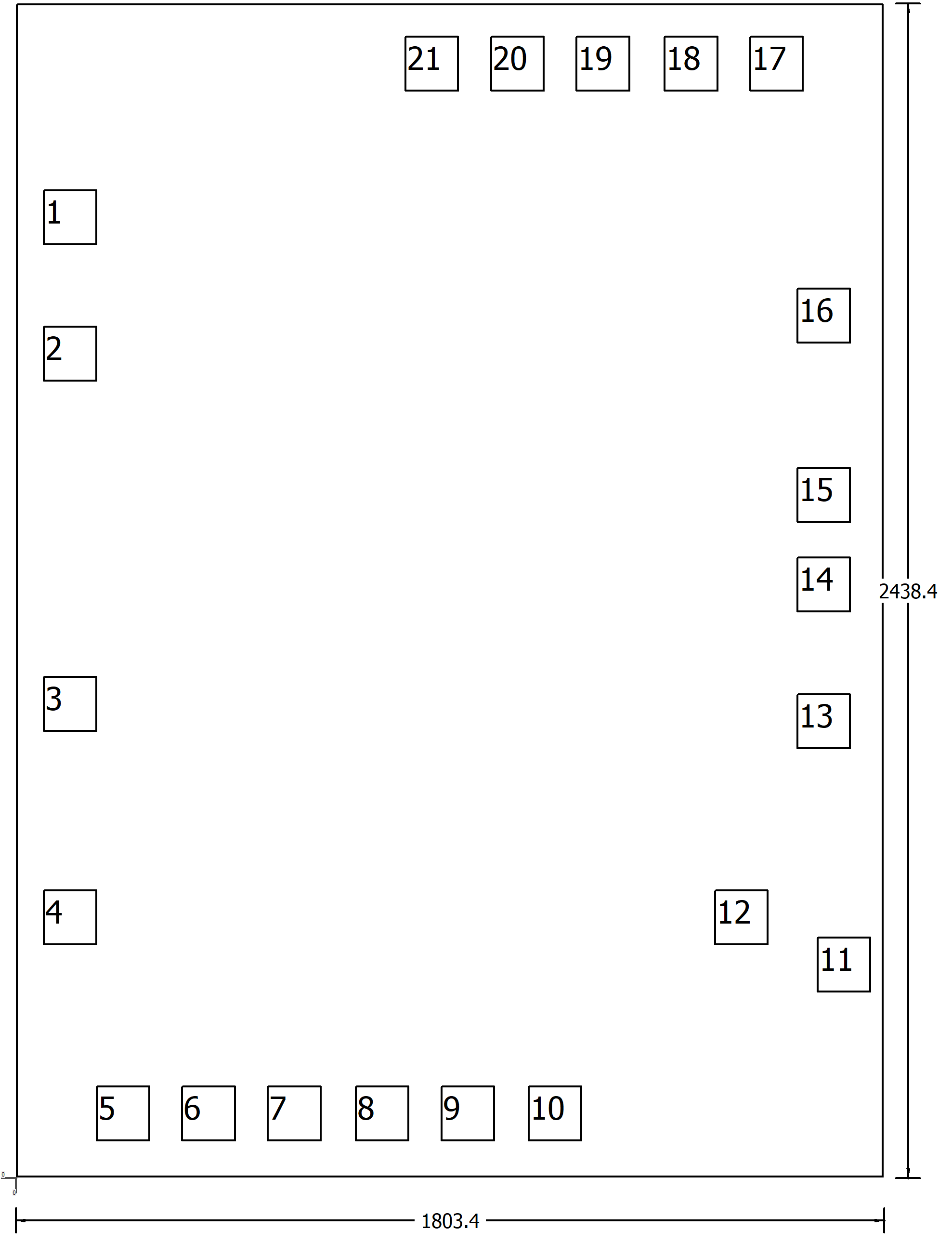

Figure 5-2 UC1843B-SP Bare Die Pin Number

Locations

Figure 5-2 UC1843B-SP Bare Die Pin Number

LocationsTable 5-3 Bond Pad Coordinates in

Microns

| DESCRIPTION | PAD NUMBER | X MIN | Y MIN | X MAX | Y MAX |

|---|---|---|---|---|---|

| COMP | 1 | 55.88 | 1935.458 | 170.181 | 2052.3 |

| VFB | 2 | 55.88 | 1651.829 | 170.181 | 1768.671 |

|

ISENSE |

3 |

55.88 |

925.028 |

170.181 |

1041.87 |

|

Rt/Ct |

4 |

55.88 |

481.858 |

170.181 |

598.7 |

|

N/C |

5 |

165.623 |

74.746 |

279.925 |

191.588 |

|

N/C |

6 |

343.425 |

74.746 |

457.726 |

191.588 |

|

N/C |

7 |

521.227 |

74.746 |

635.528 |

191.588 |

|

N/C |

8 |

704.109 |

74.746 |

818.41 |

191.588 |

|

N/C |

9 |

881.91 |

74.746 |

996.211 |

191.588 |

|

N/C |

10 |

1062.932 |

74.746 |

1177.234 |

191.588 |

|

GND |

11 |

1662.756 |

384.359 |

1777.057 |

501.201 |

|

GND |

12 |

1449.69 |

481.858 |

1563.991 |

598.7 |

|

OUTPUT |

13 |

1620.685 |

889.041 |

1734.986 |

1005.883 |

|

VCC |

14 |

1620.685 |

1172.67 |

1734.986 |

1289.512 |

|

VCC |

15 |

1620.685 |

1358.803 |

1734.986 |

1475.644 |

|

VREF |

16 |

1620.685 |

1731.066 |

1734.986 |

1847.907 |

|

N/C |

17 |

1523.03 |

2254.009 |

1637.331 |

2370.85 |

|

N/C |

18 |

1345.228 |

2254.009 |

1459.529 |

2370.85 |

|

N/C |

19 |

1162.346 |

2254.009 |

1276.647 |

2370.85 |

|

N/C |

20 |

984.544 |

2254.009 |

1098.846 |

2370.85 |

|

N/C |

21 |

806.742 |

2254.009 |

921.043 |

2370.85 |