SLUSDG3F August 2018 – September 2024

PRODUCTION DATA

- 1

- 1 Features

- 2 Applications

- 3 Description

- 4 Pin Configuration and Functions

-

5 Specifications

- 5.1 Absolute Maximum Ratings

- 5.2 ESD Ratings (Automotive)

- 5.3 Recommended Operating Conditions

- 5.4 Thermal Information

- 5.5 Power Ratings

- 5.6 Insulation Specifications

- 5.7 Safety Limiting Values

- 5.8 Electrical Characteristics

- 5.9 Timing Requirements

- 5.10 Switching Characteristics

- 5.11 Insulation Characteristics Curves

- 5.12 Typical Characteristics

- 6 Parameter Measurement Information

- 7 Detailed Description

-

8 Application and Implementation

- 8.1 Application Information

- 8.2

Typical Application

- 8.2.1 Design Requirements

- 8.2.2 Detailed Design Procedure

- 8.2.3 Application Curves

- 9 Power Supply Recommendations

- 10Layout

- 11Device and Documentation Support

- 12Revision History

- 13Mechanical, Packaging, and Orderable Information

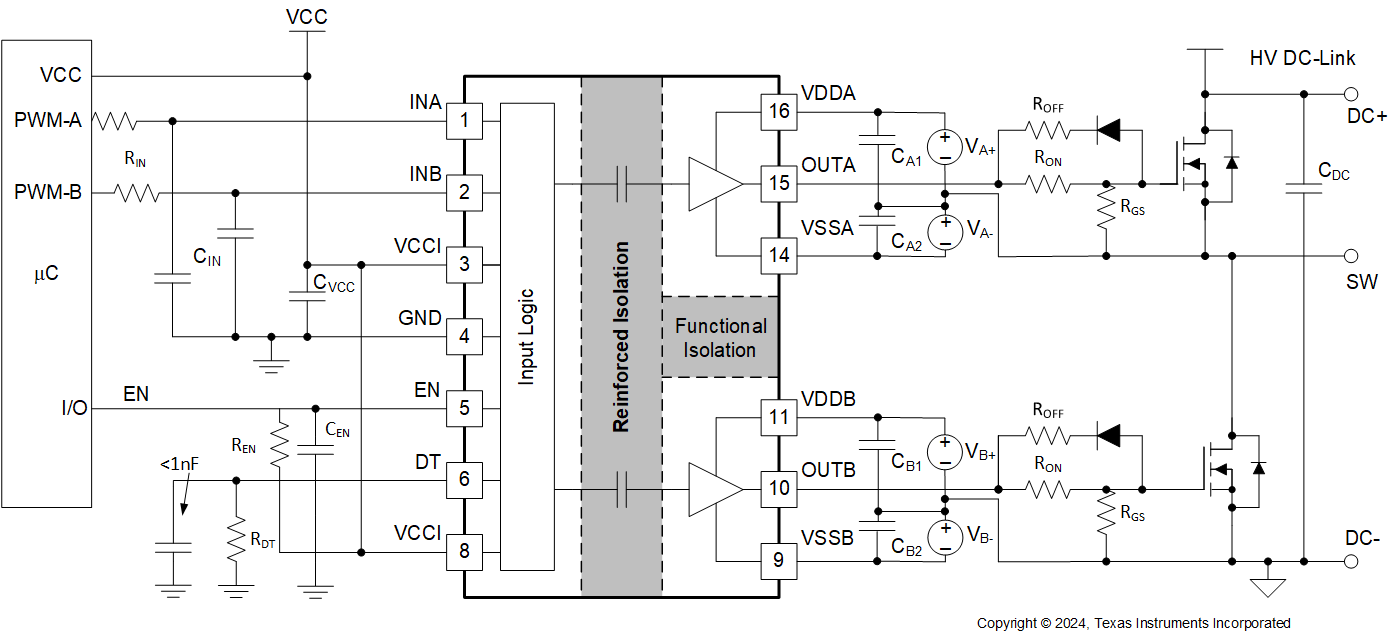

8.2 Typical Application

The circuit in Figure 8-1 shows a reference design with UCC21530-Q1 driving a typical half-bridge configuration which could be used in several popular power converter topologies such as synchronous buck, synchronous boost, half-bridge/full bridge isolated topologies, and 3-phase motor drive applications. This circuit uses two supplies (or single-input-double-output power supply). Power supply VA+ determines the positive drive output voltage and VA– determines the negative turn-off voltage. The configuration for channel B is the same as channel A.

When parasitic inductances are introduced by non-ideal PCB layout and long package leads (e.g. TO-220 and TO-247 type packages), there could be ringing in the gate-source drive voltage of the power transistor during high di/dt and dv/dt switching. If the ringing is over the threshold voltage, there is the risk of unintended turn-on and even shoot-through. Applying a negative bias on the gate drive is a popular way to keep such ringing below the threshold. This solution has two separate power supplies for each driver channel, so it provides flexibility when setting the positive and negative rail voltages.

Figure 8-1 Typical

Application Schematic with Dual Power Supplies

Figure 8-1 Typical

Application Schematic with Dual Power Supplies