SLVAF44 April 2021 TPS5432

4 Investigation on a Long-Term Reliability

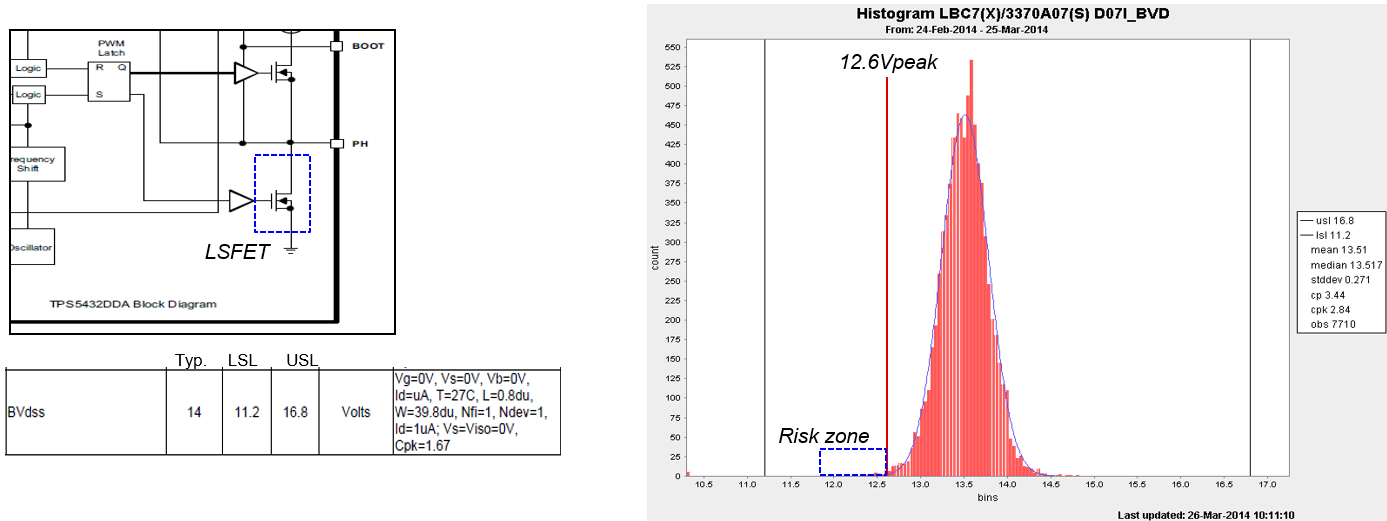

When looking into the breakdown voltage of LSFET and the distribution data in order to see whether the overstress on the switching node can reach the Breakdown voltage of LSFET as shown in Figure 4-1 (left). The worst voltage level, 12.6V is reaching minimum spec of the breakdown voltage of LSFET and some devices are in the risk zone (5 / 7,710 units) based on the distribution data as shown in Figure 4-1 (right).

Figure 4-1 Breakdown Voltage and

Distribution data

Figure 4-1 Breakdown Voltage and

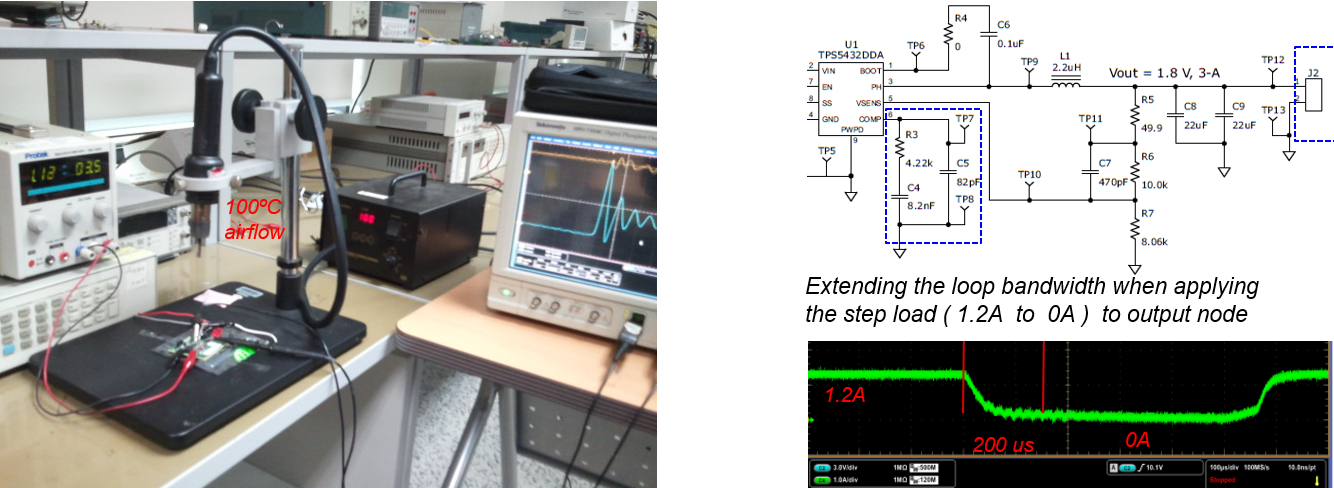

Distribution data Figure 4-2 (left) shows the test bench and the duplication conditions in order to duplicate a similar overshoot voltage with TPS5432 EVMs. Duplication conditions are that Input voltage is changed from 3.3V to 3.5 V and temperature condition is 100ºC airflow to simulate real TV application condition. In addition, external components including compensation values and output filters are changed as a shown in Figure 3-1 (left). To make a similar load release as real TV application, the step load from 1.2 to 0A is applied on output node with dynamic electronic load. Totally, 40 pcs x TPS5432 EVMs is tested.

Figure 4-2 Reliability Test Set Up and

Condition

Figure 4-2 Reliability Test Set Up and

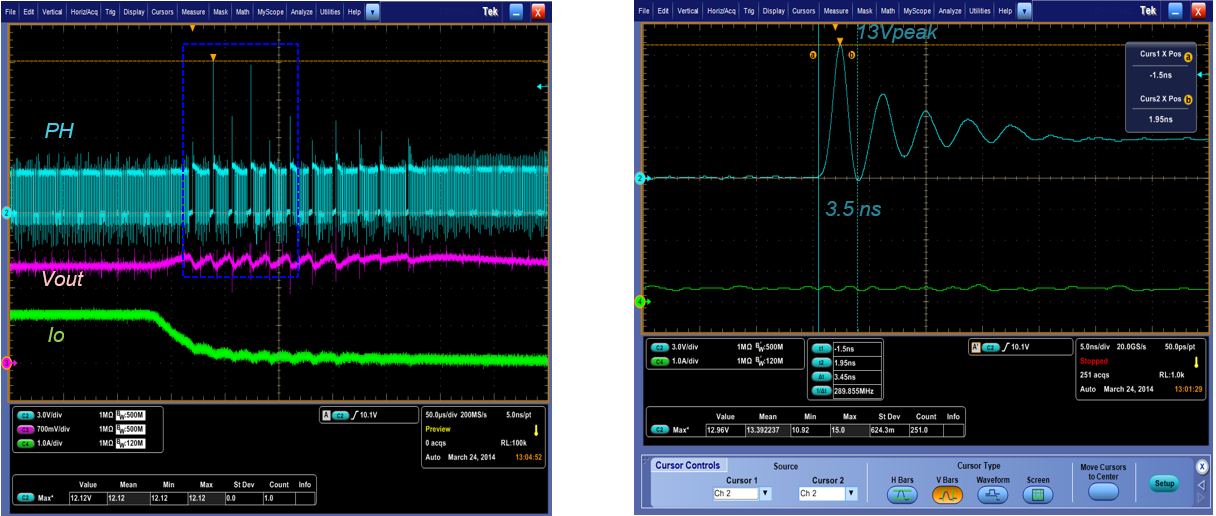

ConditionWhen checking out the overshoot waveforms, repetitive spikes are observed with 3.5ns as transient time and 13 V peak as peak voltage level as shown in Figure 4-3. It is a similar level under a unique load characteristic of SoC chipset.

Figure 4-3 Duplicated Waveform

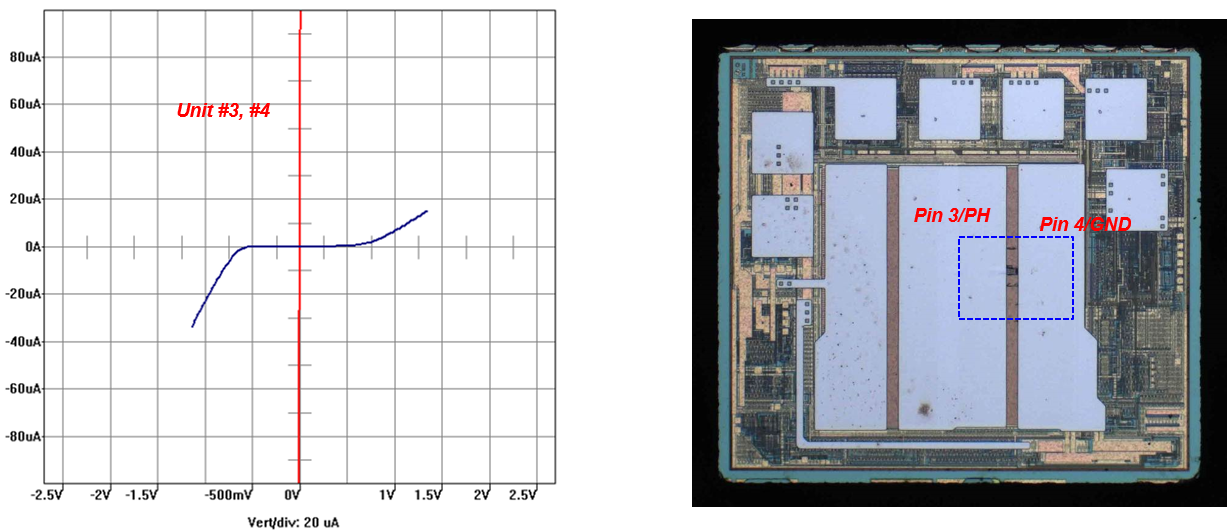

Figure 4-3 Duplicated WaveformWhen continuing to apply the repetitive spikes to devices, LSFET gets softly damaged. 39pcs out of 40 EVMs can support more than 100,000 times without device damage. However, 1pcs out of 40 EVMs gets softly damage after 84,000 times as the worst case. at the time, Input current can be higher than initial level.

As shown in Figure 4-4, it is confirmed that Pin short (Pin 3/PH vs pin 4/GND) is observed and the damage as flashed metal is observed. therefore, it is obvious that a repetitive peak overstress can have a negative impact on a long-term device reliability.

Figure 4-4 Failure Analysis

Figure 4-4 Failure Analysis