SLVK099B March 2022 – September 2023 TPS7H5001-SP , TPS7H5002-SP , TPS7H5003-SP , TPS7H5004-SP

PRODUCTION DATA

- 1

- Abstract

- Trademarks

- 1 Introduction

- 2 Single-Event Effects (SEE)

- 3 Device and Test Board Information

- 4 Irradiation Facility and Setup

- 5 Depth, Range, and LETEFF Calculation

- 6 Test Setup and Procedures

- 7 Destructive Single-Event Effects (DSEE)

- 8 Single-Event Transients (SET)

- 9 Event Rate Calculations

- 10Summary

- A Total Ionizing Dose from SEE Experiments

- B References

- C Revision History

6 Test Setup and Procedures

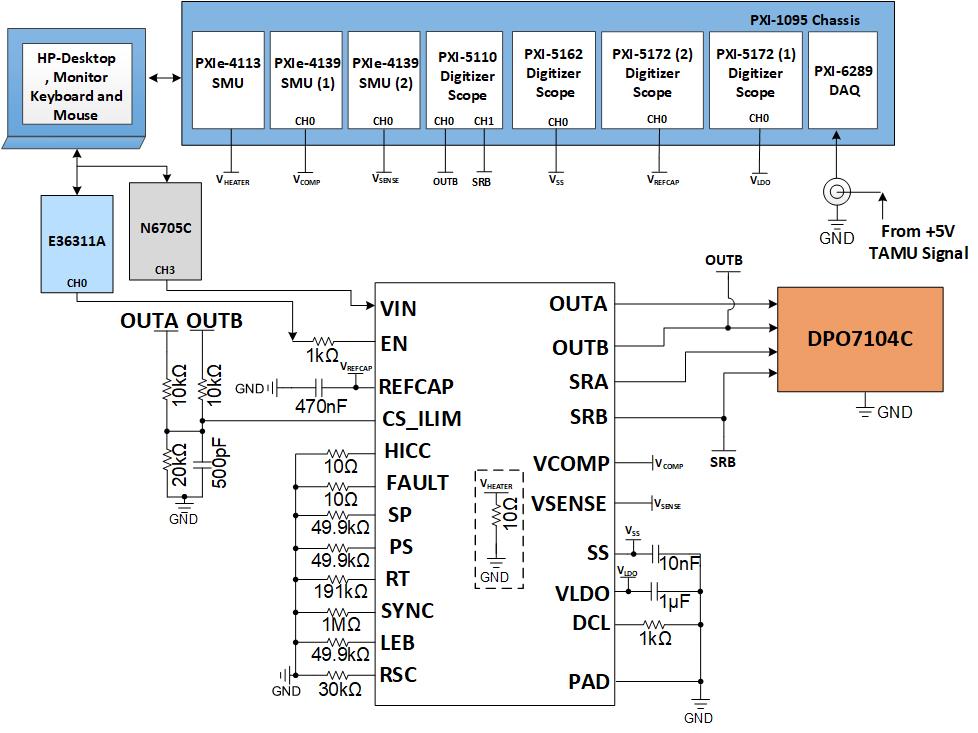

The device power (V)IN was provided using the Agilent N6705C Power supply in a four-wire configuration. For the validation the device was tested using an "open-loop" configuration, under this configuration the VSENSE and VCOMP voltages were forced externally using Channel 0 (CH 0) of two PXIe-4139 SMU (mounted on a PXI-1085 Chassis). For most of the testing, VSENSE was set to 500 mV while VCOMP was set to 2 V. However, for FSW = 1 MHz, V COMPwas programmed to 1.7 V. For FSW = 2 MHz, VCOMP was programmed to 1.4 V, PS = SP = LEB = 20 kΩ and RSC = 15 kΩ. To minimize transient filtering on the OUTX and SRX signals, the only loading on the signals was due to the probes used to monitored these signals (approximately 11 pF). DCL pin was connected to GND through a 1-kΩ pull-down for all testing.

For SEL, SEB, and SEGR testing, the device was powered up to the maximum recommended operating voltage of 14 V. During the SEL testing the device was heated to 125°C by using a TDH35P10R0JE discrete power resistor soldered under the thermal vias on the bottom layer of the coupon card. Using a PXIe-4139 SMU, a current of 1.2 A was forced into the power resistor elevating the die temperature to 125°C. The temperature of the die was verified using thermal camera. During the SEL testing not a single current event was observed.

For the SEB/SEGR characterization, the device was tested under the Enabled and Disabled modes. For the SEB-OFF mode the device was disabled using the EN pin by forcing 100 mV (using CH 0 of a E36311A Keysight PS). When device was on, 5 V was forced to the EN pin. During the SEB and SEGR testing with the device in both the Enabled and Disabled mode, not a single OUTA (only trigger signal used) transient or input current event was observed.

For the SET characterization, the device was powered up to VIN of 4, 12, and 14 V (TPS7H5002/3/4-SP were characterized at 12 V only). Internal and external clocks were used for the validation. For the external clock, a PXIe-5433 AWG was used to provide a 1-MHz pulse clock with 50% duty cycle and 0-V (low level) to 5-V (high level) logic levels into the SYNC pin of the TPS7H5001-SP. During the external clock testing, the RT pin was left floating. Internal switching frequency of 1 MHz was used for the data collection. To characterize the transient performance of the error amp, the SENSE and COMP pins of the device were tied together to operate the amplifier on unity gain. As with the DSEE in which the device can be permanently damaged, the complementary operation of OUTX to SRX is mandatory in synchronous rectifier applications. Cross conduction was tested to check if a transient in critical logic of the TPS7H5001-SP resulting in a momentary non-complementary operation of outputs can occur by using an AND gate tied to OUTA and SRA. Not a single cross conduction upset was recorded during this testing. In addition to the OUTX and SRX, the SS and the VLDO were also characterized for SET.

The SET events were monitored using two National Instruments™ scopes and setup as described in the following:

- PXIe-5110 used to trigger from SRA or SRB using a outside pulse-width trigger at ±30%.

- PXIe-5162 used to trigger from SS using a negative-edge trigger at 600 mV.

In addition an Tektronix™ DPO7104C was used to trigger from OUTA, COMP, or the AND gate used for cross-conduction. Only one signal at a time was used as the trigger. For OUTA, an outside pulse-width trigger at ±30% was used. For the COMP signal, a window trigger at ±10% from the nominal (0.6 V) was used. For the AND gate, a positive-edge trigger at 2.5 V was used (AND gate was powered up at 5 V). For details on SET testing, see Section 8.

All equipment other than the DPO7104C was controlled and monitored using a custom-developed LabVIEW™ program (PXI-RadTest) running on a HP-Z4™ desktop computer. The computer communicates with the PXI chassis through an MXI controller and NI PXIe-8381 remote control module. The DPO7104C manufacturer interface was used. The DPO was set to fast-frame for all SET data collection.

Table 6-1 shows the connections, limits, and compliance values used during the testing. Figure 6-1 shows a block diagram of the setup used for SEE testing of the TPS7H5001-SP.

| Pin Name | Equipment Used | Capability | Compliance | Range of Values Used |

|---|---|---|---|---|

| VIN | NI-PXIe 4112 (CH 0) | 60 V, 1 A | 0.1 A | 4, 5, 7, 12, and 14 V |

| VCOMP | NI-PXIe 4139-1 (CH 0) | ±6 V, 0.5 A | 0.1 A | 1.4, 1.7, and 2 V |

| VSENSE | NI-PXIe 4139-2 (CH 1) | 0.5 V | ||

| EN | E36311A (CH 0) | 5 V, 5 A | 0.1 A | 100 mV, 5 V |

| Heater | NI-PXIe-4113 | 60 V, 3 A | 3 | 1.2 A |

| SRX | NI-PXIe-5110 | 1 GS/s | — | 100 MS/s |

| OUTX | DPO7104C | 40 GS/s | — | 2.5 and 5 GS/s |

| SS | PXIe-5162 | 1.5 GS/s | — | 2.5 MS/s |

All boards used for SEE testing were fully checked for functionality. Dry runs were also performed to make sure that the test system was stable under all bias and load conditions prior to being taken to the TAMU facility. During the heavy-ion testing, the LabVIEW control program powered up the TPS7H5001-SP device and set the external sourcing and monitoring functions of the external equipment. After functionality and stability was confirmed, the beam shutter was opened to expose the device to the heavy-ion beam. The shutter remained open until the target fluence was achieved (determined by external detectors and counters). During irradiation, the NI scope cards continuously monitored the signals. When the output pulse-width (OUTX and SRX) exceeded the pre-defined 30% pulse width trigger, a data capture was initiated. In addition to monitoring the time duration of the two scopes (OUTX and SRX), VIN current and the 5-V signal from TAMU were monitored at all times. No sudden increases in current were observed (outside of normal fluctuations) on any of the test runs and indicated that no SEL or SEB/SEGR events occurred during any of the tests.

Figure 6-1 Block Diagram of the SEE Test

Setup for the TPS7H5001-SP

Figure 6-1 Block Diagram of the SEE Test

Setup for the TPS7H5001-SP