SLVUC00 September 2020 – MONTH

6.1 On-Resistance (RON) Test Setup

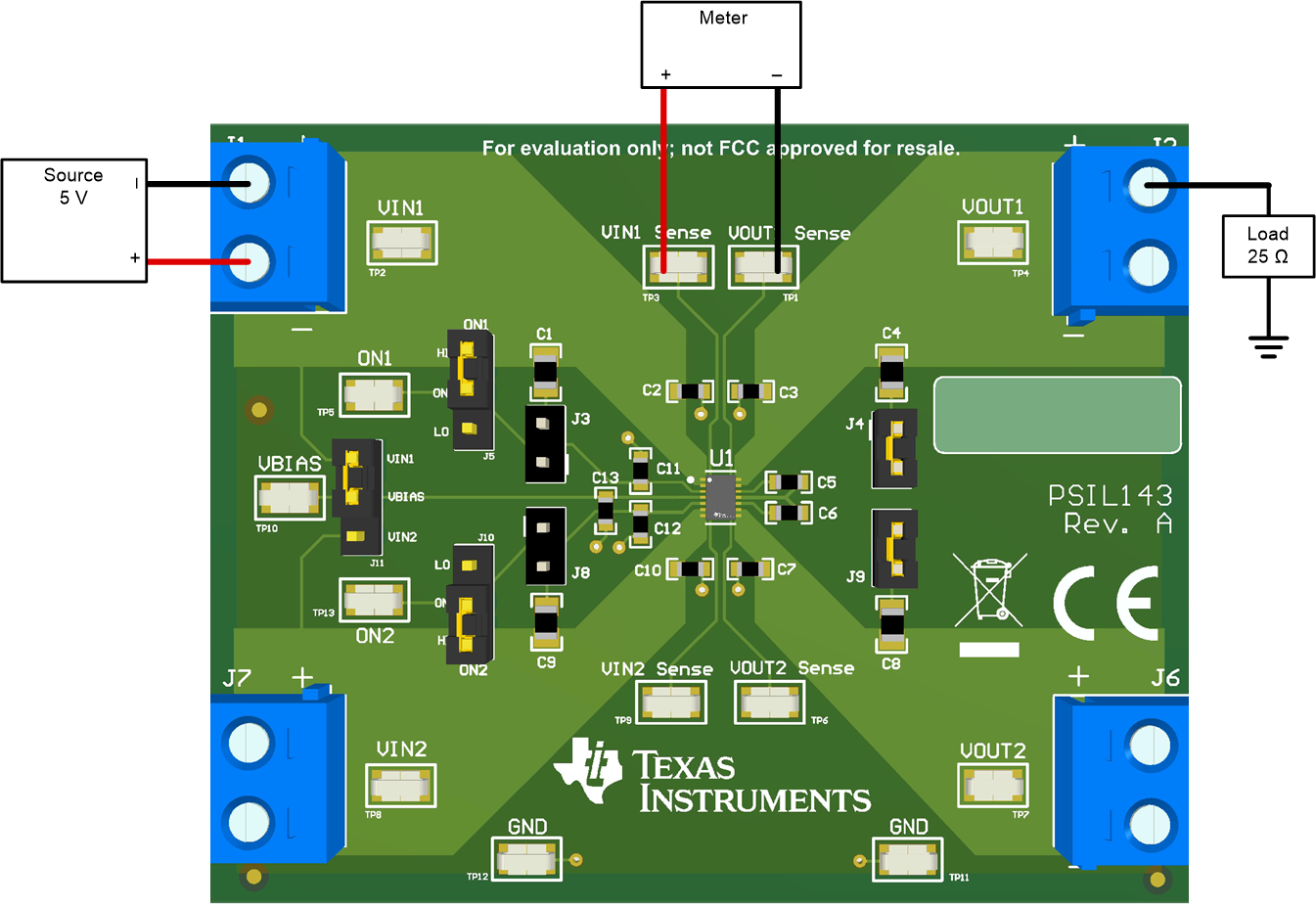

Figure 6-1 shows the typical setup for measuring on-resistance. Connect the desired VBIAS to the the VBIAS test point. It is recommended that VBIAS is greater than VIN for best on-resistance performance. The voltage drop across the switch is measured using the sense connections, and this can be divided by the load current to calculate the RON resistance.

Figure 6-1 RON Test Setup

Figure 6-1 RON Test Setup