SNVU543A November 2016 – December 2016 LM5170 , LM5170-Q1

-

LM5170-Q1 EVM User Guide

- Trademarks

- 1 Features and Electrical Performance

- 2 Setup

- 3 Test Procedure

- 4

Test Data

- 4.1 Efficiency

- 4.2 Current Regulation and Monitoring

- 4.3 Typical Master Enable Power Up and Shutdown

- 4.4 Channel Enable and Disable

- 4.5 Dual-Channel Interleaving Operation

- 4.6 ISETA Tracking

- 4.7 Diode Emulation Preventing Negative Currents

- 4.8 Dynamic DIR Change

- 4.9 Step Load Response

- 4.10 OVP

- 4.11 Output Short Circuit

- 5 Design Files

- Revision History

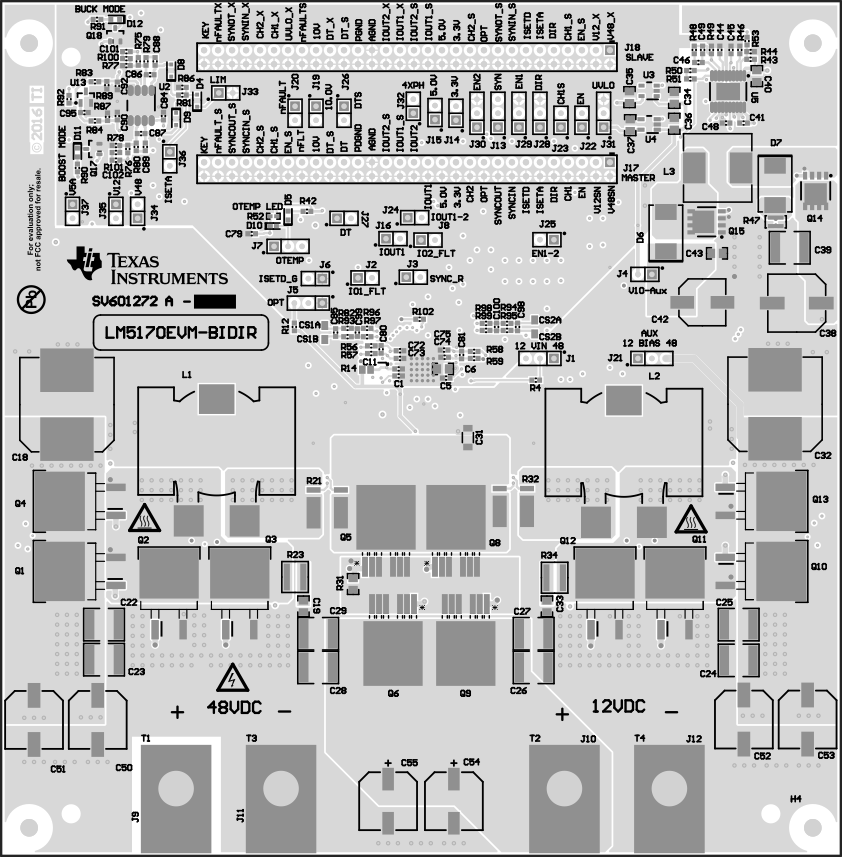

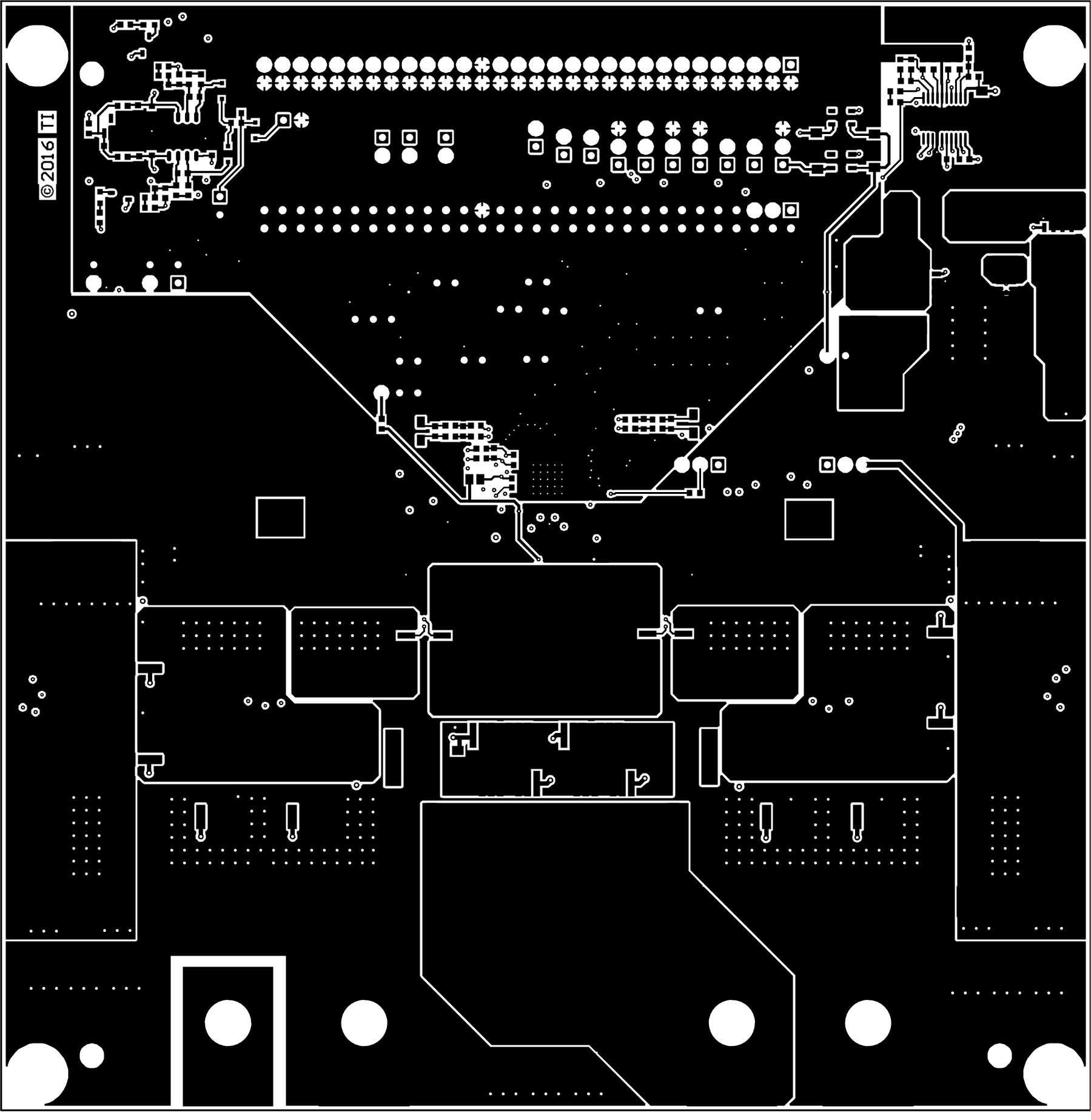

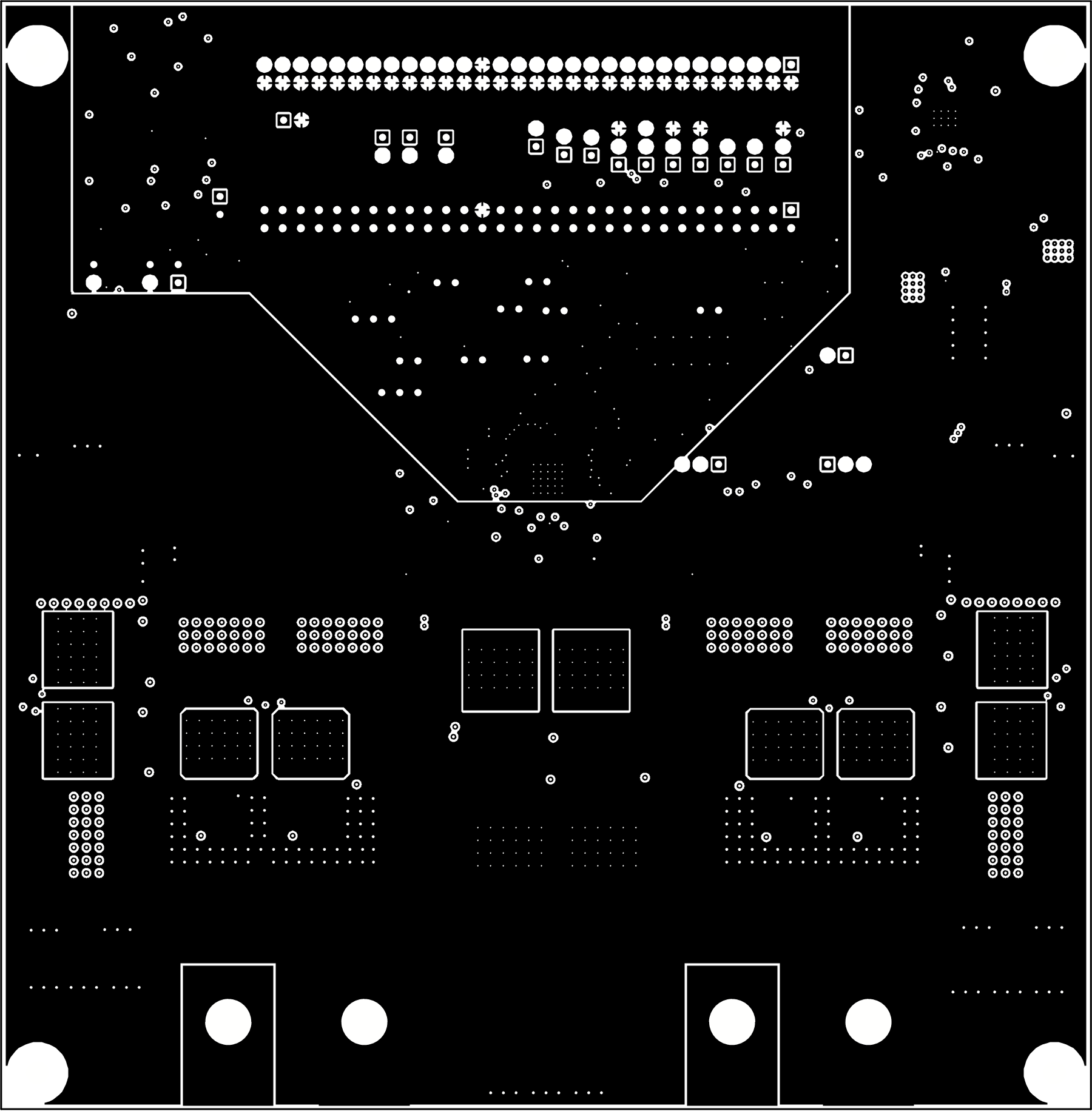

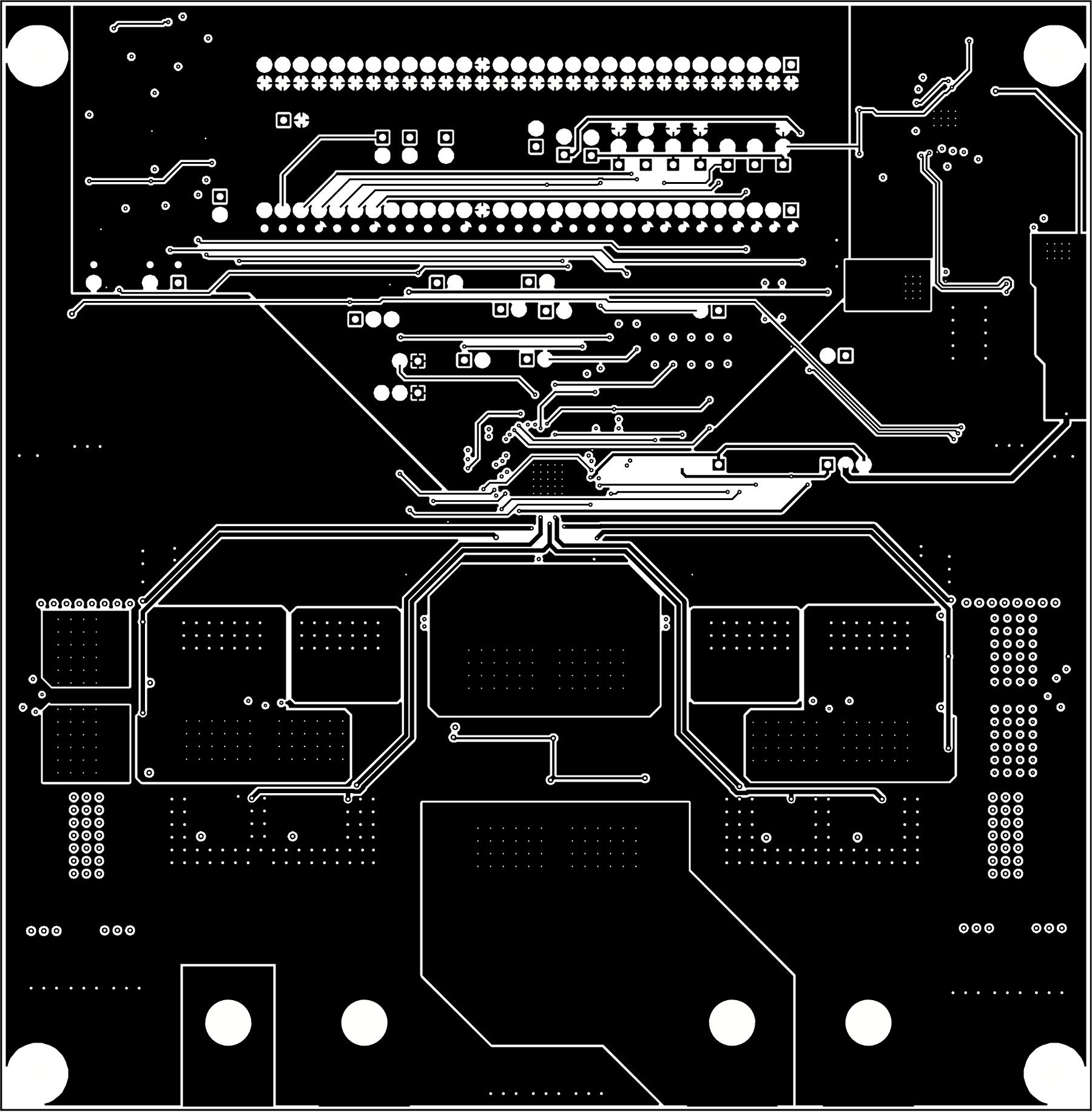

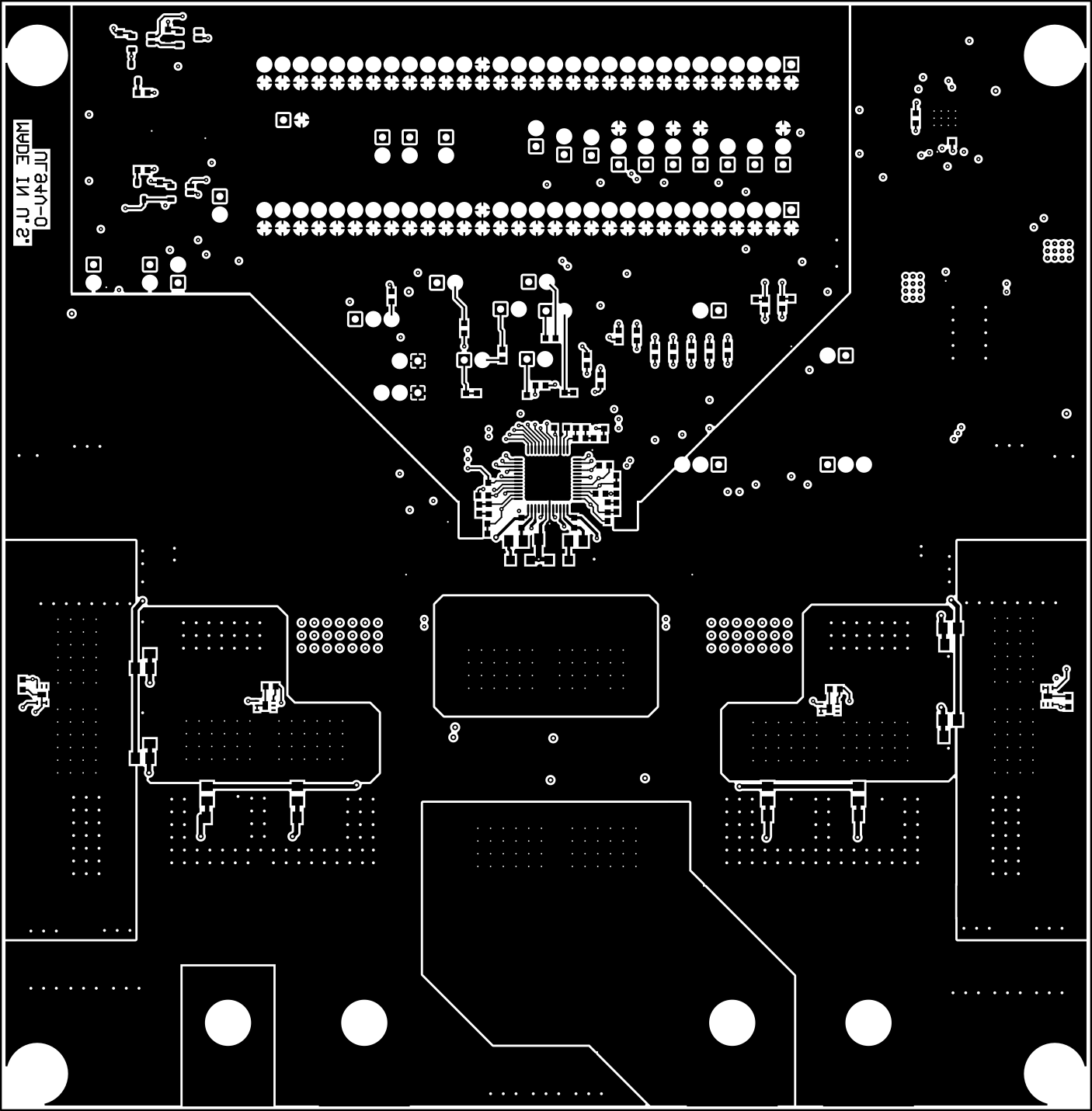

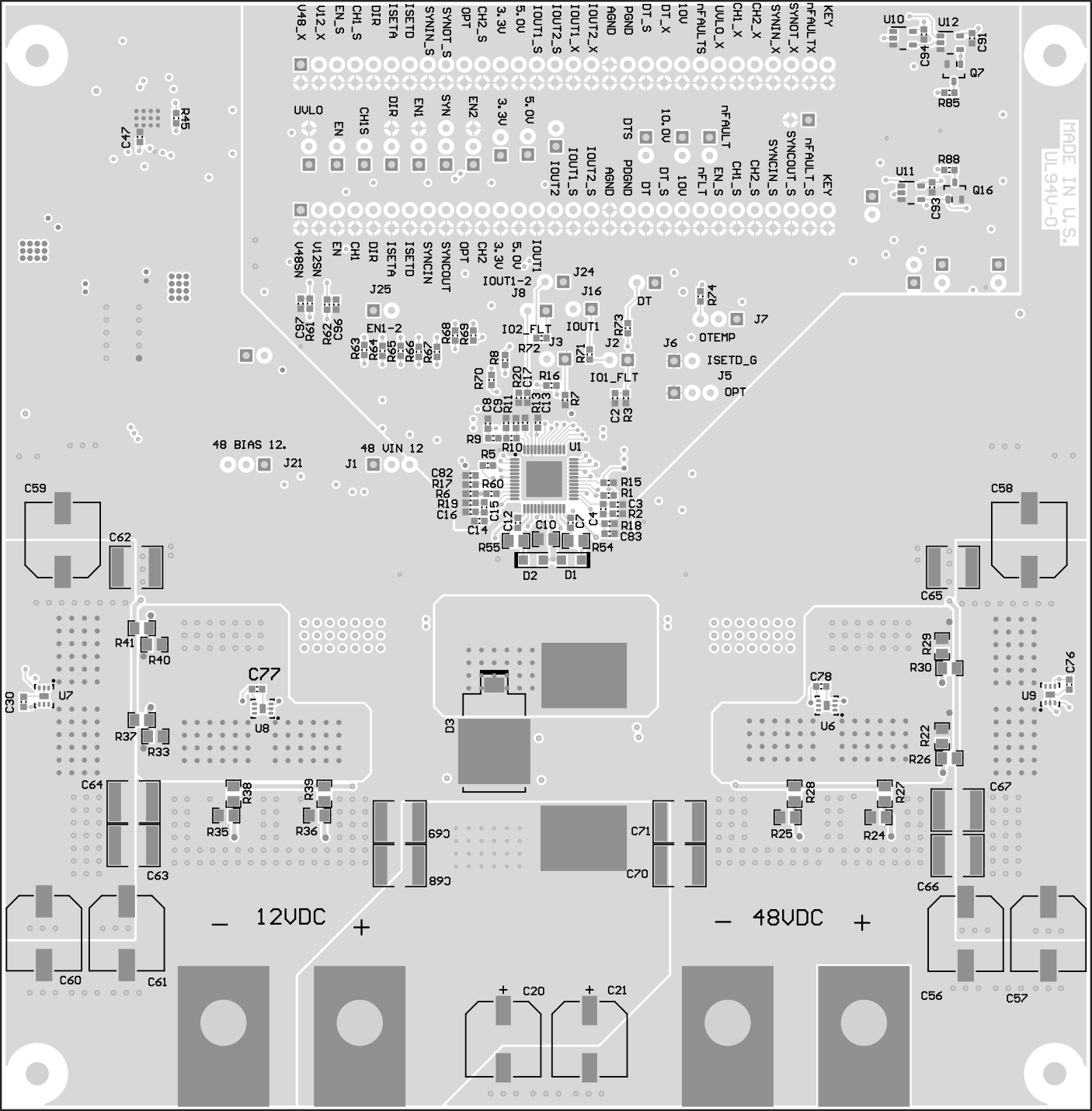

5.3 Board Layout

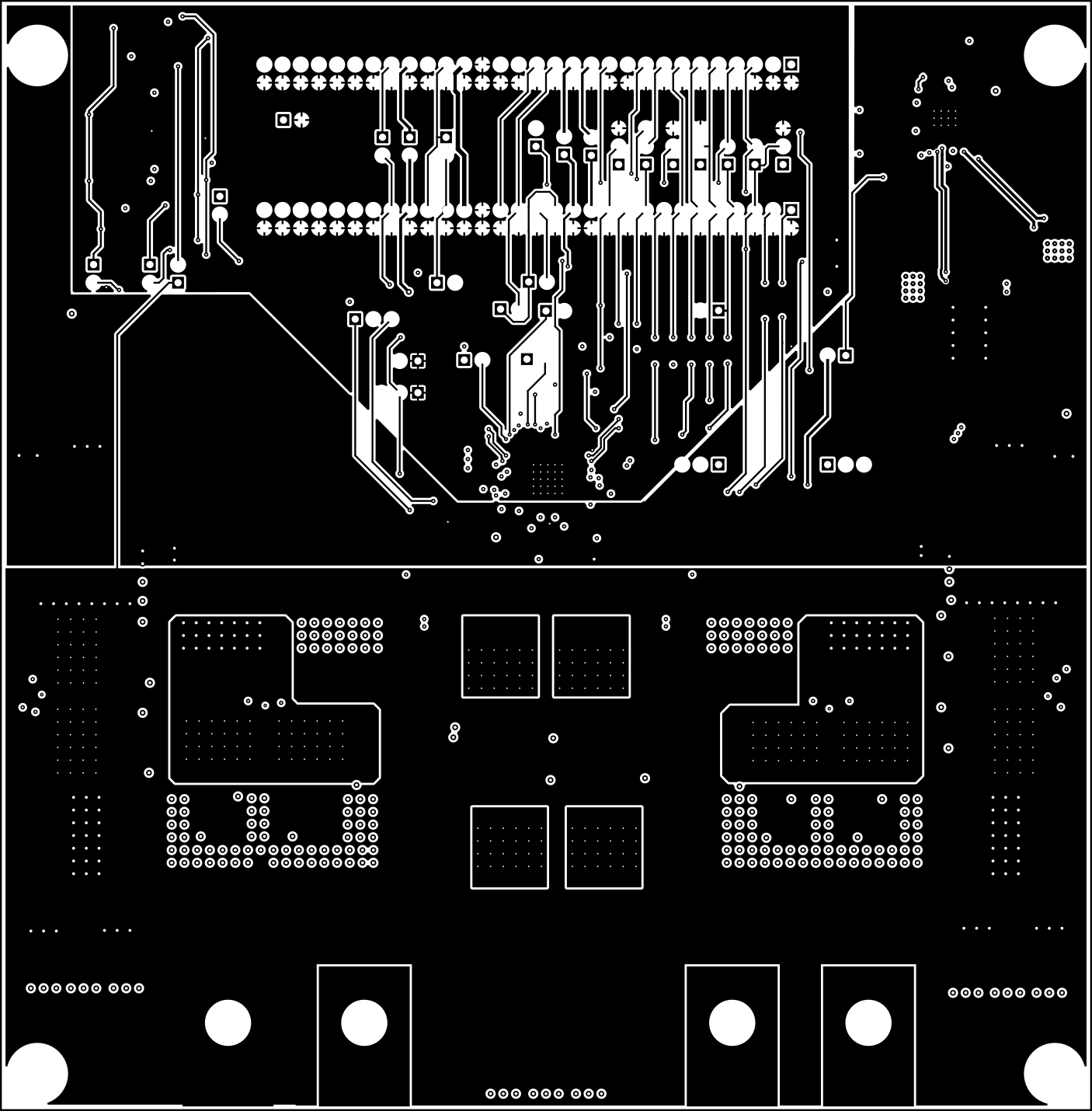

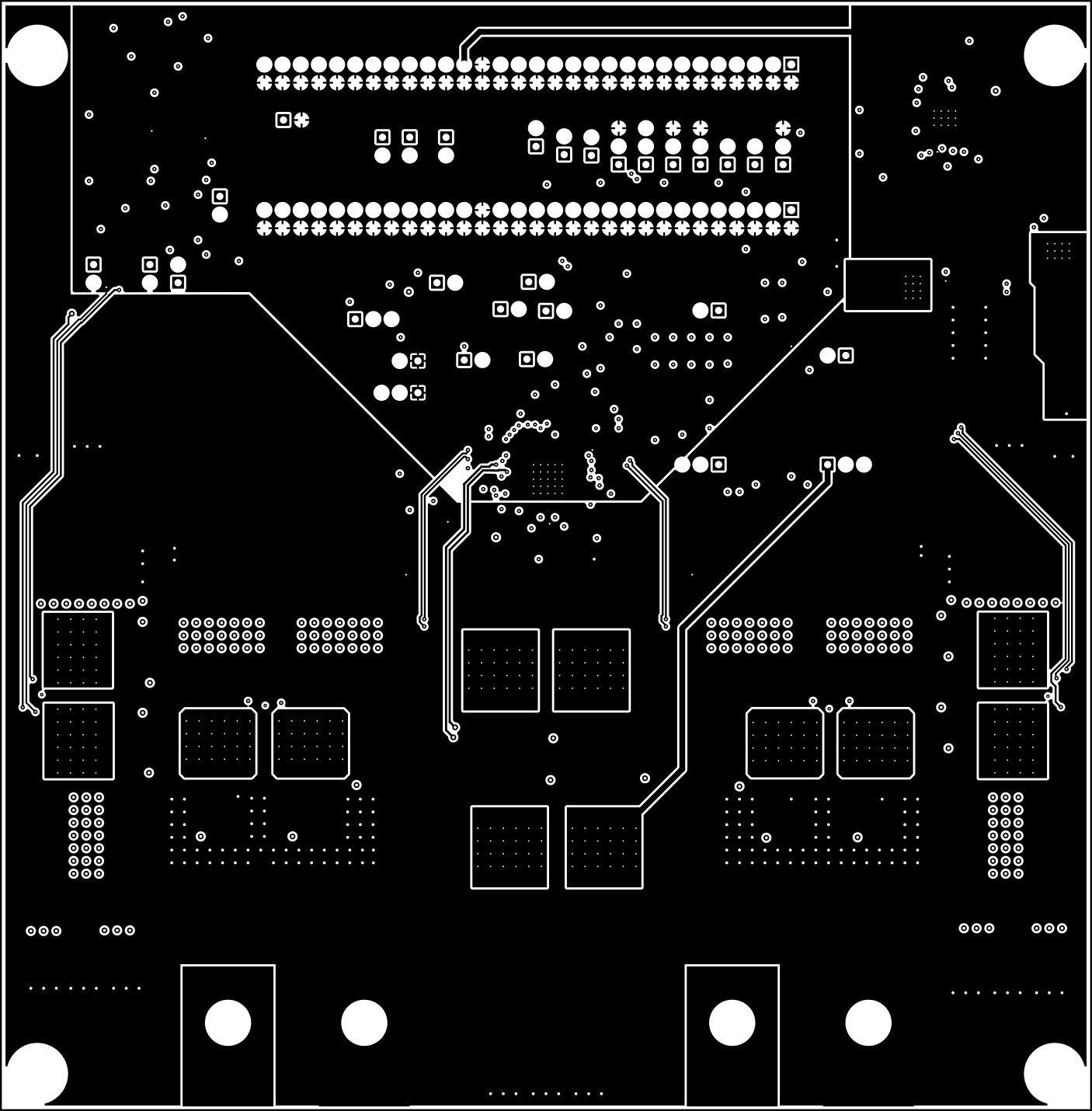

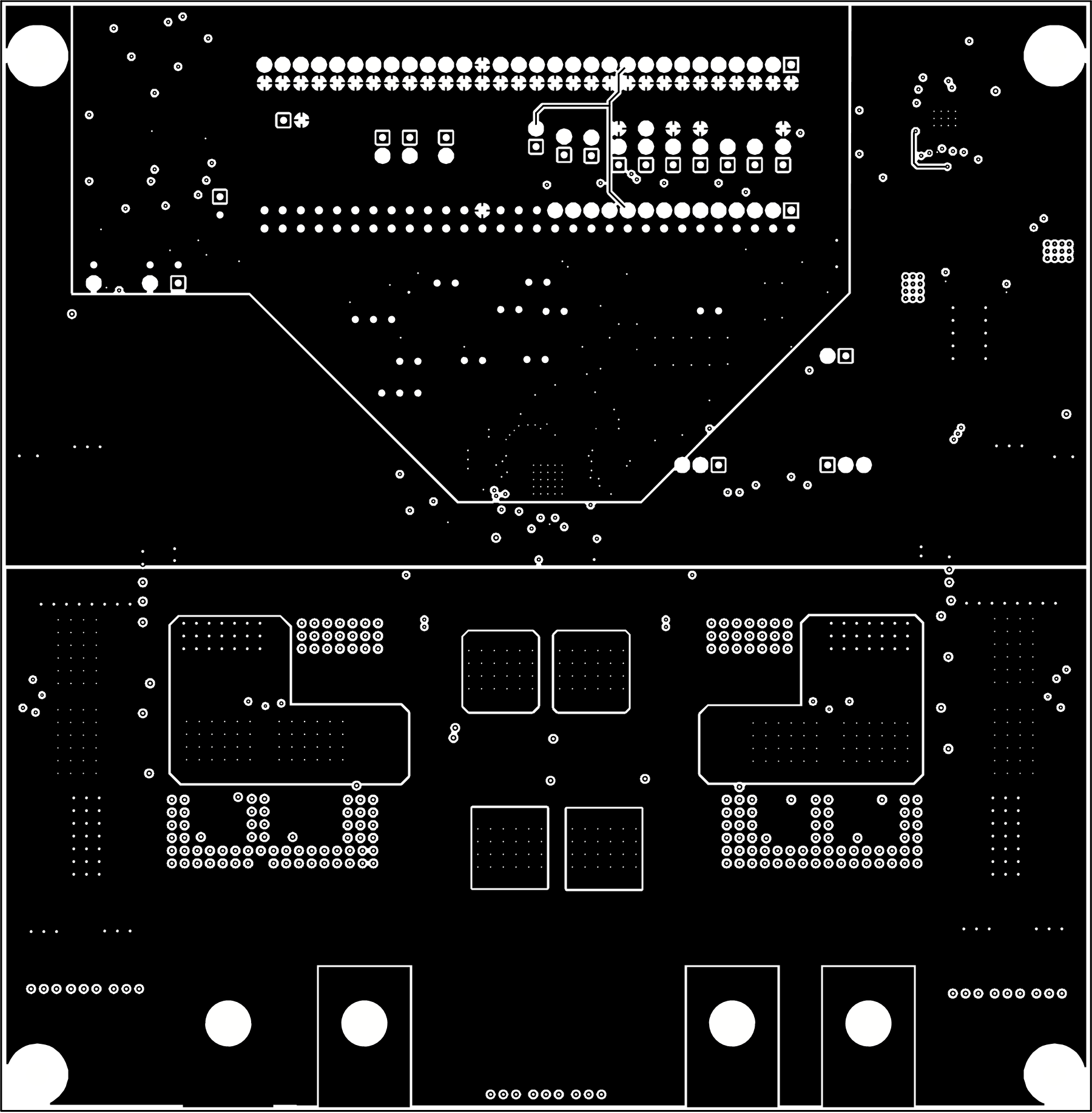

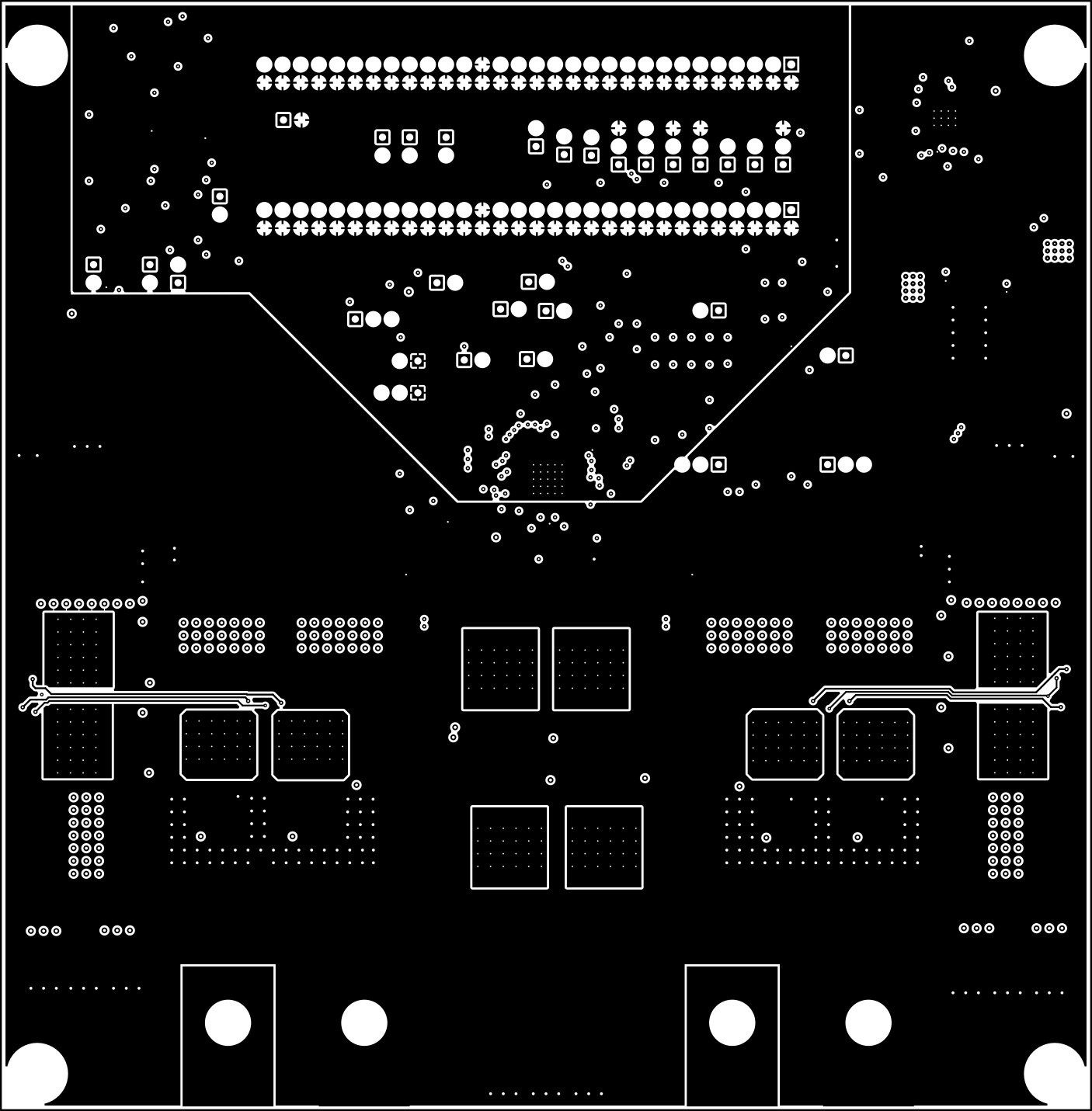

The EVM includes various headers for flexible configurations suitable for different applications. Figure 32 through Figure 41 show the EVM PCB artwork.

Figure 32. EVM Top Layer Silkscreen

Figure 32. EVM Top Layer Silkscreen  Figure 33. EVM Top Layer Copper

Figure 33. EVM Top Layer Copper  Figure 34. EVM Middle Layer 1

Figure 34. EVM Middle Layer 1  Figure 35. EVM Middle Layer 2

Figure 35. EVM Middle Layer 2  Figure 36. EVM Middle Layer 3

Figure 36. EVM Middle Layer 3  Figure 37. EVM Middle Layer 4

Figure 37. EVM Middle Layer 4  Figure 38. EVM Middle Layer 5

Figure 38. EVM Middle Layer 5  Figure 39. EVM Middle Layer 6

Figure 39. EVM Middle Layer 6  Figure 40. EVM Bottom Layer Copper

Figure 40. EVM Bottom Layer Copper  Figure 41. EVM Bottom Layer Silkscreen

Figure 41. EVM Bottom Layer Silkscreen