SPRAC21A June 2016 – June 2019 OMAP-L132 , OMAP-L138 , TDA2E , TDA2EG-17 , TDA2HF , TDA2HG , TDA2HV , TDA2LF , TDA2P-ABZ , TDA2P-ACD , TDA2SA , TDA2SG , TDA2SX , TDA3LA , TDA3LX , TDA3MA , TDA3MD , TDA3MV

-

TDA2xx and TDA2ex Performance

- Trademarks

- 1 SoC Overview

- 2 Cortex-A15

- 3 System Enhanced Direct Memory Access (System EDMA)

- 4 DSP Subsystem EDMA

- 5 Embedded Vision Engine (EVE) Subsystem EDMA

- 6 DSP CPU

- 7 Cortex-M4 (IPU)

- 8 USB IP

- 9 PCIe IP

- 10 IVA-HD IP

- 11 MMC IP

- 12 SATA IP

- 13 GMAC IP

- 14 GPMC IP

- 15 QSPI IP

- 16 Standard Benchmarks

- 17

Error Checking and Correction (ECC)

- 17.1 OCMC ECC Programming

- 17.2 EMIF ECC Programming

- 17.3 EMIF ECC Programming to Starterware Code Mapping

- 17.4 Careabouts of Using EMIF ECC

- 17.5 Impact of ECC on Performance

- 18 DDR3 Interleaved vs Non-Interleaved

- 19 DDR3 vs DDR2 Performance

- 20 Boot Time Profile

- 21 L3 Statistics Collector Programming Model

- 22 Reference

- Revision History

14.1.2.2 Asynchronous NOR Flash Single Read

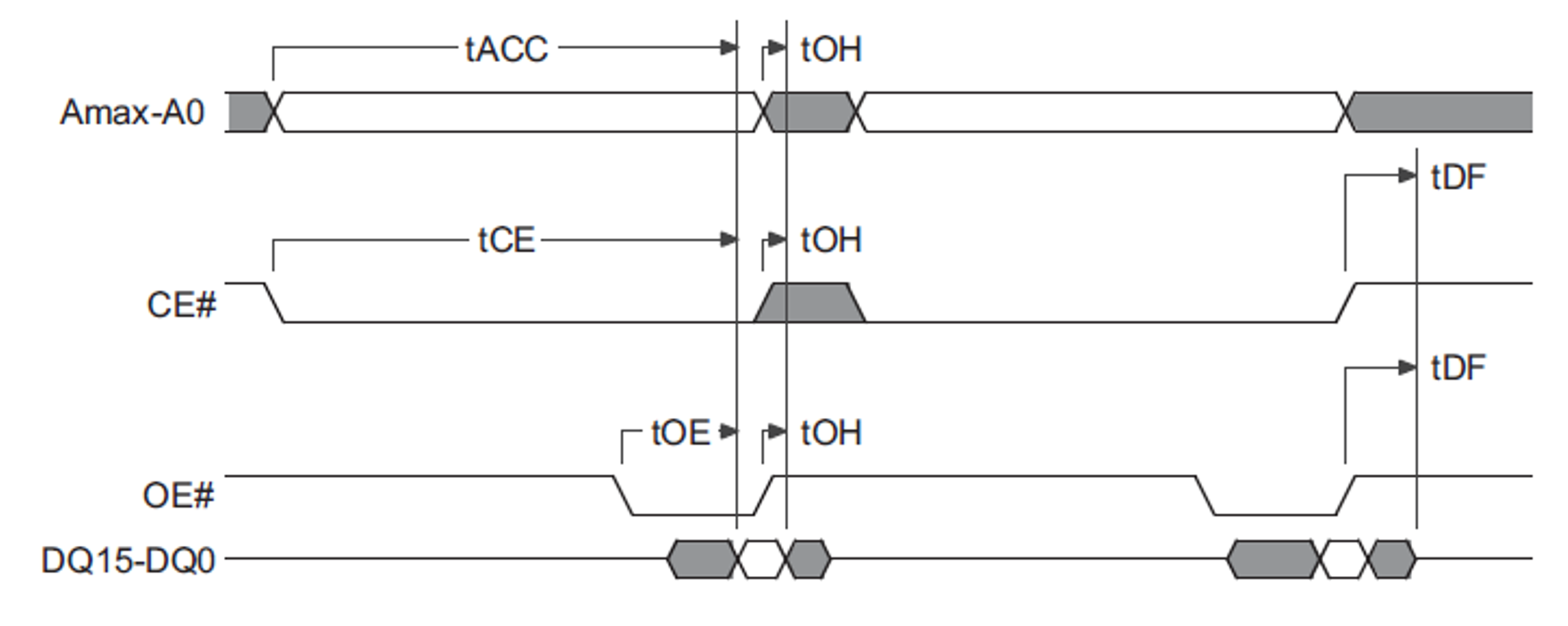

Address access time (tACC) is equal to the delay from stable addresses to valid output data The chip enable access time (tCE) is the delay from stable CE# to valid data at the outputs. In order for the read data to be driven on to the data outputs, the OE# signal must be low for at least the output enable time (tOE) before valid data is available.

Figure 34 shows the read operation timing diagram at the Flash.

Figure 34. Back-to-Back Read (tACC) Operation Timing Diagram

Figure 34. Back-to-Back Read (tACC) Operation Timing Diagram Figure 35 shows the read operation timing diagram with GPMC signal parameters.

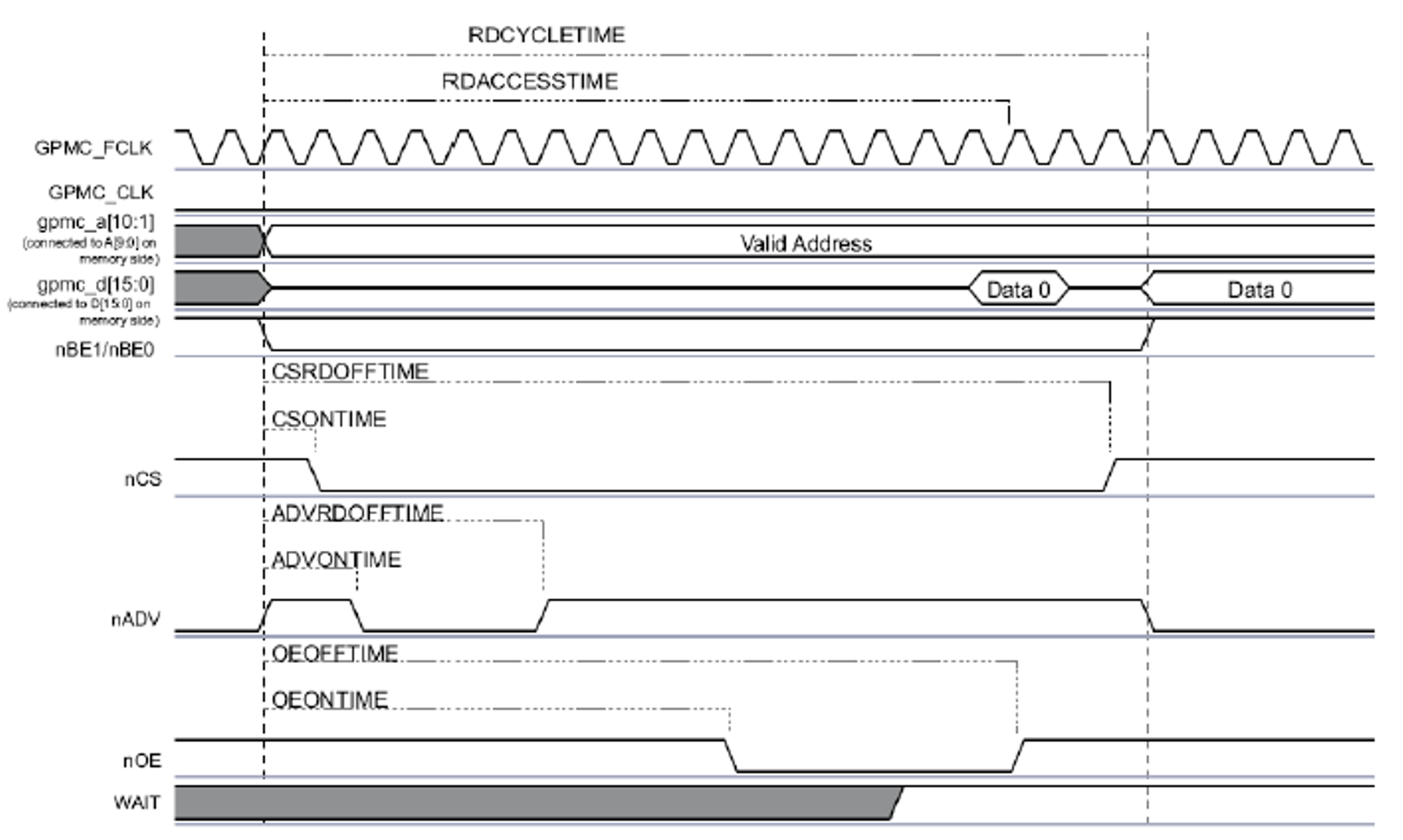

Figure 35. Asynchronous Single Read Timing Parameters

Figure 35. Asynchronous Single Read Timing Parameters For the successful read operation to occur, GPMC timing parameters have to be set satisfying the Flash level timing values. Table 53 shows the optimum configuration for GPMC timing values for successful read operation. 1 GPMC clock =~ 3.7 ns. Here “Timeparagranularity” is set as 0x1, which will multiply the configured timing values by 2.

Table 53. Optimum Configuration for GPMC for Reads of NOR Flash Single Read

| Signal | Parameter | Description | Value Programmed |

|---|---|---|---|

| Read op | RDACCESSTIME | Address latch + Initial access time = 0ns + 110ns =

30 GPMC clock cycles |

0x0F |

| RDCYCLETIME | RDACCESSTIME + Data holding + tDF = 30 + 4 + 4 =

38 GPMC clock cycles |

0x13 | |

| nCS | CSONTIME | Assert after address latch | 0x00 |

| CSRDOFFTIME | RDACCESSTIME + Data holding = 30 + 4 = 34 GPMC clock cycles | 0x11 | |

| nADV | ADVONTIME | Immediate assert with read cycle | 0x00 |

| ADVOFFTIME | Provide ADV assertion duration of 2 cycles | 0x01 | |

| nOE | OEONTIME | Assert after address latch | 0x00 |

| OEOFFTIME | RDACCESSTIME + Dataholding | 0x11 |