SPRAD64 November 2022 AM620-Q1 , AM623 , AM625 , AM625-Q1

8 SerDes Interfaces

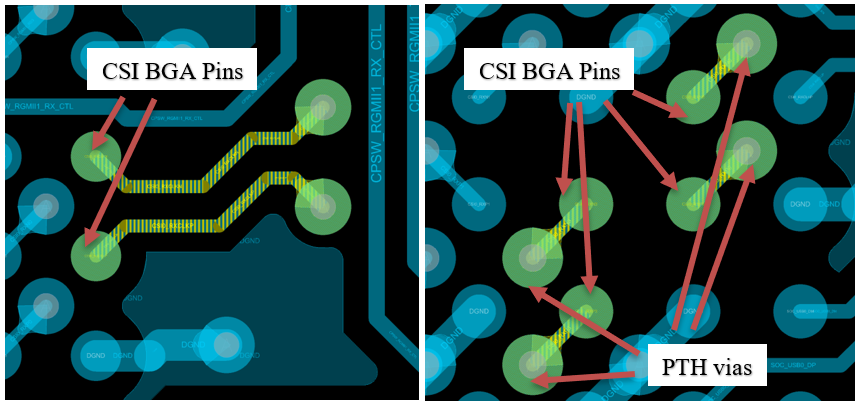

The package BGA ball map is also arranged to support routing the highest priority interfaces first. Therefore, the SerDes CSI interfaces are located close to the outer rings. The lanes located on the outermost row of BGAs can be escaped on the top layer. The lanes located on inner BGA rows require vias to escape as a differential pair on the bottom or on an interior layer. The BGA map facilitates this for inner rows. See Figure 8-1 for an example of the SerDes signals on the AM62x AMC board on the top layer and on an inner layer. Wide traces can limit the signal loss but could violate the impedance requirements. For more detailed information on routing Serdes signals, refer to High-Speed Interface Layout Guidelines.

Figure 8-1 Serdes CSI Escapes for TOP layer (Left) and Inner layer (Right)

Figure 8-1 Serdes CSI Escapes for TOP layer (Left) and Inner layer (Right)