SPRADD8 November 2024 F29H850TU , F29H859TU-Q1

- 1

- Abstract

- Trademarks

- 1Introduction to Real-Time Control

- 2C29 CPU and Key Features

- 3C29 Performance Benchmarks

- 4Summary

- 5References

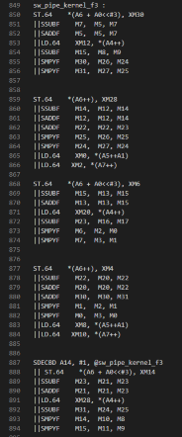

3.2.1.4 Software Pipelining

Software pipelining of loops allows multiple iterations of loops to execute in parallel, leveraging the VLIW architecture of the C29 CPU. In Figure 3-7, software pipelining is illustrated for the CFFT. The assembly is hand-written, where the complete 128-bit instruction packet is used and 8 instructions are executed in parallel per cycle in the loop.

Figure 3-7 Software Pipelining in CFFT -

Handwritten Assembly.

Figure 3-7 Software Pipelining in CFFT -

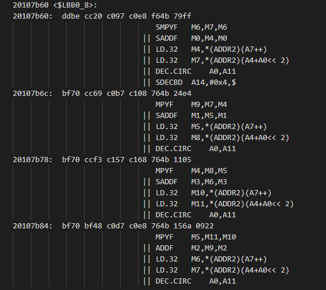

Handwritten Assembly. With -O3 optimization, the C29 compiler generates software pipelined loops, as shown in Figure 3-8, for the FIR. Software pipelining allows loops to perform faster.

Figure 3-8 Software Pipelining in FIR -

Compiler Generated.

Figure 3-8 Software Pipelining in FIR -

Compiler Generated. The compiler generates software pipelined loops at -O3 optimization setting that boosts performance for code with loops.