SPRUJ51 june 2023

- 1

- 1Abstract

- 2EVM Revisions and Assembly Variants

- Trademarks

-

3System Description

- 3.1 Key Features

- 3.2 Functional Block Diagram

- 3.3 AM62x-Low Power SK EVM Interface Mapping

- 3.4 Power ON OFF Procedures

- 3.5

Peripheral and Major Component Description

- 3.5.1 Clocking

- 3.5.2 Reset

- 3.5.3 OLDI Display Interface

- 3.5.4 CSI Interface

- 3.5.5 Audio Codec Interface

- 3.5.6 HDMI Display Interface

- 3.5.7 JTAG Interface

- 3.5.8 Test Automation Header

- 3.5.9 UART Interface

- 3.5.10 USB Interface

- 3.5.11 Memory Interfaces

- 3.5.12 Ethernet Interface

- 3.5.13 GPIO Port Expander

- 3.5.14 GPIO Mapping

- 3.5.15 Power

- 3.5.16 AM62x-Low Power SK EVM User Setup and Configuration

- 3.5.17 Expansion Headers

- 3.5.18 Push Buttons

- 3.5.19 I2C Address Mapping

- 4Known Issues and Modifications

- 5Revision History

- 6IMPORTANT NOTICE AND DISCLAIMER

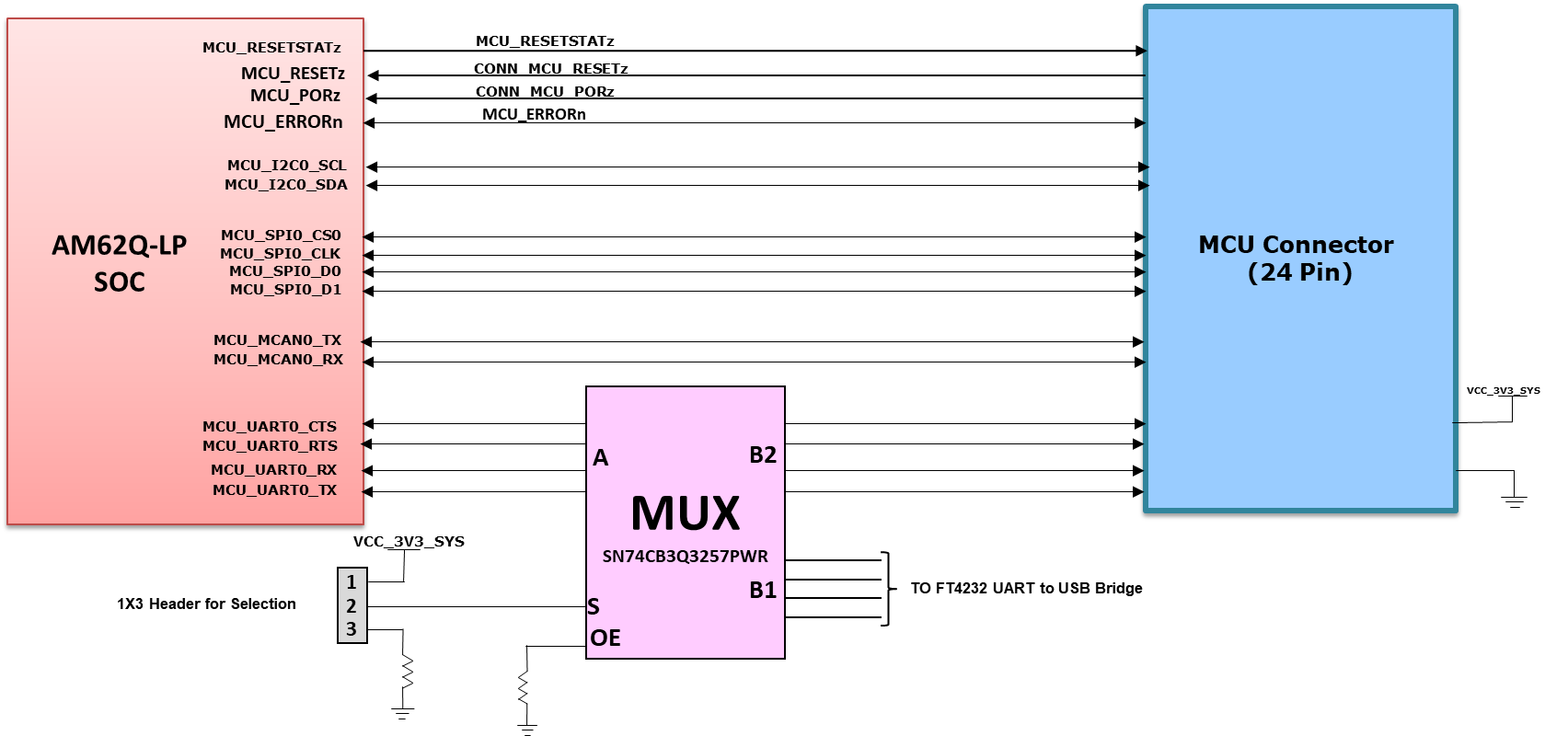

3.5.17.2 MCU Connector

The AM62x-Low Power SK EVM has a 14x2 standard 0.1 spaced MCU connector which includes signals connected to the MCU Domain of SoC. 13 Signals include MCU_I2C0, MCU_UART0 (with flow control), MCU_SPI0 and MCU_MCAN0 signals are connected to the MCU Header. Additional control signals provided on the Header include CONN_MCU_RESETz, CONN_MCU_PORz, MCU_RESETSTATz, MCU_SAFETY_ERRORn, 3.3V IO and GND. MCU_UART0 signals from AM62x SoC are connected to both MCU Header and FT4232 Bridge through MUX Mfr Part # SN74CB3Q3257PWR. The MCU Header does not include the Board ID memory interface. Allowed current limit is 100mA on 3.3V rail.

Figure 3-28 MCU Connector Interface

Figure 3-28 MCU Connector Interface| Pin No. | SoCBall No. | Netname |

| 1 | - | VCC_3V3_SYS |

| 2 | - | DGND |

| 3 | - | DGND |

| 4 | D8 | MCU_SPI0_D1 |

| 5 | - | CAN_FD_WKUP_HDR_INH |

| 6 | E8 | MCU_SPI0_D0 |

| 7 | - | DGND |

| 8 | C8 | MCU_SPI0_CS1 |

| 9 | - | DGND |

| 10 | D5 | MCU_GPIO0_15 |

| 11 | D6 | MCU_GPIO0_16 |

| 12 | B8 | MCU_UART0_CTS_CONN |

| 13 | A8 | MCU_UART0_RXD_CONN |

| 14 | - | DGND |

| 15 | - | DGND |

| 16 | C5 | MCU_MCAN0_TX |

| 17 | D7 | MCU_UART0_RTS_CONN |

| 18 | B7 | MCU_SPI0_CLK |

| 19 | B6 | MCU_UART0_TXD_CONN |

| 20 | - | DGND |

| 21 | A10 | MCU_I2C0_SDA |

| 22 | C4 | MCU_MCAN0_RX |

| 23 | A12 | MCU_RESETSTATz |

| 24 | B9 | MCU_I2C0_SCL |

| 25 | - | CONN_MCU_RESETz |

| 26 | - | MCU_SAFETY_ERRORz_3V3 |

| 27 | - | DGND |

| 28 | - | CONN_MCU_PORz |