SPRUJ51 june 2023

- 1

- 1Abstract

- 2EVM Revisions and Assembly Variants

- Trademarks

-

3System Description

- 3.1 Key Features

- 3.2 Functional Block Diagram

- 3.3 AM62x-Low Power SK EVM Interface Mapping

- 3.4 Power ON OFF Procedures

- 3.5

Peripheral and Major Component Description

- 3.5.1 Clocking

- 3.5.2 Reset

- 3.5.3 OLDI Display Interface

- 3.5.4 CSI Interface

- 3.5.5 Audio Codec Interface

- 3.5.6 HDMI Display Interface

- 3.5.7 JTAG Interface

- 3.5.8 Test Automation Header

- 3.5.9 UART Interface

- 3.5.10 USB Interface

- 3.5.11 Memory Interfaces

- 3.5.12 Ethernet Interface

- 3.5.13 GPIO Port Expander

- 3.5.14 GPIO Mapping

- 3.5.15 Power

- 3.5.16 AM62x-Low Power SK EVM User Setup and Configuration

- 3.5.17 Expansion Headers

- 3.5.18 Push Buttons

- 3.5.19 I2C Address Mapping

- 4Known Issues and Modifications

- 5Revision History

- 6IMPORTANT NOTICE AND DISCLAIMER

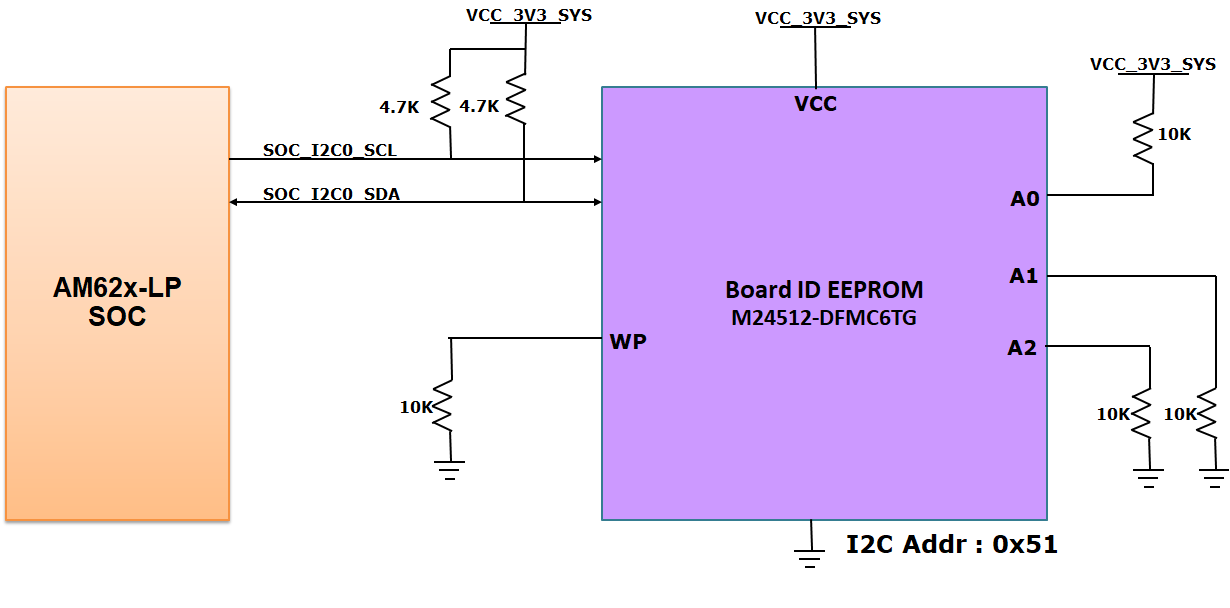

3.5.11.4 EEPROM

AM62x-Low Power SK EVM boards are identified by its version and serial number, which are stored on the onboard EEPROM. The EEPROM is accessible from AM62x 17x17 SoC I2C0 port.

The Board ID EEPROM I2C address is set to 0x51. The AM62x-Low Power SK EVM includes an M24512-DFMC6TG 512kb EEPROM. The first 259 bytes of memory are preprogrammed with identification information for each board. The remaining 65277 bytes are available to the user for data or code storage.

Figure 3-23 Board ID EEPROM Interface

Block Diagram

Figure 3-23 Board ID EEPROM Interface

Block Diagram