SPRUJ69 December 2022 AM68 , AM68A , TDA4AL-Q1 , TDA4VE-Q1 , TDA4VL-Q1

- Trademarks

- 1Introduction

-

2User Interfaces

- 2.1 Power Inputs

- 2.2 Power Input [J7_CP] with LED for Status [LD2_CP][LD3_CP]

- 2.3 User Inputs

- 2.4

Standard Interfaces

- 2.4.1 Uart-Over-USB [J43_CP] [J44_CP] with LED for Status [LD10_CP] [LD11_CP]

- 2.4.2 Gigabit Ethernet [J35_CP] with Integrated LEDs for Status

- 2.4.3 USB3.1 Gen1 Interface [J5_CP]

- 2.4.4 USB2.0 Interface [J6_CP]

- 2.4.5 PCIe Card Slot [J8_CP]

- 2.4.6 Display Port Interfaces [J36_CP] [J37_CP]

- 2.4.7 MicroSD Card Cage [J49_CP]

- 2.4.8 Stereo Audio Interface [LINE-IN J38_CP, LINE-OUT J41B_CP, J40B_CP]

- 2.5 Expansion Interfaces

- 3Circuit Details

- 4Revision History

2 User Interfaces

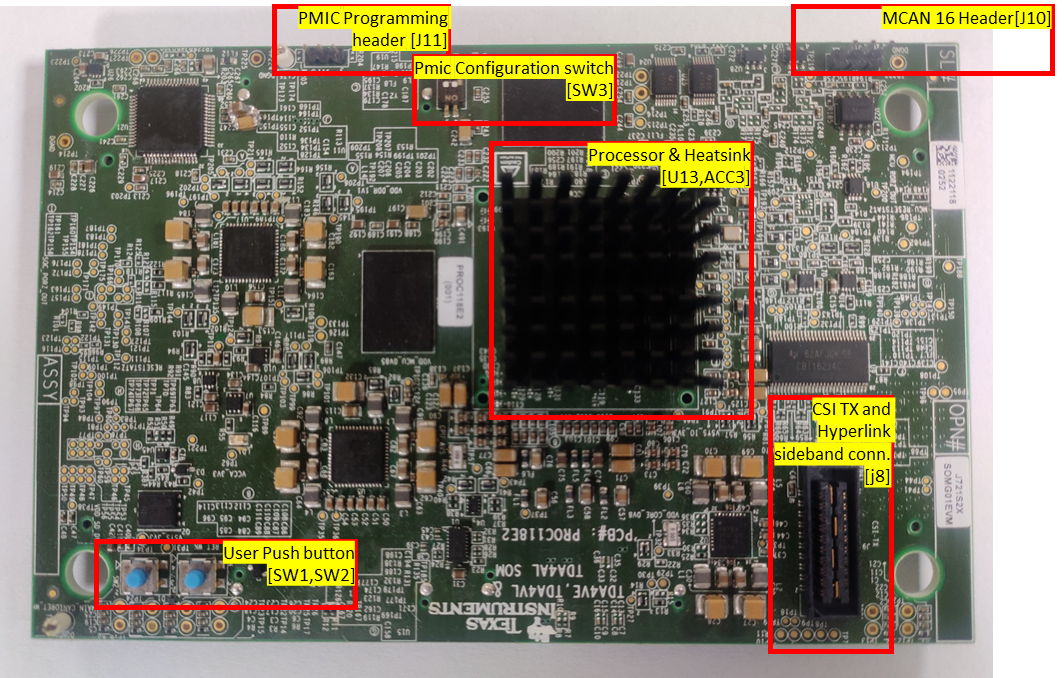

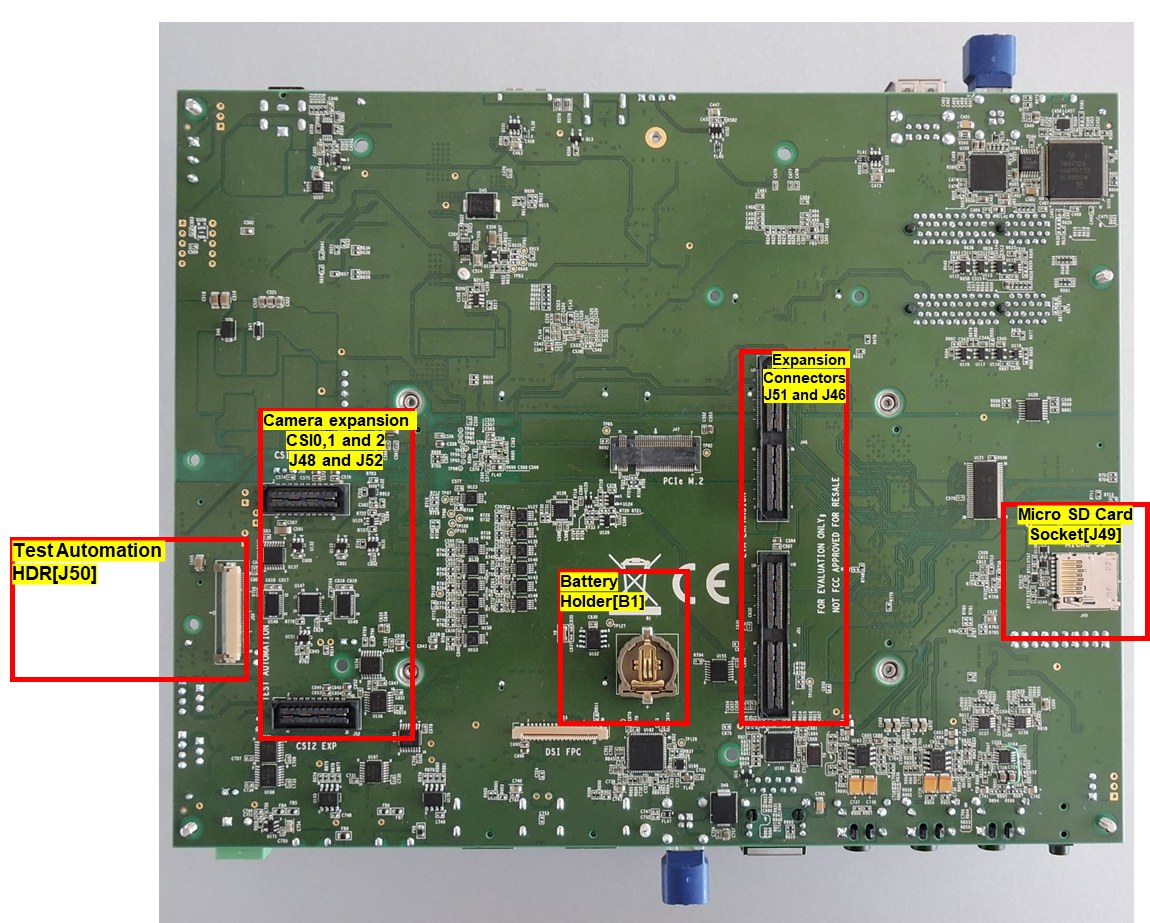

Figure 2-1 and Figure 2-2 identify the key user interfaces on the EVM (top and bottom view).

Figure 2-1 TDA4VE-Q1/TDA4VL-Q1/TDA4AL-Q1

System on Module Component Identification

Figure 2-1 TDA4VE-Q1/TDA4VL-Q1/TDA4AL-Q1

System on Module Component Identification

Figure 2-2 Jacinto7 Common Processor Component Identification

Figure 2-2 Jacinto7 Common Processor Component IdentificationBecause the Jacinto7 Common Processor board is used with different SOM boards featuring different Jacinto7 processors with different feature sets, some of the board’s peripherals/interfaces may not be supported.