SSZT176 april 2021 TPS7A4501-SP , TPS7H1101A-SP

Radiation-hardened low-dropout regulators (LDOs) are vital power components of many space-grade subsystems, including field-programmable gate arrays (FPGAs), data converters and analog circuitry. LDOs help ensure a stable, low-noise and low-ripple supply of power for components whose performance depends on a clean input.

But with so many LDOs available on the market, how do you choose the right radiation-hardened device for your subsystem? Let’s look at some design specifications and device features to help you with this decision.

Dropout Voltage for Space-grade LDOs

An LDO’s dropout voltage is the voltage differential between the input and output voltage, at which point the LDO ceases to regulate the output voltage. The smaller the dropout voltage specification, the lower the operating voltage differential one is able to operate with, which results in less power and thermal dissipation as well as inherently higher maximum efficiency. These benefits become more significant at higher currents, as expressed by Equation 1:

LDO power dissipation = (VIN-VOUT)xIOUT (1)

In the radiation-hardened market, it can be difficult to find truly low dropout regulators that offer strong performance over radiation, temperature and aging. TI’s radiation-hardened LDO, the TPS7H1101A-SP, is one example, offering a typical dropout voltage (Vdo) of 210 mV at 3 A – currently, the lowest on the market. If you have a standard 5-V, 3.3-V, 2.5-V or 1.8-V rail available, this LDO can regulate output voltages down to 0.8 V to supply any required voltage, as well as the current needed for one or more space-grade analog-to-digital converters (ADCs) or clocks.

Noise Performance for Space LDOs

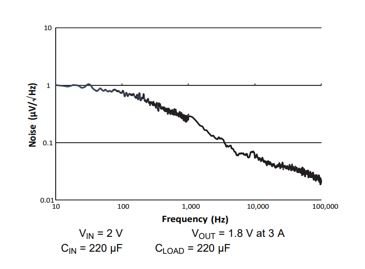

With satellites in space for 10 or more years, getting the maximum performance out of the onboard integrated circuits helps ensure design longevity. In order to provide a clean, low-noise rail for high-performance clocks, data converters, digital signal processors or analog components, the internal noise generated by the LDO’s circuitry needs to be minimal. Since it is not easy to filter internally generated 1/f noise, look for LDOs with inherent low-noise characteristics. Lower-frequency noise is often the largest and most difficult to filter out. The TPS7H1101A-SP offers one of the lowest 1/f noise levels, with a peak around 1 µV/√Hz at 10 Hz. See Figure 1 below for RMS noise over frequency.

Figure 1 TPS7H1101A-sp Noise

Figure 1 TPS7H1101A-sp NoisePSRR for Space LDOs

The power-supply rejection ratio (PSRR) is a measure of how well an LDO can clean up, or reject, incoming noise from other components upstream. For higher-end ADCs, the input supply noise requirements continue to get tighter to minimize bit errors. At higher frequencies, it is difficult to have high PSRR given the characteristics of the control loop. Often, designers need to use external components to filter the noise to reach an acceptable effective PSRR, which increases solution size – an obvious issue for space applications, where size and weight tie directly to satellite launch costs. The PSRR is most important at the switching frequency of the upstream supply (since there is a voltage ripple at this frequency). Additionally, PSRR is important above this frequency because of the switching harmonics. If you’re looking for good PSRR, the TPS7A4501-SP LDO offers a PSRR of over 45 dB at 100 kHz.

Other Important LDO Features

- Enable. In space, there is only a set amount of power available from the solar panel, from which many functions need to run. The enable feature allows you to specify whether the LDO should be on or off at any given time, and proves critical for overall savings in a power budget. The enable pin is also important for power-up sequencing, which is of increasing need in newer-generation FPGAs.

- Soft start. A voltage that rises too quickly can cause current overshoot or an excessive peak inrush current, damaging downstream components such as the FPGA or ADC. The soft-start feature regulates how quickly the output voltage rises at startup. Soft start also prevents a level of voltage droop that could be unacceptable by preventing an overcurrent draw on the upstream supply.

- Output voltage accuracy. Often, newer space-grade FPGAs such as the Xilinx KU060 have strict input-voltage tolerance requirements on each rail to enable their best performance. To ensure that your design meets strict accuracy requirements over radiation exposure and end-of-life conditions, look for devices like the TPS7H1101A-SP, which is on the KU060 development board.

- Size. Other than having a small, easy-to-layout package, other ways to reduce solution size include limiting the number of external components to the LDO; having more integrated features, better PSRR and noise specifications; and more reliable radiation performance under single-event effects. TI’s TPS7A4501-SP is one of the industry’s smallest radiation-hardened LDOs, both in package size, layout and solution size.

Conclusion

With so many options available, it can be difficult to pick the right LDO. Consider which capabilities and features are the most important. For example, if your application is powering a high-end FPGA or high-speed data converter, features like output-voltage accuracy, reference accuracy, PSRR and noise might be the priorities. If, however, you are designing a low-performance analog circuit or working with an older FPGA where tolerance requirements are not so stringent, having the smallest-sized, lowest-cost solution while retaining good-enough capability might be the better option.

Additional Resources

- Read the white paper, “Powering a New Era of High-Performance Space-Grade Xilinx FPGAs.”

- Download the TI Space Products Guide.

- Download the Radiation Handbook for Electronics.