SSZTAH7 january 2017 MSP430F5529 , TPS3110 , TPS3851

Much like a small, yappy dog that lives in a celebrity’s purse, watchdog timers are often considered unnecessary or excessive. To equate the two, how ever, would do a great disservice to the watchdog. Unlike “purse dogs,” watchdogs add critical monitoring features that allow you to internally and externally monitor your system for failure and take action should that happen.

Just What Is a Watchdog Timer?

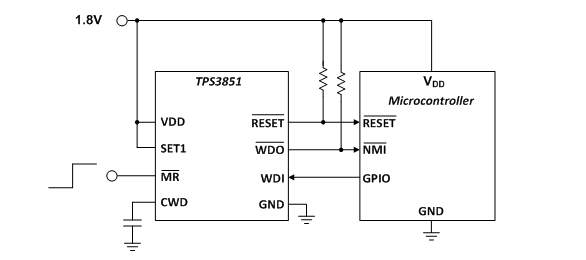

Figure 1 Watchdog Monitoring Provided by the TPS3851

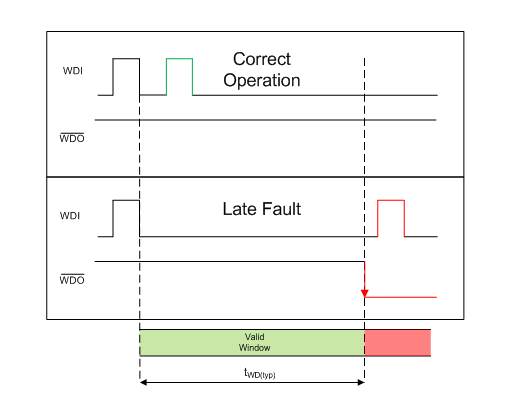

Figure 1 Watchdog Monitoring Provided by the TPS3851The processor periodically sends a pulse to the watchdog timer to indicate that the system software is operating properly. If the watchdog timer does not receive this pulse within an allotted time frame (known as the watchdog timeout), the watchdog timer asserts a reset output. This reset output can be used to notify the system that the processor has experienced a hang or a freeze, or to reset the processor itself. Figure 2 illustrates a pulse received within the watchdog timeout and a pulse received after the watchdog timeout has expired.

Figure 2 Operation of a Standard Watchdog Timer

Figure 2 Operation of a Standard Watchdog TimerWhy Are Watchdog Timers So Important?

How Can I Implement a Watchdog Timer in My Embedded System?

- Using a processor with integrated watchdog functionality. Many microcontrollers such as the MSP430F5529 series have integrated watchdog functionality. This is valuable because it is very easy to implement and no other ICs are required. However, it comes with one major caveat: integrated watchdogs may not always work as desired because the code issues that cause the MCU to malfunction could also inadvertently disable the watchdog timer. Again, software is written in such a way that an internal watchdog should be able to detect any freezes or hangs. However, taking the extra steps to monitor the watchdog input in a redundant manner can help account for unforeseen errors in code.

- Using a voltage supervisor with a watchdog timer. A supervisor with watchdog-timer functionality such as the TPS3851 or the TPS3110 allows you monitor both the supply voltage and watchdog signal in an external, redundant fashion. Should the internal watchdog of the processor fail to detect an errant or missing pulse, the external watchdog timer will add a level of detection not achievable otherwise.

In principle, the functionality of a watchdog timer is not overly complicated. However, its importance in maintaining the reliability of systems cannot be overstated. This is especially true if a human-initiated system reset in case of failure is not possible or very difficult.

Additional Resources

- See more of TI’s supervisors with watchdog timers.

- For more information on voltage supervisors, read the blog post, “Why monitoring voltages matters.”

- Learn more about TI’s microcontrollers.