SWRA574B October 2017 – February 2020 AWR1243 , AWR2243

2.2.1 Frame (Burst) and Chirp Timing in AWR2243

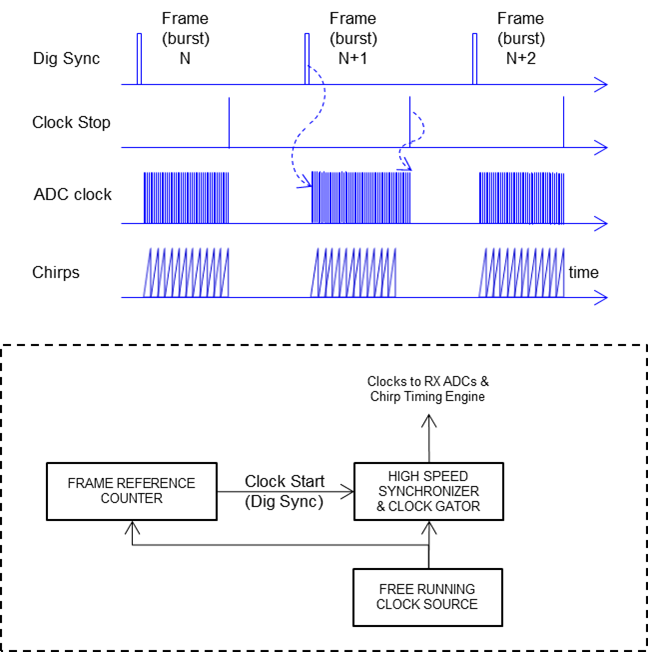

The AWR2243 device includes a frame reference counter (FRC) which maintains timing across frames (bursts). It generates a digital synchronization (labeled "Dig Sync" in Figure 5) signal, also referred to as frame (burst) start signal based on the frame (burst) timing parameters given by the API messages described in the Software Messaging section. The processor firmware also relies on the FRC to schedule calibrations, monitoring and setting up of functional bursts.

The AWR2243 device also includes a high speed synchronizer and clock gator, which starts off the high speed clocks to the RX ADCs and chirp timing engine in synchronism with Dig Sync. The chirp timing engine maintains the timing during and across multiple chirps within each frame (burst) and accounts for the generation of synthesizer ramp and RX ADC valid data picking, and so forth. At the end of each frame (burst), the clocks are stopped by the processor. This is illustrated in the timing and block diagrams below in single chip usage example.

Figure 5. Frame (Burst) Timing and Clock Generation in AWR2243

Figure 5. Frame (Burst) Timing and Clock Generation in AWR2243