SWRZ101B December 2021 – December 2023 AM2732 , AM2732-Q1

i2387

PLL: GCM circuit glitch during clock source switch

Details:

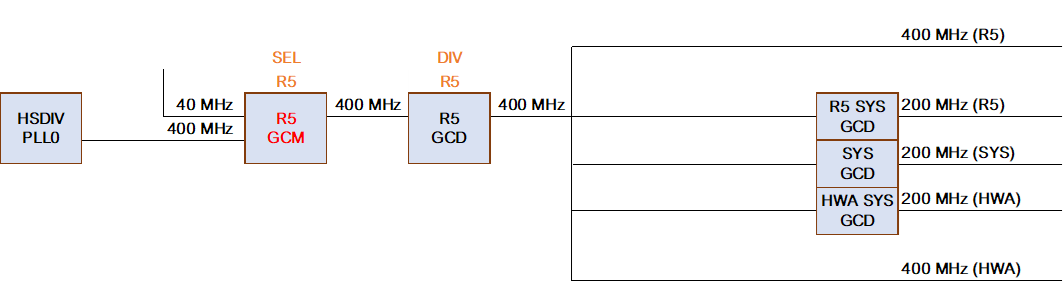

GCM circuit [highlighted] is susceptible to glitch when switching the clock source from Crystal to the PLL Clock, causing the phase misalignment between SYS clocks resulting in random behaviors like aborts or hangs or access failures. Reference below for HSDIV0 feeding clock to R5F and SYS Clocks.

Figure 2-2 PLL

Figure 2-2 PLLWorkaround(s):

1: Use external WDT to reset in case of hang scenarios.

2: Use staggered PLL programming sequence [Step 1 to Step 5] to switch from 40MHz- 200MHz – 400MHz in SBL. Application where R5F Running at 400MHz (Core PLL HSDIV0CLKOUT0 output is 400MHz)

Step 1: Program MSS_CR5_CLK_SRC_SEL, MSS_CR5_DIV_VAL and SYS_CLK_DIV_VAL ‘000 ; // Switch back to XTAL

Step 2: Program MSS_CR5_DIV_VAL ‘111; // Suppress the glitch

Step 3: Program SYS_CLK_DIV_VAL ‘111 ; // R5F and SYS clocks are in 1:2 ratio

Step 4: Program MSS_CR5_CLK_SRC_SEL ‘222; // Switch to PLL clock , switch to 200MHz

Step 5: Program MSS_CR5_DIV_VAL ‘000 ; // Switch back to 400MHz

Application where R5F Running at 200MHz (Core PLL HSDIV0CLKOUT0 output is 200MHz)

Step 1: Program MSS_CR5_CLK_SRC_SEL, MSS_CR5_DIV_VAL and SYS_CLK_DIV_VAL ‘000 ; // Switch back to XTAL

Step 2: Program MSS_CR5_DIV_VAL ‘111; // Suppress the glitch

Step 3: Program SYS_CLK_DIV_VAL ‘000 ; // R5F and SYS clocks are in 1:1 ratio

Step 4: Program MSS_CR5_CLK_SRC_SEL ‘222; //Switch to PLL clock , switch to 100MHz

Step 5: Program MSS_CR5_DIV_VAL ‘000 ; //Switch back to 200MHz