TIDT244 July 2021

3.4 Current Regulation

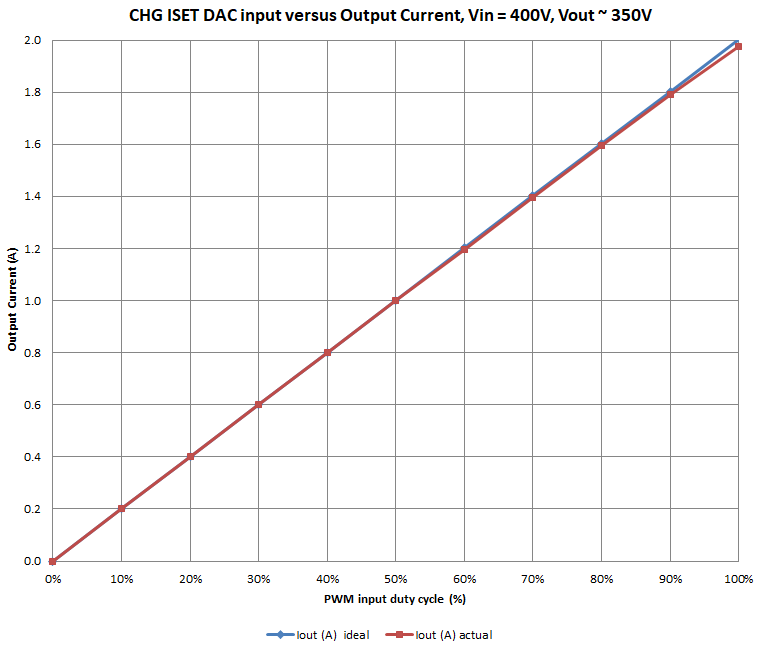

This graph displays the measured output current versus CHG ISET DAC at an input voltage of 400 Vdc. A PWM signal is provided at J8 with a frequency of 100 kHz, an amplitude of 2.5 V, and a duty cycle varying between 0% and 100%. A constant resistance mode load of 200 Ω is used and VOUT is allowed to vary with the current control.

Figure 3-7 CHG

ISET DAC Accuracy Curve

Figure 3-7 CHG

ISET DAC Accuracy Curve Figure 3-8 CHG

ISET DAC Accuracy Table

Figure 3-8 CHG

ISET DAC Accuracy Table