TIDT280 May 2022

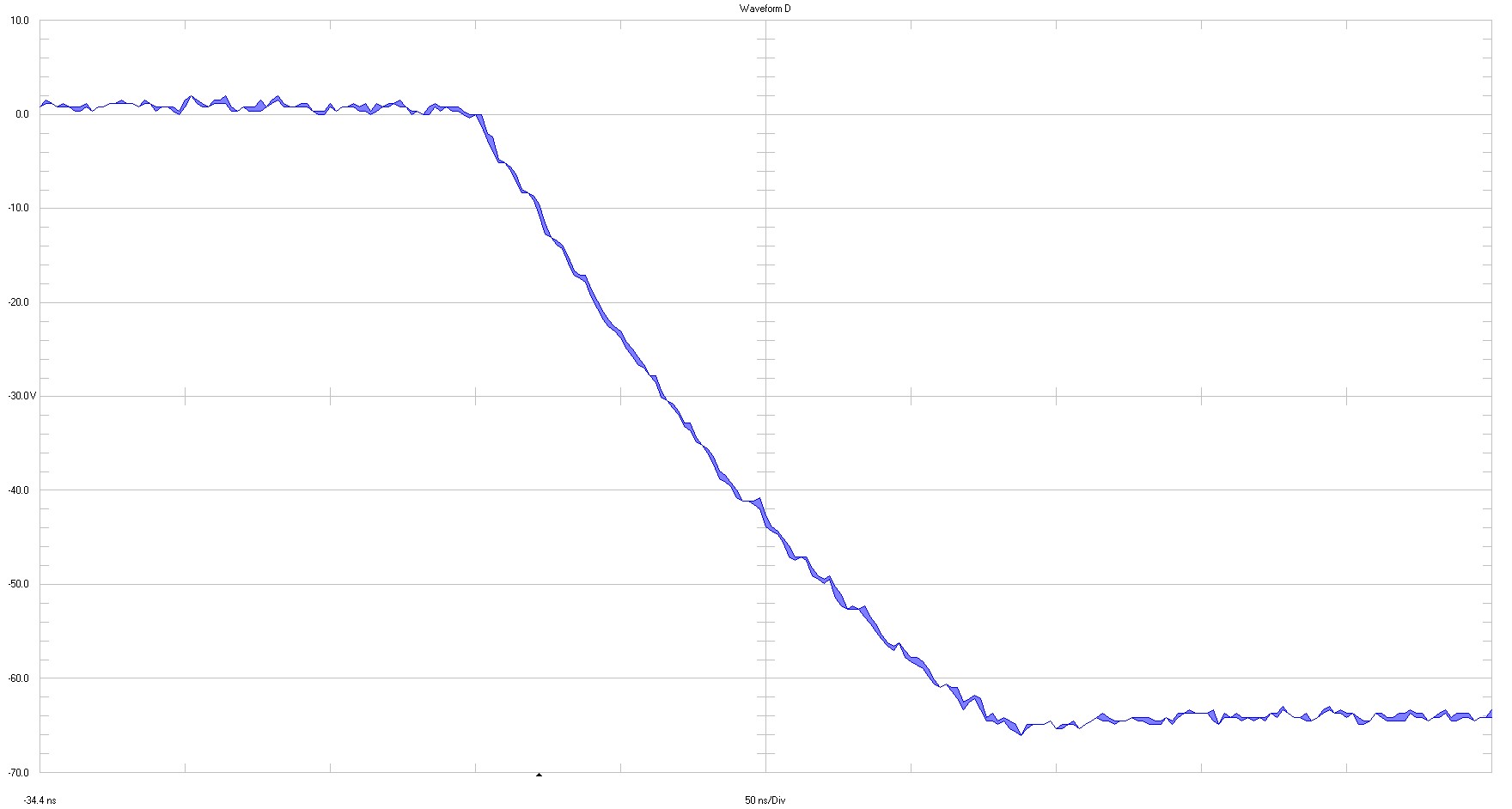

3.1.2.1.2 56-V Input Voltage

|

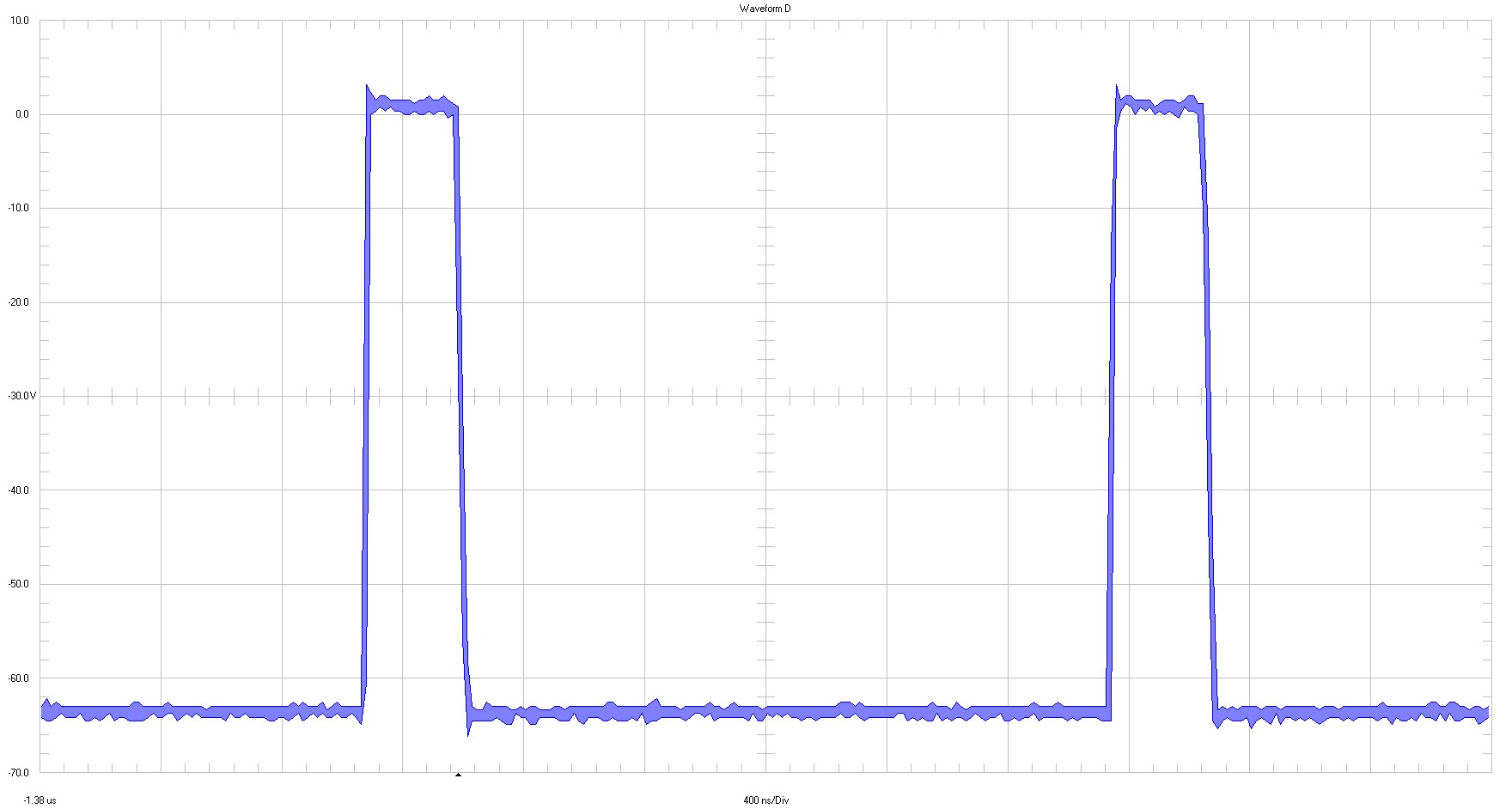

10 V / div full bandwidth 400 ns / div |

|

|

|

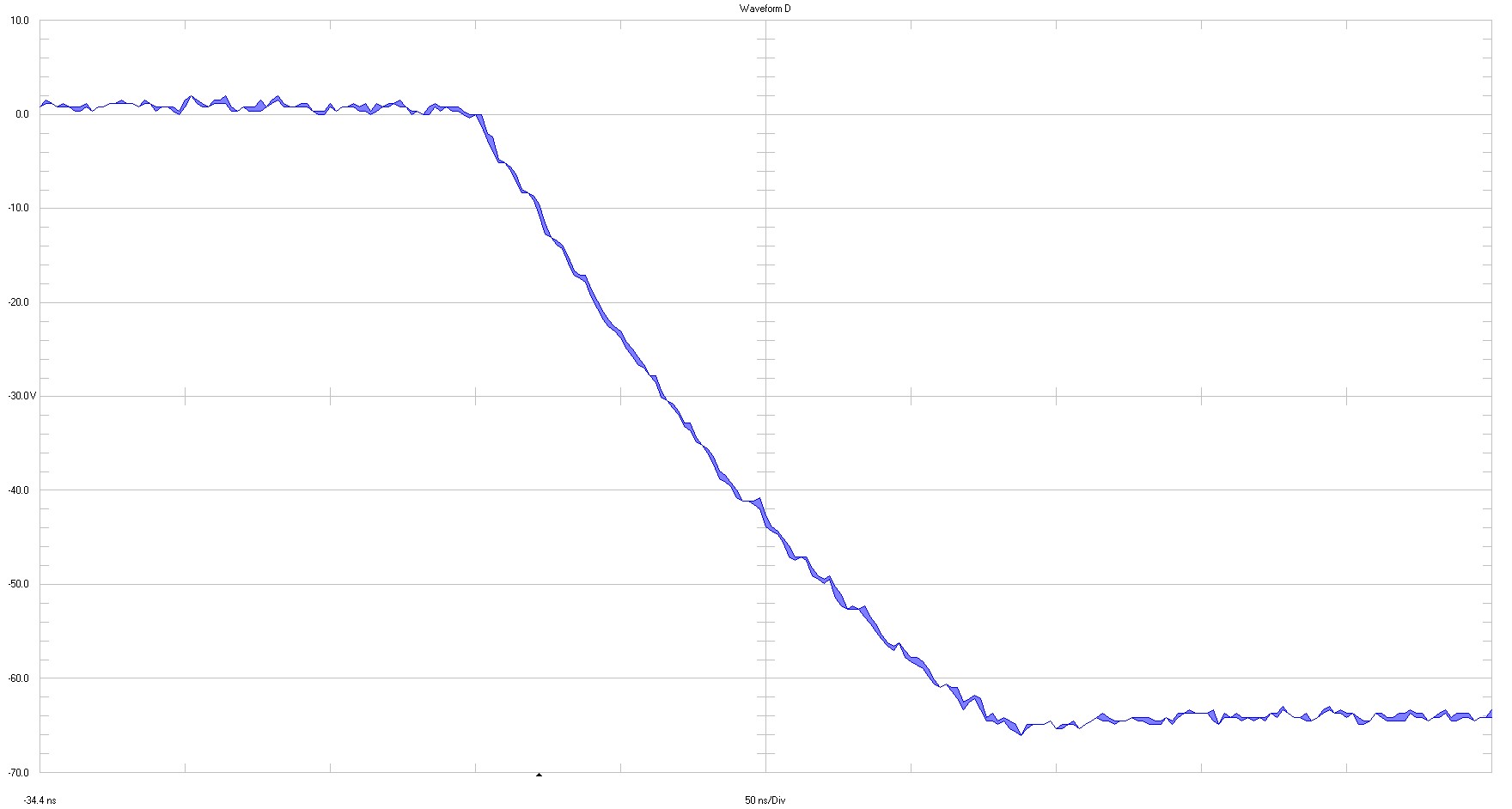

10 V / div full bandwidth 50 ns / major div |

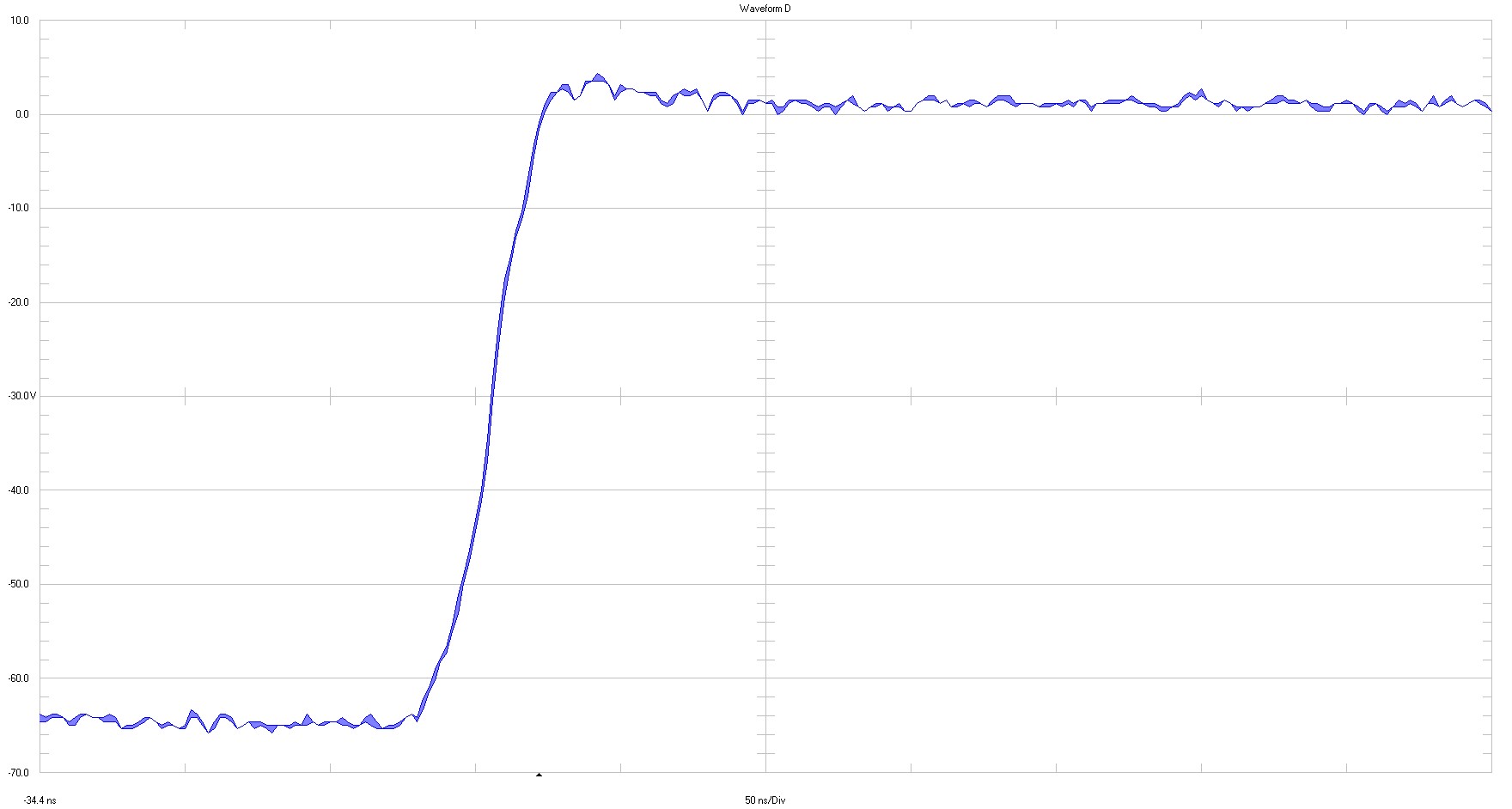

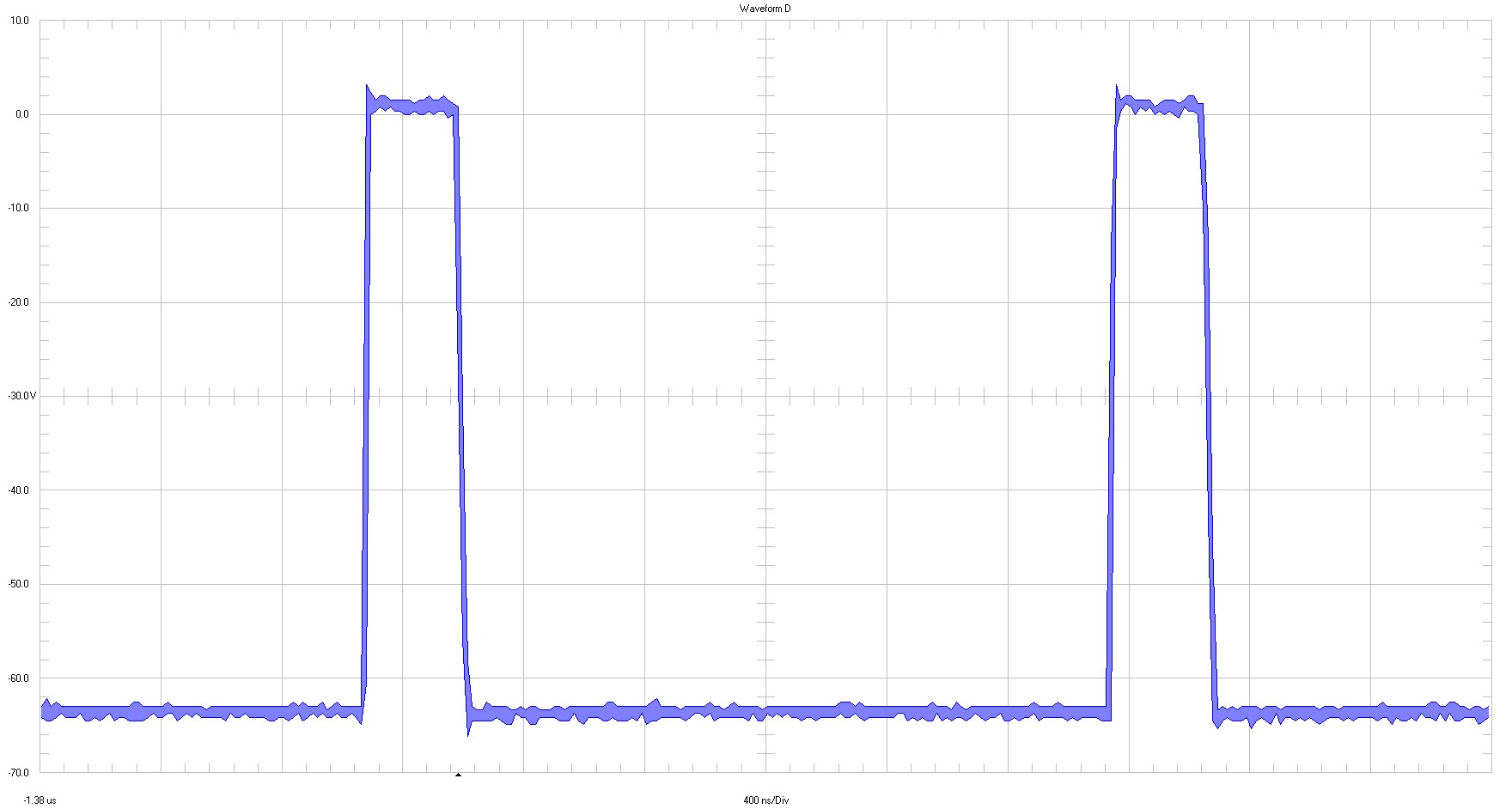

Figure 3-6 Q1 Source-Drain at 56

VIN

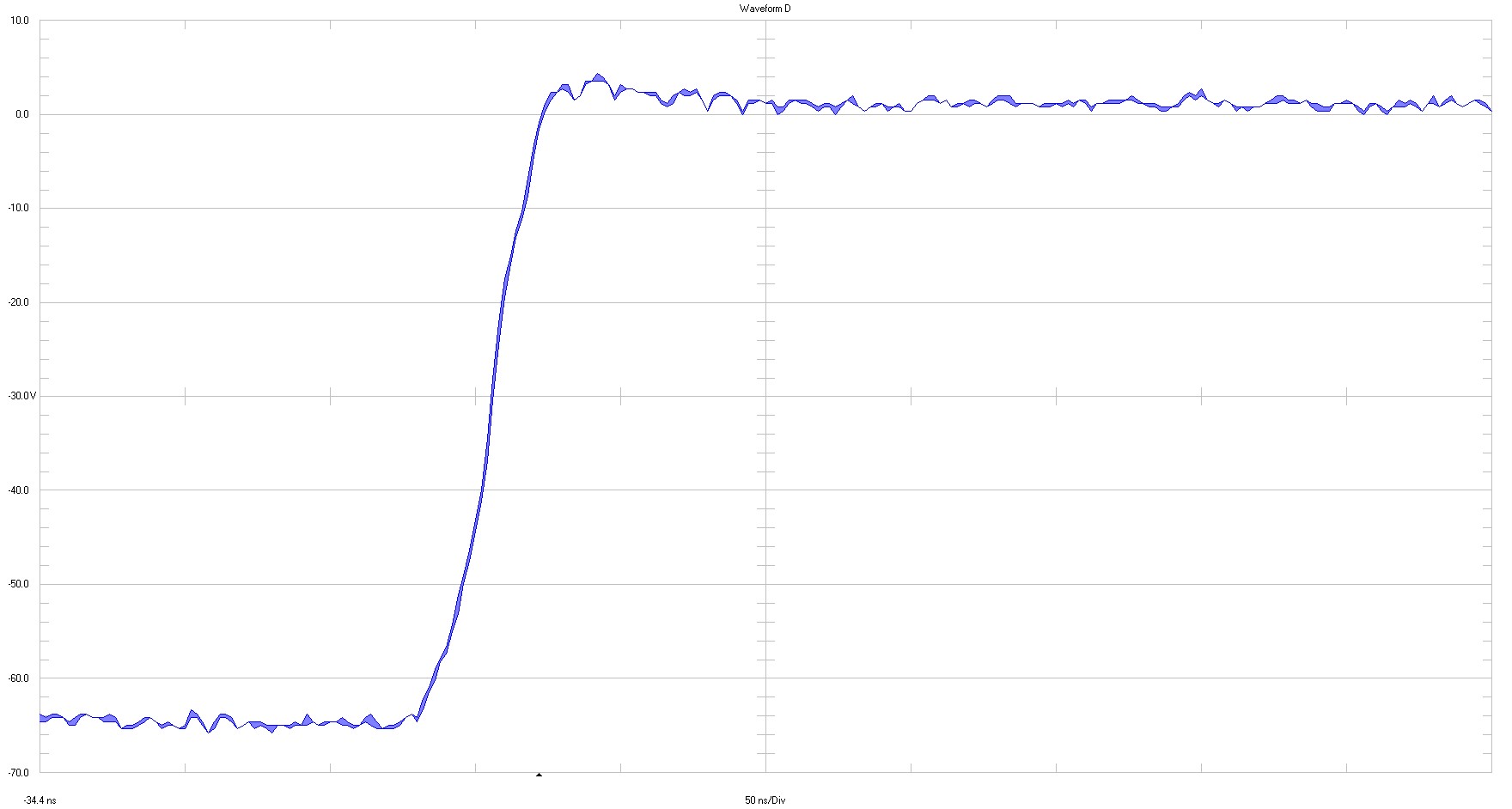

TIDT280 May 2022

|

10 V / div full bandwidth 400 ns / div |

|

|

|

10 V / div full bandwidth 50 ns / major div |