TIDT328 april 2023

A.2.2.1 Sinus 120 Hz

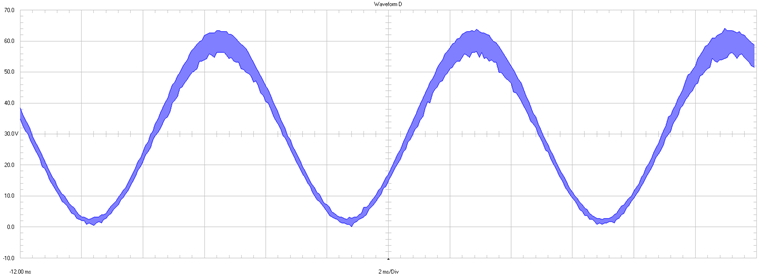

|

10 V / div 2 ms / div full bandwidth |

Figure 4-9 Modulation Sinusoidal (5

VPP + 2.5 V) 120 Hz, 12 VIN, 200-Ω

Load

Modulation set to 120 Hz, sinusoidal output voltage looks promising, but the output ripple voltage is increased by lowering output impedance.

Ripple reduction – instead of using a single output capacitor 2.2 µF,100 V, X7R, 1210, a small improvement can be achieved by using several smaller capacitors in parallel ⇒ 3 × 1 µF, 100 V, X7R, 1206, that is, Murata GCJ31CR72A105KA01.