ZHCA883A January 2019 – September 2024 CSD13380F3 , PCM5102A , TPS3890 , TPS7A8300

设计说明

电源调节是音频应用中的一个关键方面。汽车音响主机和高端售后市场汽车音频系统中常见的电路将实现硬件级静音,以确保音频数模转换器 (DAC) 和放大器在建立电源时能够保持静音。这些电源还需要一些调节,以降低耦合到音频 DAC 中的噪声。该电路显示了一个用于为音频 DAC 生成 +3.3V 电源的低噪声、低压降 (LDO) 稳压器。LDO 的另一个好处是 LDO 可以在更宽的输入电压范围内维持电源电压。电压监控器用于在 LDO 的源开始崩溃时通知 DAC,因此音频 DAC 可以在其电源被移除之前对输出进行软静音。这将减少关闭和启动期间不必要的咔嗒声或砰砰声。

设计说明

- 在该电路中,当软静音引脚 (XSMT) 保持低电平时,DAC 会将输出静音,但并非所有 DAC 都采用低电平有效静音输入。某些器件为其他器件(如静音开关和放大器)提供使能信号,这些器件要求 MUTE 为高电平有效。在这些情况下,可以在输出端添加一个简单的 N 沟道 MOSFET,从而使信号反相。

- 在加电事件期间,监控器 CT 引脚 (CCT) 上的电容器允许 SNS 引脚值上升到阈值电压以上以及 SNS_OUT 变为高电平后具有额外的延迟。这可用于延迟 LDO 的 MUTE 输出停用,以建立其电压(因为它必须对输出电容器进行充电)。此外,如果在 DAC 退出静音之前有其他器件需要时间进行初始化,这将非常有用。可以使用以下公式计算额外的传播延迟。

- 当器件的电源部分减小但不足以在器件内发出完全上电复位 (POR) 时,会发生欠压事件。因此,建议在这些事件期间确认完全复位。监控电路可以实现这一点,因为 XSMT 引脚充当音频 DAC 的复位电路。

- 大多数音频 DAC 采用 VCOM 或 VREF 架构。VCOM 架构使用电源中的简单分压器来创建输出振幅基准。这是很优越的架构,因为它可以确保当电源不是标称值时不会有来自 DAC 的输出削波,因为输出会随输入电压的变化而相应地变化。该架构的缺点是电源噪声的电源抑制比 (PSRR) 有限。虽然音频 DAC 的 VCOM 引脚上的电容器将提供一些滤波功能,但它仍可能影响输出。

在 VREF 配置的架构中,音频 DAC 生成内部基准。这将为系统带来更好的 PSRR 性能。该设计的缺点是如果电源电压下降,输出可能会削减。

设计步骤

- 选择根据电流输出能力、电压输入范围和输出噪声来选择 LDO 稳压器。为音频 DAC 供电的 LDO 必须至少能够提供所需的 DAC 电流。此外,如果同一总线上有其他器件(如放大器),则必须考虑这些器件的静态电流。LDO 输入电压范围必须适应主电源,假设该电路中的主电源是一节 12V 的电池。

- 必须计算反馈 (FB) 电压以提供正确的输出电压。在该电路中,可以通过以下所示的公式计算电阻器 R1 和 R2。

鉴于 VDD 的设计目标为 +3.3V,并且该 LDO 的 VREF 约为 0.8V,请使用 35.7kΩ 的 R1 和 11.5kΩ 的 R2。此外,请注意 FB 节点具有电流要求,建议在选择 R2 时使用以下公式作为指导。

- 选择电压监控器以实现系统所需的功能。在该电路中,所选的监控器具有使能输入引脚。利用该功能,用户(或微控制器)可以使用于覆盖监控器输出的信号静音。此外,一些监控器允许监控多个电源轨,这对输出放大器很有用。

- 可以使用以下公式计算检测电压。

当 SNS 电压低于基准电压(约 1.15V)时,SNS-OUT 引脚被拉低。对 R3 使用 10kΩ 并对 R4 使用 2kΩ,如果 VBATTERY 电源降至低于约 6.9V,则器件会静音。

LDO 使用电容器 CNR/SS 来降低噪声并启用 LDO 软启动功能。

- 根据应用需求来选择 DAC。考虑所需的 SNR、THD+N 和支持的 I2S 接口采样率。虽然大多数音频 DAC 支持 16kHz 至 192kHz 的采样率,但并非所有音频 DAC 都支持 384kHz 或 768kHz 等采样率。较高的采样率会导致噪声整形,从而使带外噪声进一步远离可闻范围,但并非所有音频源都能提供这些采样率。

- 用于音频滤波器的电容器应为 COG、NP0 型陶瓷电容器。COG、NP0 型电容器具有较低的电容电压系数,这意味着组件的电容值受器件两端电压偏置的影响较小。由于电容器是滤波器性能的关键,因此应避免在信号路径中使用其他类型的陶瓷电容器。

- 用于 LDO 输入和输出的电容器应具有低等效串联电阻 (ESR),例如 X7R-、X5R- 和 COG- 型电容器。

- 用于 LDO 和电压监控器的电阻器可以是厚膜,但电阻分压器的精度会影响 LDO 输出电压和监控器阈值。因此,建议 R1、R2、R3 和 R4 的最大容差为 1%。

- 建议针对 DAC 输出滤波器中的电阻元件使用薄膜电阻器。

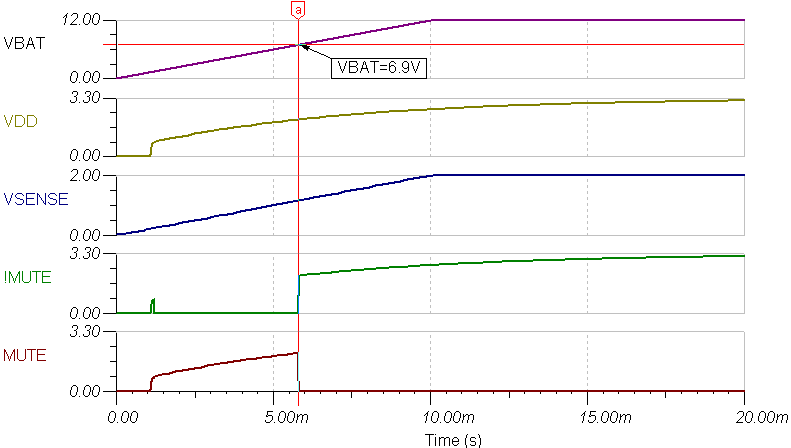

加电静音瞬态

以下仿真显示了电路的加电瞬态。可以看到,直到 VBAT 输入达到大约 6.9V 时才释放 MUTE 输出。

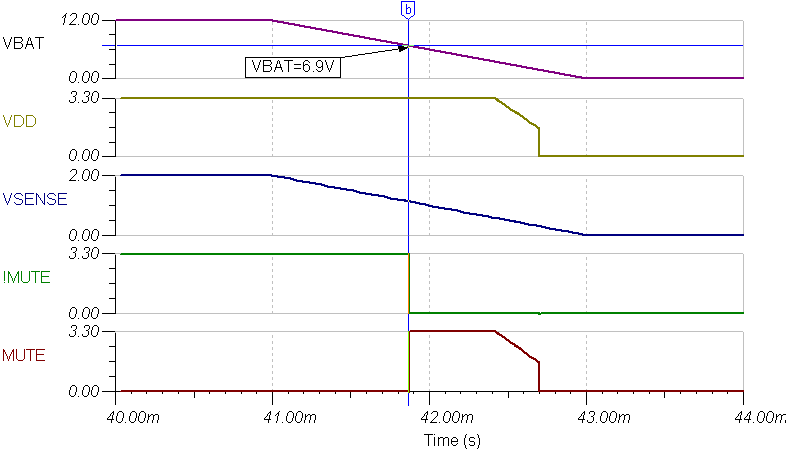

断电静音瞬态

以下仿真显示,当 VBAT 输入降至 6.9V 以下时,MUTE 输出置为低电平。

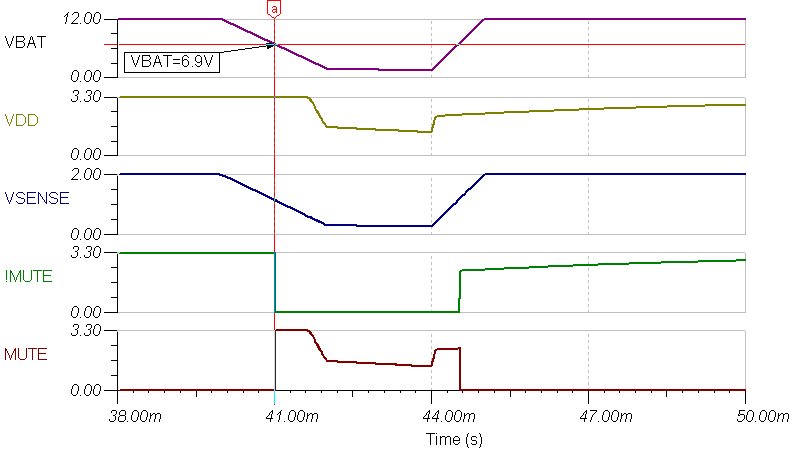

欠压静音瞬态

以下仿真展示,DAC 在 VDD 电源受到欠压事件影响之前将处于静音状态。当 VBAT 电压降至约 6.9V 以下时,MUTE 信号会置于低电平。VBAT 恢复后,MUTE 信号会取消置位。

设计中采用的器件

| 器件 | 主要特性 | 链路 | 其他可能的器件 |

|---|---|---|---|

| PCM5102A | 具有 32 位 384kHz PCM 接口的 2VRMS DirectPath™、112dB 音频立体声 DAC | 具有 32 位 384kHz PCM 接口的 2VRMS DirectPath™、112dB 音频立体声 DAC | 音频 DAC |

| TPS7A8300 | 2A、6µVRMS、低噪声 LDO 稳压器 | 具有电源正常指示功能的 2A、低输入电压、低噪声、超低压降稳压器 | 线性和低压降 (LDO) 稳压器 |

| TPS389001 | 具有可编程延迟的低静态电流、1% 精度电压监控器 | 具有可编程延迟的低静态电流、1% 精度监控器 | 监控器和复位 IC |

| CSD13380F3 | 12V N 沟道 FemtoFET™ MOSFET | 采用 0.6mm x 0.7mm LGA 封装、具有栅极 ESD 保护的单路、76mΩ、12V、N 沟道 NexFET™ 功率 MOSFET | MOSFET |

设计参考资料

米6体育平台手机版_好二三四 (TI),SBAM414 电路配套仿真文件,软件

其他链接:

米6体育平台手机版_好二三四 (TI),精密 DAC 学习中心,米6体育平台手机版_好二三四系列概述

米6体育平台手机版_好二三四 (TI),音频 DAC,米6体育平台手机版_好二三四系列概述