ZHCA886A January 2019 – September 2024 DAC8871 , OPA211 , OPA828 , REF6050

设计目标

| DAC 输出范围 | DAC VREFH 输入电压 | DAC VREFL 输入电压 |

|---|---|---|

| -5V 至 5V | 5V | -5V |

设计说明

磁共振成像 (MRI) 机 和任意波形发生器 (AWG) 等应用中使用的高精度数模转换器 (DAC) 通常需要高精度电压基准。这些系统常见问题的原因是 DAC 的基准输入端存在不需要的串联电阻。当 R-2R 电阻梯的输入电流根据 DAC 输入代码变化时,该电阻将在它们两端产生取决于该代码的电压。最终结果是基准电压似乎会根据 DAC 代码而变化,这将导致弓形积分非线性误差曲线。

为了解决该问题,高精度 DAC 通常为每个基准输入(VREFH 和 VREFL)提供基准强制和检测引脚。虽然这些引脚本质上只是与 R-2R 电阻梯基准输入节点的两个并联连接(每个连接都有各自的串联电阻),但添加外部单位增益基准缓冲器可以使放大器对节点上的电压进行补偿。流入运算放大器反相输入的小偏置电流将在检测输入的串联电阻上产生最小电压,而运算放大器的输出可以提供 R-2R 电阻梯所需的电流。

设计说明

- 所选的基准仅具有正 5V 输出,因此需要使用反相放大器来生成 VREF- 值。电阻器 R1 和 R2 也会生成从基准输出到 –5V 电位的电流路径。该电流由电压基准提供。可以通过增大 R1 和 R2 的值来限制该电流,但代价是电路会产生额外的噪声。放大器的电流噪声和电阻器的热噪声是导致电路总噪声的其中两个因素。

- 可以通过添加 CFILT 来降低基准的噪声,该电容器会过滤内部基准的带隙产生的噪声。基准的输出还需要一个具有最小等效串联电阻 (ESR) 的电容器 (CL)。可以通过延长的迹线在 PCB 上生成此电阻(显示为 RESR)。

- DAC 的噪声主要由电阻梯的热噪声产生。可以使用以下公式来计算热噪声,其中 Kb 是玻尔兹曼常数,T 是以开尔文为单位的温度,R 是电阻梯的电阻,F 是频率范围。

DAC8871 的典型输出阻抗约为 6.25kΩ,假设在室温下运行,其热噪声可通过以下公式进行计算:

设计步骤

- 根据分辨率、精度和噪声性能来选择 DAC。分辨率可能取决于应用,但在该电路中通常会看到 16 位或更高的分辨率。DAC 输出中的误差被视为非线性误差。非线性误差表示为积分非线性误差 (INL) 和微分非线性误差 (DNL)。假设 DAC 的输入端具有理想基准,则 R-2R 电阻梯的电阻不精确性将导致系统的 INL 和 DNL 误差。

- 根据应用的精度、热漂移和噪声要求来选择基准。输出电压精度通常以百分比表示。热漂移以 ppm/°C(百万分率)为单位。电路的噪声有两项规格:低频噪声(通常在有限频域(0.1Hz 到 10Hz)内以 VPEAK-PEAK 指定)和总积分噪声(以 VRMS 指定)。

- 应根据噪声性能来选择用于反转基准电压的运算放大器。放大器会通过两种方式来导致系统噪声,即电压噪声和电流噪声。通过选择通常具有低电压噪声的双极输入放大器,可以更大程度地减小电压噪声的作用。双极输入放大器还具有比 CMOS 输入放大器更高的电流噪声,但电流噪声可以通过电路的电阻器 R1 和 R2 转换为电压噪声。通过更大程度地减小这些组件的电阻,可以更大程度地减小放大器电流噪声的作用。

- 应根据快速稳定能力和带宽来选择用于驱动 DAC 的强制和检测输入的放大器。当使用新的输入代码更新 DAC 时,R-2R 电阻梯中的开关将导致需要基准输入提供的电流突然变化。这会导致基准输入上产生瞬态,该瞬态也会在 DAC 输出上传送。如果基准缓冲放大器能够快速稳定,则会更大程度地减小输出误差。此外,这些放大器的电压噪声是导致系统总噪声的因素之一。因此,应选择双极或 JFET 输入放大器。

- 如果需要电路驱动负载,请选择输出缓冲器。DAC8871 是一款无缓冲器件,这意味着 DAC 的输出是电阻梯上的一个节点。该放大器是根据负载要求进行选择的,这些要求包括电流输出能力、容性负载稳定性、压摆率和电压范围等。

- 电容器 CFILT 和 CL 是低 ESR 陶瓷型电容器。这些电容器的额定电压需要与 5V 基准输出相一致。

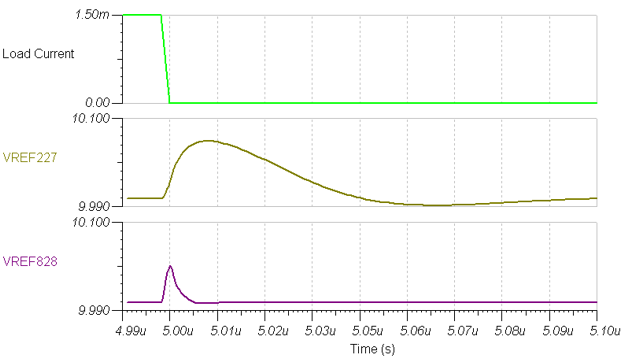

基准缓冲器负载瞬态

当 DAC 更改代码时,基准缓冲器必须能够快速提供 R-2R 电阻梯所需的瞬态电流。鉴于 DAC8871 的架构,当 DAC 从零或满标度代码转换为中标度时,会出现最大瞬态电流。可以使用 VREFH 和 VREFL 输入之间的电流源来对该瞬变进行仿真。以下仿真显示了使用 OPA828 和 OPA227 仿真的电流瞬态期间的差分基准电压。这表明 OPA828 降低了基准误差幅度和持续时间。

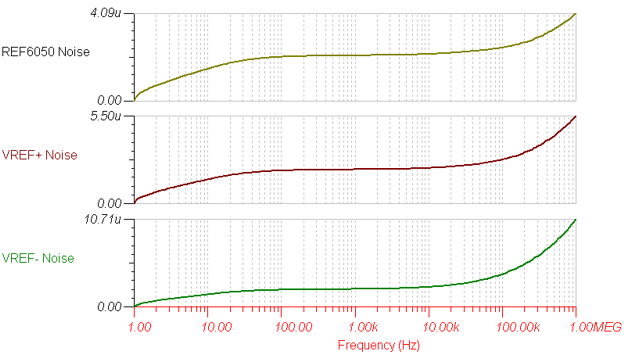

基准缓冲器总噪声

电路产生的总噪声如以下仿真所示。基准、反相放大器和基准缓冲器均会导致噪声。请注意,由于反相放大器及其反馈网络中分立式电阻器的作用,VREF- 输入具有更大的噪声。

设计中采用的器件

| 器件 | 主要特性 | 链路 | 其他可能的器件 |

|---|---|---|---|

| DAC8871 | 16 位、单通道、串行接口、高电压、双极输出 DAC | 16 位、单通道、串行接口、±18V(高电压双极性)输出 DAC | 精密 DAC (≤10MSPS) |

| OPA828 | 低偏移、低漂移、低噪声、45MHz 带宽、JFET 输入运算放大器 | 高速(45MHz 和 150V/μs)、36V、低噪声 (4nV/√Hz) RRO JFET 运算放大器 | 精密运算放大器 (Vos < 1mV) |

| OPA221 | 低功耗、1.1nV/√Hz 噪声、高性能运算放大器 | 1.1nV/rtHz 噪声、低功耗、精密运算放大器 | 精密运算放大器 (Vos < 1mV) |

| REF6050 | 低噪声、高精度、5V 输出电压基准 | 具有集成缓冲器和使能引脚的 5V、5ppm/°C 高精度电压基准 | 串联电压基准 |