ZHCA964A September 2019 – July 2020 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

2.3.3.3 计数器

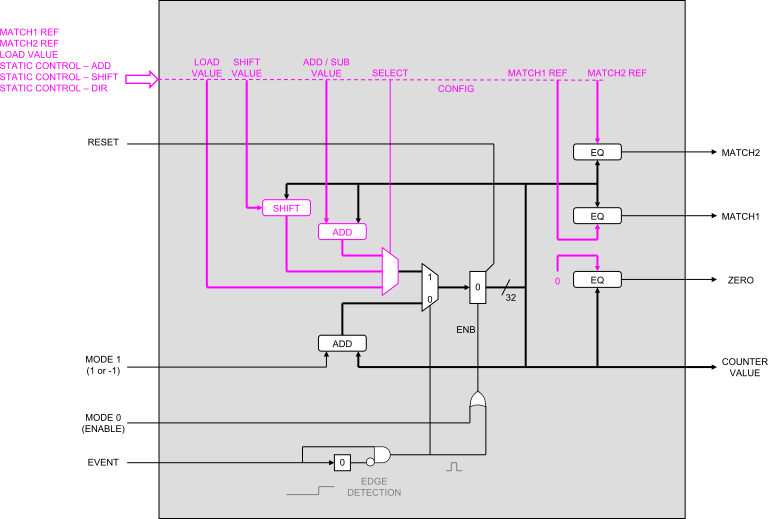

图 2-14 显示了每个 CLB 实例内部可用的三个计数器之一。计数器的核心是具有计数寄存器和加法器的计数循环,该加法器根据 MODE1 输入的状态使计数寄存器递增或递减 1。计数循环还包含一个计数器多路复用器,用于使用先前计数值的递增或递减版本以外的值初始化计数寄存器。例如,可以使用新值、当前计数值的移位版本或当前计数加/减 32 位值寄存器的内容版本来初始化计数寄存器。当MODE0 输入置位,并且ENB 信号置位时,计数寄存器只能在CLB 时钟的上升沿递增或递减。使用上述三个初始值之一加载计数寄存器需要 EVENT 输入从高到低转换。这会产生一个单时钟脉冲,该脉冲会立即将计数器多路复用器从递增/递减模式切换到加载模式,向计数寄存器加载新值。最后,无论其他输入的状态如何,复位输入都会将计数寄存器的内容初始化为零。计数器的全部四个输入都可以根据 SysConfig 工具先前配置的相应控制寄存器从 32 位共享逻辑总线中进行选择。

图 2-14 CLB 计数器块

图 2-14 CLB 计数器块计数器块的输出包括当前计数器值(32 位宽)和来自零比较器、匹配 1 比较器和匹配 2 比较器的三个 1 位状态信号。只要当前计数值与给定比较器关联的比较值相匹配,这些比较器就会发出逻辑 1 脉冲。三个 1 位计数器输出映射到 32 位共享逻辑总线的三个预定义位,以后可以用作其他计数器、LUT、FSM 和 HLC 的输入。

HLC 可以直接访问 32 位计数器值,两个匹配寄存器也是如此。C2000 CPU/CLA 也可以通过数据共享寄存器间接加载相同的寄存器。