ZHCA964A September 2019 – July 2020 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

4.1.2 胶合逻辑的 VHDL 代码

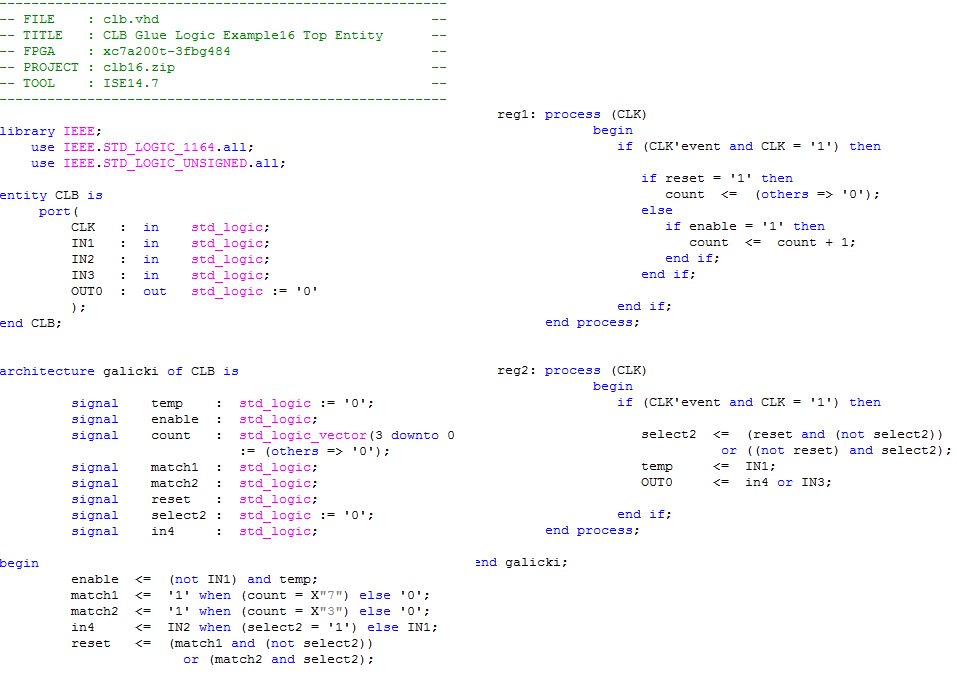

图 4-5 显示了实现图 4-4 的原理图功能的 VHDL 源代码。首先,entity 语句标识三个输入和一个输出以及时钟源(CLB 时钟)。接下来,signal 语句声明内部信号。在信号声明之后,有 5 个信号组合分配语句(瞬时操作,无时钟延迟)。

然后,两个已注册的处理过程用来输出时钟信号。第一个已注册过程 reg1 在 ENABLE 为高电平时在 CLB 时钟的每个上升沿更新 32 位计数器,但每当 RESET 变为高电平时将其循环回至 0。第二个已注册过程 reg2 在 CLB 时钟的每个上升沿更新其余的三个寄存器。这些寄存器包括在下降沿检测电路中使用的 TEMP 寄存器、在简单状态机中使用的 SELECT2 寄存器以及用于锁存输出的 Output 0 寄存器。

图 4-5 CLB 示例 16 – FPGA 胶合逻辑的 VHDL 源代码

图 4-5 CLB 示例 16 – FPGA 胶合逻辑的 VHDL 源代码