ZHCA964A September 2019 – July 2020 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

3.4 CLB 示例 19 – 仅使用外部信号来创建您自己的外设

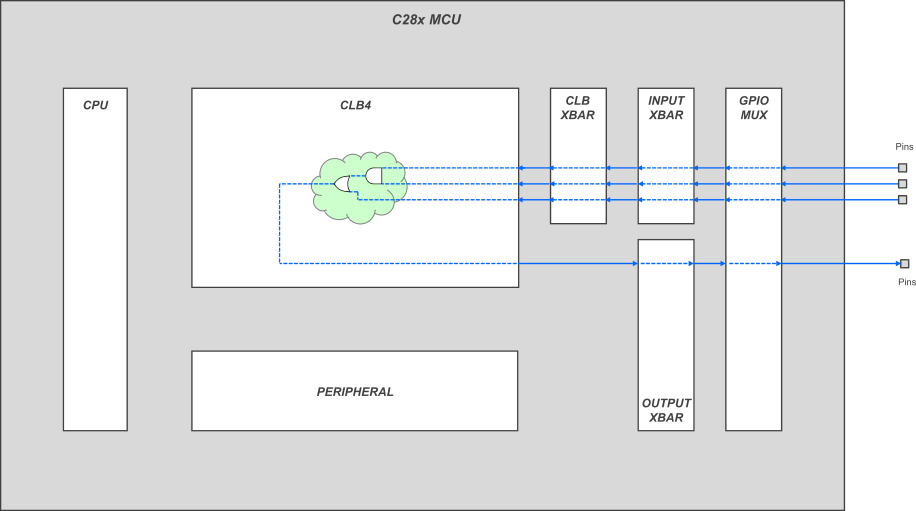

该示例与先前的三个示例的不同之处在于,此处未使用 C2000 外设。相反,CLB4 仅对外部 GPIO 输入进行操作以生成 GPIO 输出。图 3-10 显示有三个外部输入进入 GPIO 多路复用器,并在到达 CLB4 的过程中经过输入 XBar 和 CLB XBar。这三个信号进入 CLB4 之后,会根据 CLB4 配置寄存器进行逻辑组合,然后输出通过输出多路复用器返回到 GPIO 多路复用器,输出在此处放置在分配的输出引脚上。尽管修改内部外设的功能非常强大,但该示例显示,为了使用 CLB,您无需修改或放弃任何外设。可以将自定义逻辑简单地添加到所有其他 C2000 功能之上,以吸收(例如)来自外部器件(如 CPLD 或 FPGA)的胶合逻辑。

图 3-10 CLB 示例 19 – 仅使用外部信号来创建您自己的外设

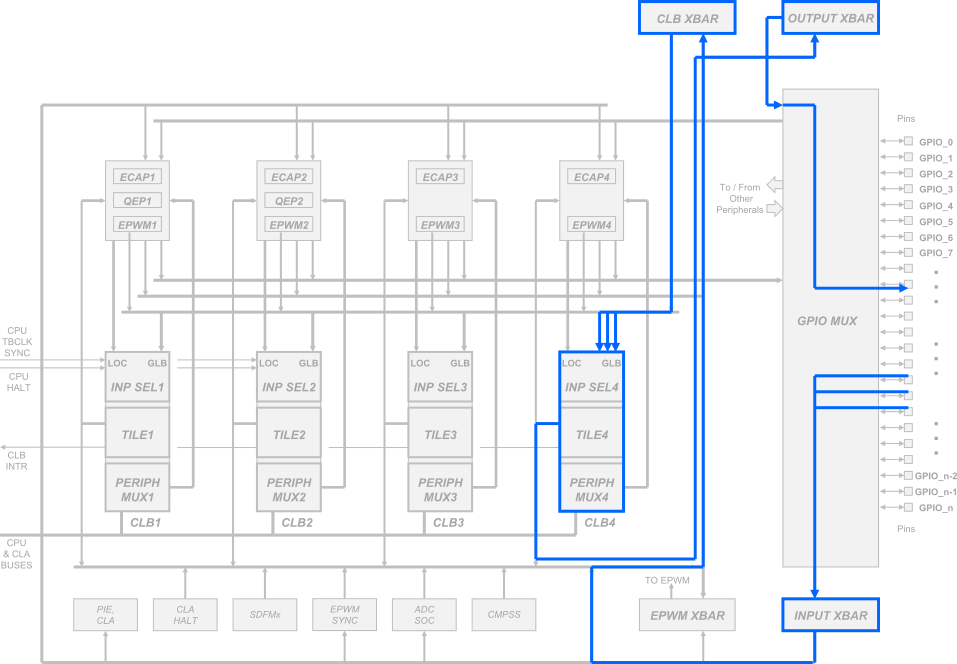

图 3-10 CLB 示例 19 – 仅使用外部信号来创建您自己的外设图 3-11 在器件级视图中显示了相同的示例,以在整个 I/O 部分的暗灰色背景下更好地显示活动块和产生的数据传输。在此处,它显示了三个 GPIO 输入,它们通过 CLB4 的输入选择部分中的输入 XBar 和 CLB XBar 到达全局信号总线,它们在此处转发至逻辑块 4 以应用自定义逻辑。产生的输出通过输出 XBar 路由到 GPIO 多路复用器,以放置在分配的输出引脚上。在这种情况下不使用 CLB4 的外设信号多路复用器块,并可以将其忽略,因为没有要更改的外设(因此没有要替换的外设信号)。

图 3-11 示例 19 中的信号流 – 器件视图

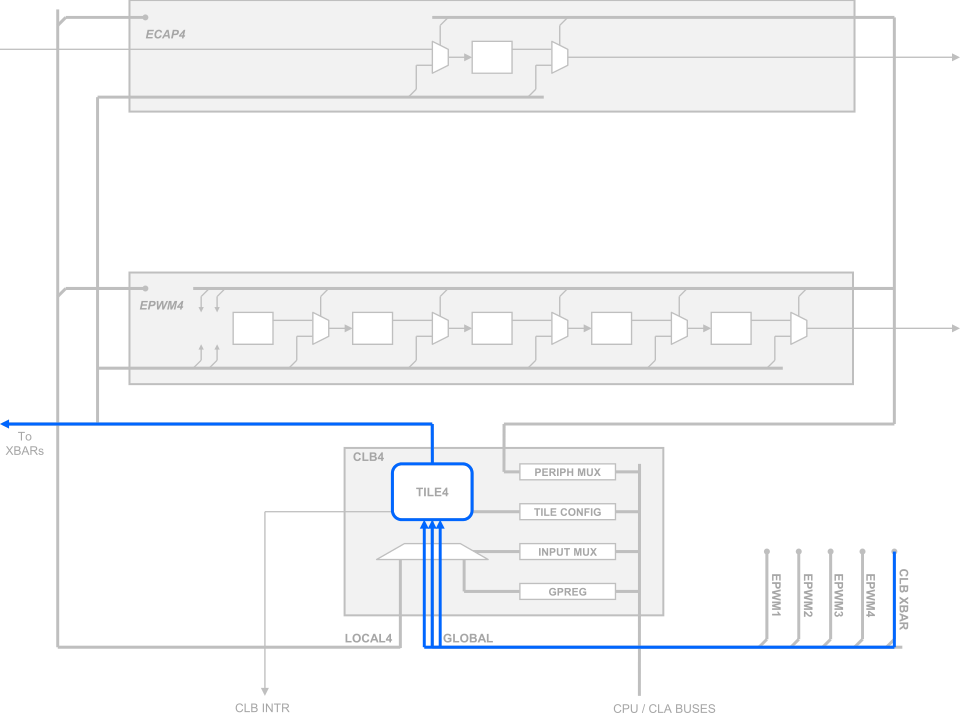

图 3-11 示例 19 中的信号流 – 器件视图图 3-12 提供了 CLB4 内部该示例的信号流详细信息。来自 CLB XBar(以及之前的输入 XBar)的三个输入信号使用全局信号总线到达 CLB4 的输入多路复用器部分。配置寄存器中的内容指示输入多路复用器将三个输入转发到逻辑块 4,在逻辑块 4 中应用自定义逻辑以产生输出信号。该输出通过 CLB4 输出信号总线离开逻辑块 4,向输出 XBar 和 GPIO 多路复用器传输。同样,由于在这种情况下不涉及控制外设,不需要使用外设信号多路复用器来替换任何内部外设信号,因此可以保持不变。外设信号多路复用器的默认状态是保留所有外设信号(不使用 CLB 信号替代任何外设信号)。

图 3-12 示例 19 中的信号流 – CLB4 连接

图 3-12 示例 19 中的信号流 – CLB4 连接