ZHCAA38E August 2021 – January 2023 TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28384D , TMS320F28384S , TMS320F28386D , TMS320F28386S , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

5.1.1 CPU 控制

- 测试条件

器件 1 发送数据 -> 器件 2 接收数据 -> 器件 2 CPU 将 RX 数据移至 TX 缓冲区和寄存器 -> 器件 2 通过将接收到的数据转发回至器件 1 的软件触发 FSI TX -> 器件 1 接收返回的数据,CPU 验证这些数据是否与最初发送的 TX 数据相匹配。

- 测试案例

8 个字的数据长度,2 条数据线,TXCLK = 50MHz,启用设置 ①(表 5-1)。

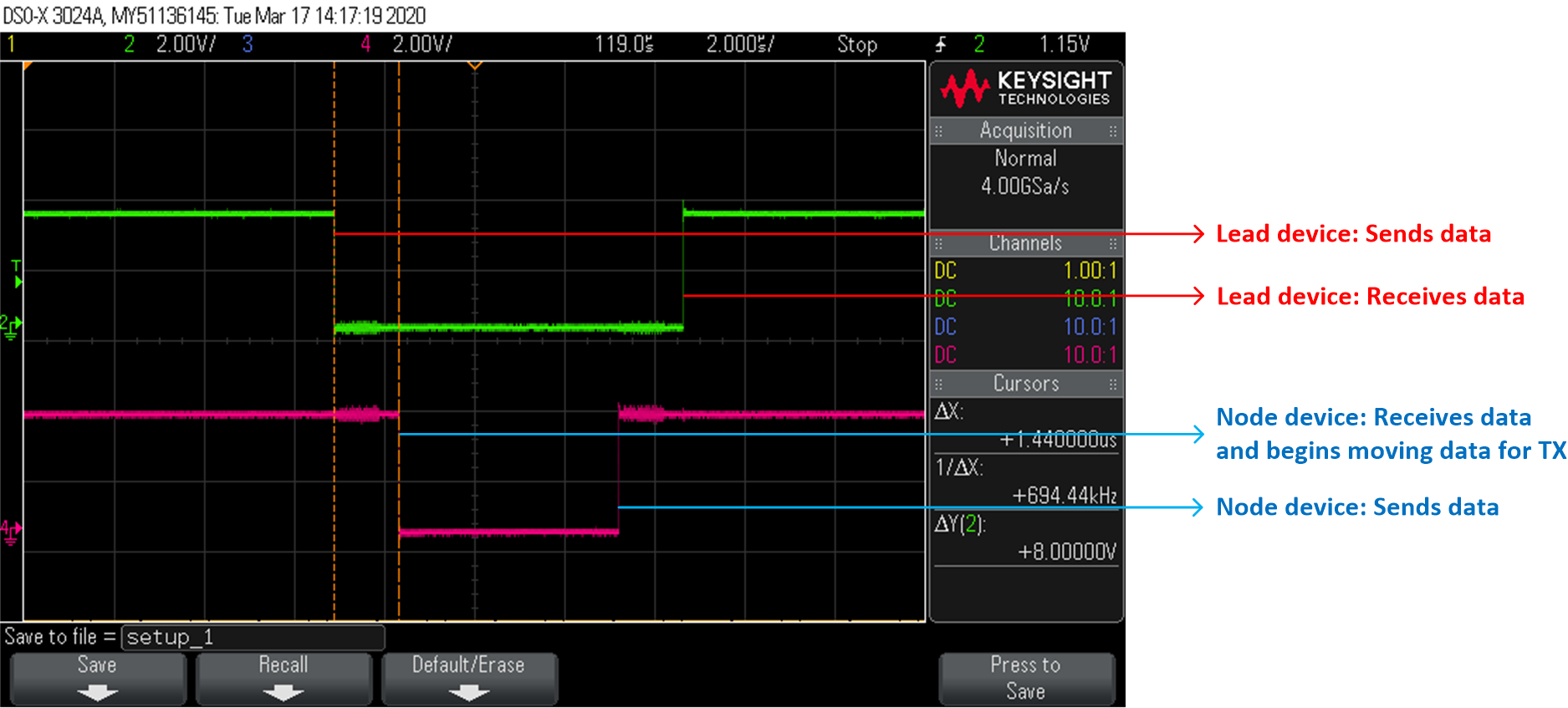

在测试中,当通信期间发生特定事件时,会在软件内翻转通用输入/输出 (GPIO),并使用示波器对其进行测量以获取相应的时序数据。在#ID-7CD0D2B9-E0CF-4048-E67C-7DA3F4712D86中,绿色信号表示器件 1(主控器件)的 GPIO 翻转,品红色信号表示器件 2(节点器件)的 GPIO 翻转。

图 5-3 采用 CPU 控件的数据传输测试

图 5-3 采用 CPU 控件的数据传输测试根据#ID-7CD0D2B9-E0CF-4048-E67C-7DA3F4712D86中所示的结果,获取的数据传输时间大约为 1.4µs。为了计算传输速度,应考虑总数据长度。表 5-2 显示了数据帧的通用结构,该结构可以分为两部分:有效数据位和开销位。

- 有效数据位:包括 8 位用户数据、16 位数据字和 8 位 CRC 字段

- 开销位:包括前同步码、SOF、帧类型、EOF 和后同步码字段

因此,理论上可以得出 8 个字的理想传输时间,如表 5-3中所示。

应该注意的是,两条数据线仅适用于有效数据位,因此一个 FSITXCLK 周期提供 4 个有效数据位,而一个 FSITXCLK 周期仅提供 2 个开销位。因此,8 个数据字需要 48 个 FSITXCLK 周期,从而可以计算出传输时间,如#EQUATION-BLOCK_LRC_5FS_SQB中所示。

因此,理论传输速度为 175Mbps(168/0.96µs),而测试速度为 120Mbps,传输时间为 1.4µs,这是由于测试的传输时间包括进入 ISR(用于翻转 IO 引脚)以及隔离器、收发器、电缆等引入的延迟。如果改为一条数据线,则理论传输速度为 100Mbps,而测试速度为 80Mbps,传输时间为 2.1µs。

#ID-7CD0D2B9-E0CF-4048-E67C-7DA3F4712D86的另一个发现是,使用 FSI driverLib 函数在节点器件中将数据从 FSIRX 缓冲区移至 FSITX 缓冲区需要一些时间,该时间大约为 4.9µs。这将是区分后续部分所示 DMA 控制和硬件控制的关键因素。

| IDLE | 前导码 | SOF | 帧类型 | 用户数据 | 数据字 | CRC | 帧标签 | EOF | 后同步码 | IDLE |

|---|---|---|---|---|---|---|---|---|---|---|

| 1111 | 1001 | 0011 | 8 位 | N 个字 | 8 位 | 4 位 | 0110 | 1111 |

| 有效数据位(位) | 开销位(位) | 总长度(位) | 有效数据位的 FSITXCLK 周期(周期) | 开销位的 FSITXCLK 周期(周期) | 总数据传输时间 (us) |

|---|---|---|---|---|---|

| 144 | 24 | 168 | 36 | 12 | 0.96 |