ZHCAA80B December 2019 – April 2021 AFE7920 , AFE7921 , AFE7988 , AFE7989

6 接地域

- TI 强烈建议不同接地域的任意两个旁路电容器不得共享同一个接地过孔。表 6-1请参阅,了解通用接地域对特定 AFE79xx 器件接地网的参考。 表 6-1 AFE79xx 接地网描述

AFE79xx EVM 通用网名称 AFE79xx 器件电源引脚 网的说明 DGND DGND 数字内核电源接地 VSST 串行器/解串器数字内核电源接地 VSSGPIO GPIO 接地 ESD_GND ESD 保护电路接地 AGND VSSFB FB ADC 链信号接地 VSSRX RX ADC 链信号接地 VSSTX TX DAC 链信号接地 虚拟 VSSCLK 绑定到 AGND VSSFBCLK FB ADC 链时钟接地 VSSPLL PLL 接地 VSSPLLCLKREF 时钟参考接地 VSSPLLFBCML FB ADC 链时钟接地 VSSPLLRXCML RX ADC 链时钟接地 VSSRXCLK FB ADC 链时钟接地 VSSTXCLK TX DAC 链时钟接地 VSSTXENC TX DAC 链编码器接地 - 两个电源平面之间需要有足够的侧向间距(大约是平面厚度的三倍),以便更大限度地减少平面间耦合。或者,在两个电源平面之间使用接地过孔拼接,进一步减少平面间耦合。

- 图 6-1所有接地层在 AFE79xx 器件下面都必须有接地覆铜,使用一个缝隙来隔离数字接地和模拟接地,如 中所示。缝隙必须在器件封装的边界处结束,而器件封装区域外部必须有足够的接地覆铜。器件封装区域外部的接地覆铜使得数字接地和模拟接地可以维持接地连接和接地电势。一个接地平面上的任何噪声干扰或接地反弹必须先经过较大的接地覆铜,然后再到达另一个接地平面。接地覆铜必须通过 PCB 平面的去耦层(分别穿过顶层和底层以及第 2 层和第 11 层接地层)来吸收噪声和接地反弹。

注意:VSSCLK 被并入 AGND 中。图 6-1 接地缝隙和器件的引脚分配

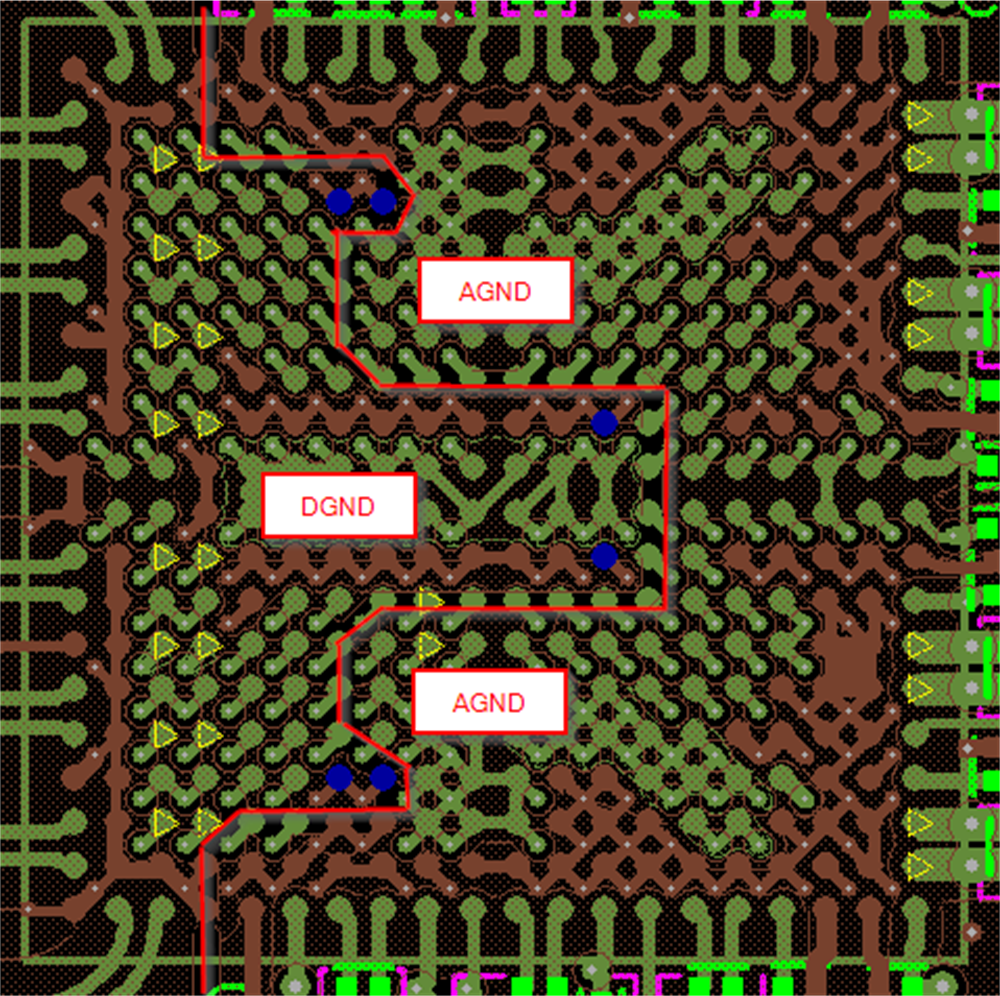

注意:VSSCLK 被并入 AGND 中。图 6-1 接地缝隙和器件的引脚分配 - 图 6-2 显示了模拟接地 (AGND)、数字接地 (DGND) 和理论时钟接地 (VSSCLK) 的接地切断策略。接地切断的目标是特意产生电感,以便一个接地域的噪声干扰不会立即影响另一个域的噪声质量。所有接地均在器件封装区域外部绑定在一起,以便维持接地电势。在这个 PCB 设计中,理论 VSSCLK 接地与 AGND 绑定在一起,其原因将在应用手册的后面部分讨论。

注意:VSSCLK 被并入 AGND 中。图 6-2 包含理论 VSSCLK 切断的接地切断策略示例

注意:VSSCLK 被并入 AGND 中。图 6-2 包含理论 VSSCLK 切断的接地切断策略示例 - 图 6-3 突出显示了常规接地域与器件引脚映射。此图可帮助系统设计人员了解接地切断和器件引脚映射。

图 6-3 DGND、AGND 和理论 CLK 接地区域与 AFE79xx 引脚映射。

图 6-3 DGND、AGND 和理论 CLK 接地区域与 AFE79xx 引脚映射。 - ESD 接地 (ESD_GND) 和 GPIO 接地 (VSSGPIO) 是数字接地切断 (DGND) 的一部分。图 6-4根据 AFE79xx EVM DGND 切断区域,ESD_GND 在 DGND 边界内,如 所示。图 6-5VSSGPIO 是 VDD1p8GPIO 的关联接地网,如 所示。VDD1p8GPIO 通常源自模拟 1.8V 电源轨中的共享 1.8V 电源。因此,系统设计人员必须检查从模拟电源到 VSSGPIO 接地的返回路径,确保获得足够的返回路径。

图 6-4 与 DGND 切断相关的 ESD_GND 焊球(显示为蓝色)

图 6-4 与 DGND 切断相关的 ESD_GND 焊球(显示为蓝色) 图 6-5 与 DGND 切断相关的 VSSGPIO 焊球和 VDD1p8GPIO 旁路电容器

图 6-5 与 DGND 切断相关的 VSSGPIO 焊球和 VDD1p8GPIO 旁路电容器理论上,可以用另一个缝隙来分隔 PLL 和时钟分布接地回路。最大限度地减少时钟接地以及 RX、FB 和 TX 接地的耦合,则有助于提高 RX、FB 和 TX 块内采样时钟的质量。如果有 RX、FB 或 TX 信号或噪声耦合到采样时钟上,则耦合的信号或噪声会将其本身调制到采样时钟上。在采样时钟受到污染的情况下,RX、FB 和 TX 信号拥有调制到其本身的已耦合信号。此类循环调制会产生谐波失真,并降低 AFE79xx 的噪声性能。图 6-6有关双音输出的自耦合在 TXDAC 输出时影响 IMD3 性能的示例,请查看 中的示例图。

图 6-6 双音输出的自耦合影响 TXDAC 的 IMD3 性能

图 6-6 双音输出的自耦合影响 TXDAC 的 IMD3 性能由于空间受限,此设计不包括时钟接地缝隙。引入时钟接地缝隙可降低总体有效接地面积。因此,引入接地缝隙的风险会大于收益。取而代之的是,对于时钟接地隔离我们进行了以下考虑:

- 时钟电源去耦并返回到 AGND。去耦电容器经过定向,可使一个引脚连接到时钟电源,另一个引脚(尽可能)直接连接到关联的时钟接地。例如,VDD1p2PLLCLKREF(REFCLK± 时钟接收器的电源)有 VSS1p2PLLCLKREF 的关联时钟接地。

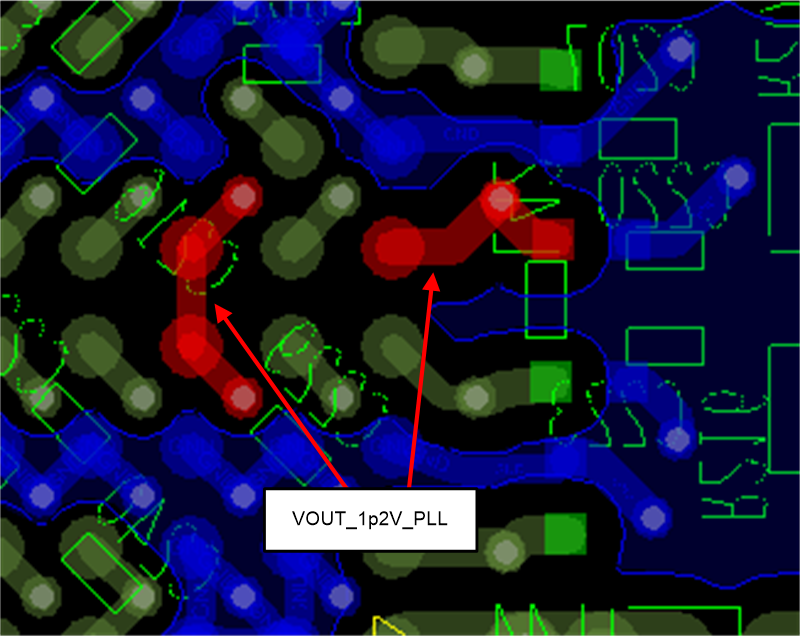

- 为了减少由过孔引入的电感,在顶层布置以下时钟电源网:VOUT_1p8CLK、VOUT_1p2_CLK、PLLA1p8V 和 VOUT_1p8_PLL.有关详细信息,请参阅本文之前的部分。

- 图 6-7 演示了 VDD1P2PLLCLKREF(REFCLK± 时钟接收器的电源)的去耦电容器定向。这种布线方法具有从 VDD1P2PLLCLKREF 到 VSSPLLCLKREF 引脚的直接连接。

VOUT_1p2V_PLL 布置在顶层,可最大限度地减少去耦路径所用的过孔数量。图 6-7 VOUT_1p2V_PLL 布线示例

VOUT_1p2V_PLL 布置在顶层,可最大限度地减少去耦路径所用的过孔数量。图 6-7 VOUT_1p2V_PLL 布线示例 - PLL_LDOUT 是片上 PLL 的内部 LDO。0.1µF 电容器必须在时钟接地区域附近进行绑定。由于 PLL_LDOUT 网与内部 PLL/VCO/时钟电路相关,电阻器端接的返回路径必须直接布置到位于引脚 J18 的 VSSPLLCLKREF 引脚。

图 6-8 PLL_LDOUT 0.1µF 电容器从引脚 J19 (PLL_LDOUT) 路由到引脚 J18 (VSSPLLCLKREF)

图 6-8 PLL_LDOUT 0.1µF 电容器从引脚 J19 (PLL_LDOUT) 路由到引脚 J18 (VSSPLLCLKREF) - 如果 PCB 设计有一个通用 1.8V 电源共享到多个 AFE79xx PLLA1p8V (VDD1p8PLLVCO) 网,则 VDD1p8PLLVCO 网必须有足够的滤波,以防多个 AFE79xx VCO 串扰和 VCO 拉取机制通过通用电源节点。图 6-9有关滤波建议,请参阅。

图 6-9 电源网隔离滤波器

图 6-9 电源网隔离滤波器