ZHCAAA1A December 2017 – May 2021 AM3351 , AM3352 , AM3354 , AM3356 , AM3357 , AM3358 , AM3358-EP , AM3359 , AM4372 , AM4376 , AM4377 , AM4378 , AM4379 , AM5706 , AM5708 , AM5716 , AM5718 , AM5718-HIREL , AM5726 , AM5728 , AM5729 , AM5746 , AM5748 , AM5749 , DP83822H , DP83822HF , DP83822I , DP83822IF , DP83825I

3 PHY 速度、双工等

PHY 复位后,可以针对所需工作模式使用 MDIO 对其进行配置。AMIC110 中 PRU-ICSS 内的 MDIO 采用 802.3 串行管理接口 (SMI),可通过使用共享双线总线同时询问和控制两个以太网 PHY。DP83822 器件中的 SMI 符合 IEEE 802.3 第 22 条和第 45 条的要求,可访问其内部寄存器空间,包括标准寄存器组 0 至 31、采用寄存器控制寄存器(REGCR,地址 0x000D)的扩展寄存器组以及数据寄存器(ADDAR,地址 0x000E),以获取状态信息和配置。

以太网自动协商功能提供了一种机制,可通过突发脉冲在链路段两端之间交换配置信息,如速度和双工。自动协商功能可确保根据链路伙伴和本地器件的广播能力选择最高性能协议。可在硬件中使用 AN_EN 自举启用或禁用自动协商功能,也可使用基本模式控制寄存器(BMCR,地址 0x0000)中的位 [12] 并通过寄存器配置来启用或禁用该功能。

在 PRU-ICSS EtherCAT 软件中,使用 MDIO 的 PHY 初始化的调用流程如下:

Phy_reset( )

|

Task_create(task1,&taskParams, NULL);

|

BIOS_start();

其中 MDIO 和 PHY 初始化是在 task1 中执行:

task1() -> Hw_init( ) --> bsp_init( ) -> bsp_pruss_mdio_init( ) -> bsp_ethphy_init( )

Hw_init( ) – EtherCAT 从接口初始化

bsp_init() – PRU 初始化

使用 CSL 函数 CSL_MDIO_init() 通过 bsp_pruss_mdio_init() 对 MDIO 进行初始化,其中输入和输出时钟用作参数。

/** ============================================================================

* @n@b CSL_MDIO_init

*

* \brief 此 API 初始化 MDIO 外设。这可启用 MDIO 状态

* 机,使用标准前导码并设置时钟分频器值。

*

* \param baseAddr MDIO 模块的基地址。

* \param mdioInputFreq MDIO 模块的时钟输入。

* \param mdioOutputFreq MDIO 总线上所需的时钟输出。

* =============================================================================

*/

static inline void CSL_MDIO_init(uint32_t baseAddr,

uint32_t mdioInputFreq,

uint32_t mdioOutputFreq);

MDIO PRU 固件与 PHY 通信时需要对 PRU-ICSS 进行初始化,因此必须在 PRU-ICSS 域上电之后执行 PRU-ICSS 的初始化,然后在两个 PRU 上加载并执行 PRU 固件。

MDIO 完成初始化后,可以通过 CSL 函数 CSL_MDIO_phyRegRead() 和 CSL_MDIO_phyRegWrite() 访问 PHY,以配置以下内容:

- 连接速度、双工和自动协商

- 自动 MDIX,可确定是使用直通电缆还是交叉电缆来与链路伙伴相连。

- 扩展全双工模式。在扩展全双工模式下,当 PHY 设置为自动协商或 Force 100Base-TX,且链路伙伴在 Force 100Base-TX 模式下运行时,链路始终为全双工模式。禁用后,决定是在全双工还是半双工模式下工作时要遵循 IEEE 规范 – 半双工。

- 在奇半字节边界中检测到传输错误,该错误使 TX_EN 扩展一个额外的 TX_CLK 周期,并且其行为就好像在该额外周期中置位了 TX_ER 一样。

- 其他功能(如奇半字节插入和快速链路断开检测)如下所述:

/** ============================================================================

* @n@b CSL_MDIO_phyRegRead

*

* \param baseAddr MDIO 模块的基地址。

* \param phyAddr PHY 地址。

* \param regNum 要读取的寄存器编号。

* \param pData 写入读取值的指针。

*

* \retval TRUE 读取成功。

* \retval FALSE 未正确确认读取。

* =============================================================================

*/

static inline Uint32 CSL_MDIO_phyRegRead(uint32_t baseAddr,

Uint32 phyAddr,

Uint32 regNum,

Uint16 *pData)

/** ============================================================================

* @n@b CSL_MDIO_phyRegWrite

*

* \brief 此 API 使用 MDIO 写入一个 PHY 寄存器。

*

* \param baseAddr MDIO 模块的基地址。

* \param phyAddr PHY 地址。

* \param regNum 要写入的寄存器编号。

* \param wrVal 要写入的值。

* =============================================================================

*/

static inline void CSL_MDIO_phyRegWrite(uint32_t baseAddr,

uint32_t phyAddr,

uint32_t regNum,

uint16_t wrVal);

大多数 MDIO PHY 配置函数都集成在 Processor SDK 的电路板库中。

例如,若要启用 0x0019 PHY 控制寄存器 (PHYCR) 中的自动 MDIX 位,请参阅以下内容:

Board_enablePhyAutoMDIX((((PRUICSS_HwAttrs *)(pruIcssHandle->hwAttrs))->prussMiiMdioRegBase), pmdio_params->addr0);

若要启用 0x000A 控制寄存器 2 (CR2) 中的扩展全双工模式位,请参阅以下内容:

Board_phyExtFDEnable((((PRUICSS_HwAttrs *)(pruIcssHandle->hwAttrs))->prussMiiMdioRegBase), phy0addr);

要启用 0x000A 控制寄存器 2 (CR2) 中的奇半字节插入位,请参阅以下内容:

Board_phyODDNibbleDetEnable((((PRUICSS_HwAttrs *)(pruIcssHandle->hwAttrs))->prussMiiMdioRegBase), phy0addr);

用户也可以直接调用 CSL 函数来管理 PHY,例如关闭 RMII 模式并选择 MII 模式,具体请参阅以下内容:

phyregval = 0;

CSL_MDIO_phyRegWrite((((PRUICSS_HwAttrs *)(pruIcssHandle->hwAttrs))->prussMiiMdioRegBase), pmdio_params->addr0, TLKPHY_RCSR_REG, phyregval);

使用 Code Composer Studio™ 中的内存浏览器或寄存器窗口通过 USERACCESS0/1 寄存器读取 PHY 和写入 PHY,这是对 PHY 问题进行故障排除的一种有效现场调试功能(请参阅 表 3-1)。

| 位 | 字段 | 类型 | 复位 | 说明 |

|---|---|---|---|---|

| 31 | GO | R/W/S | 0 | Go.向此位写入 1 会使 MDIO 状态机在其方便时执行 MDIO 访问(这不是一个瞬间过程)。将 0 写入此位无影响。仅当启用了 MDIO 状态机时,此位才可写。当请求的访问完成后,此位将自行清除。当 GO 位为 1 时,系统将阻止对 MDIOUSERACCESS0 寄存器的任何写入。如果使用的是字节访问,则应最后写入 GO 位。 |

| 30 | WRITE | R/W | 0 | 写入启用。将此位设为 1 会使 MDIO 事务成为一个寄存器写入,否则为一个寄存器读取。 |

| 29 | ACK | R/W | 0 | 确认。如果 PHY 确认了读取事务,则设置此位。 |

| 28:26 | 保留 | R | 0 | 保留 |

| 25:21 | REGADR | R/W | 0 | 寄存器地址。指定此事务要访问的 PHY 寄存器。 |

| 20:16 | PHYADR | R/W | 0 | PHY 地址。指定此事务要访问的 PHY。 |

| 15:0 | 数据 | R/W | 0 | 用户数据。从指定 PHY 寄存器读取或写入该寄存器的数据值。 |

若要在内存浏览器或寄存器窗口中读取 PHY,请执行以下步骤:

- 确保将 MDIO 用户访问寄存器 (MDIOUSERACCESSn) 中的 GO 位清除。

- 在 MDIOUSERACCESSn 中写入与要读取的 PHY 和 PHY 寄存器相对应的 GO、REGADR 和 PHYADR 位。

- 当模块在串行总线上完成读取操作后,读取的数据值在 MDIOUSERACCESSn 的 DATA 位中可用。可通过轮询 MDIOUSERACCESSn 中的 GO 和 ACK 位来确定读取操作的完成情况。当 GO 位执行清除操作时,系统将在成功读取后设置 ACK 位。

若要在内存浏览器或寄存器窗口中写入 PHY,请执行以下步骤:

- 确保将 MDIO 用户访问寄存器 (MDIOUSERACCESSn) 中的 GO 位清除。

- 写入 MDIOUSERACCESSn 中与要写入的 PHY 和 PHY 寄存器相对应的 GO、WRITE、REGADR、PHYADR 和 DATA 位。

- 对 PHY 的写入操作由 MDIO 模块进行安排并完成。可以通过轮询 MDIOUSERACCESSn 中的 GO 位为 0 来确定写入操作的完成情况。

若要验证 PHY 是否成功连接,用户可以查看基地址偏移处的 MDIOALIVE 和 MDIOLINK 寄存器 0x04 和 0x08。

如果 PHY 确认了对 PHY 的最近一次访问,则设置 MDIOALIVE 寄存器的 32 位中的每一位,其地址对应于寄存器位数。如果 PHY 无法确认该次访问,则会将该位复位。对 PHY 的用户访问和轮询访问都会导致对相应活动位的更新。这些活动位仅用于用相应地址表示 PHY 的存在或缺失。对任何位写入 1 都会将该位清除;写入 0 则无影响。

读取 PHY 的状态寄存器后,MDIOLINK 寄存器将更新。如果 PHY 与相应地址的链路接通,并且 PHY 确认读取事务,则设置该位。如果 PHY 指示它没有链路或无法确认读取事务,则将该位复位。写入寄存器无影响。此外,可以使用 MLINK 输入引脚来确定 MDIOUSERPHYSELn 寄存器中指定的两个 PHY 的状态。此选择由 MDIOUSERPHYSELn 寄存器中的 LINKSEL 位确定。

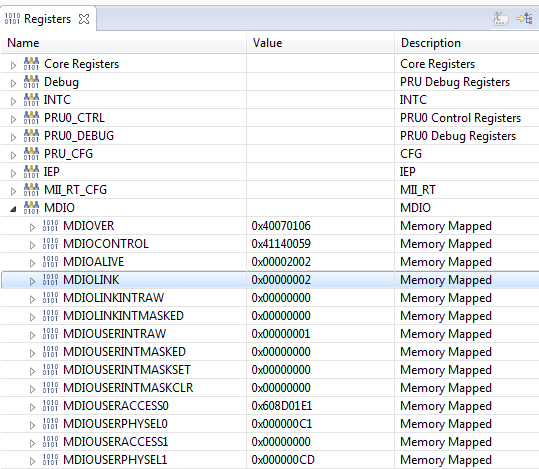

图 3-1 显示了在 AMIC110 ICE 上捕获的 Code Composer Studio PRU 寄存器窗口的一个快照。此快照指示存在两个 PHY (MDIOALIVE = 0x0002002),并且具有地址 0x1 链路的 PHY 已接通 (MDIOLINK = 0x00000002)。

图 3-1 Code Composer Studio 中的 MDIO 寄存器

图 3-1 Code Composer Studio 中的 MDIO 寄存器TI 的 EtherCAT 实现中提供了多个 PRU-ICSS MDIO 主机 API,这些 API 可用于读取/写入 PHY 寄存器以及查询 PHY 链路状态。例如,请参阅以下内容:

Int16 bsp_pruss_mdio_phy_read (Uint8 phyaddr, Uint8 regoffset, Uint16 *regval);参数:

- phyaddr – 使用 PHY 地址选择要读取的 PHY

- regoffset – 要读取的 PHY 中的寄存器偏移

- regval – 指针,指向用于保存已读取寄存器值的变量

- 返回值

- 0: 成功

- –1:MDIO 访问错误

Int16 bsp_pruss_mdio_phy_write (Uint8 phyaddr, Uint8 regoffset, Uint16 regval);参数:

- phyaddr – 使用 PHY 地址选择要写入的 PHY

- regoffset – 要读取的 PHY 中的寄存器偏移

- regval – 要写入 PHY 寄存器的值

- 返回值

- 0: 成功

- –1:MDIO 访问错误

Uint32 bsp_pruss_mdio_phy_link_state (Uint8 phyaddr);参数:

- phyaddr – 选择 PHY 以获取链路状态

- 返回值

- 0: 链路断开

- 否则:链路接通

bsp_pruss_mdio_phy_link_state( ) API 考虑 MII_LINK 信号极性差异,建议在启用 TIESC_MDIO_RX_LINK_ENABLE 的情况下使用该 API 来增强链路检测。