ZHCAAB0A April 2021 – December 2021 TMS320F2800132 , TMS320F2800133 , TMS320F2800135 , TMS320F2800137 , TMS320F280021 , TMS320F280021-Q1 , TMS320F280023 , TMS320F280023-Q1 , TMS320F280023C , TMS320F280025 , TMS320F280025-Q1 , TMS320F280025C , TMS320F280025C-Q1 , TMS320F280033 , TMS320F280034 , TMS320F280034-Q1 , TMS320F280036-Q1 , TMS320F280036C-Q1 , TMS320F280037 , TMS320F280037-Q1 , TMS320F280037C , TMS320F280037C-Q1 , TMS320F280038-Q1 , TMS320F280038C-Q1 , TMS320F280039 , TMS320F280039-Q1 , TMS320F280039C , TMS320F280039C-Q1 , TMS320F280040-Q1 , TMS320F280040C-Q1 , TMS320F280041 , TMS320F280041-Q1 , TMS320F280041C , TMS320F280041C-Q1 , TMS320F280045 , TMS320F280048-Q1 , TMS320F280048C-Q1 , TMS320F280049 , TMS320F280049-Q1 , TMS320F280049C , TMS320F280049C-Q1 , TMS320F28075 , TMS320F28075-Q1 , TMS320F28076 , TMS320F28374D , TMS320F28374S , TMS320F28375D , TMS320F28375S , TMS320F28375S-Q1 , TMS320F28376D , TMS320F28376S , TMS320F28377D , TMS320F28377D-EP , TMS320F28377D-Q1 , TMS320F28377S , TMS320F28377S-Q1 , TMS320F28378D , TMS320F28378S , TMS320F28379D , TMS320F28379D-Q1 , TMS320F28379S , TMS320F28384D , TMS320F28384D-Q1 , TMS320F28384S , TMS320F28384S-Q1 , TMS320F28386D , TMS320F28386D-Q1 , TMS320F28386S , TMS320F28386S-Q1 , TMS320F28388D , TMS320F28388S , TMS320F28P650DH , TMS320F28P650DK , TMS320F28P650SH , TMS320F28P650SK , TMS320F28P659DH-Q1 , TMS320F28P659DK-Q1 , TMS320F28P659SH-Q1

3.1 ADC 中断响应延迟

中断延迟是了解实时系统响应时间的重要因素。评估系统中断延迟的典型方法是计算硬件响应中断并跳转到中断矢量(硬件锁存和响应)所需的周期数。但是,在实时应用中,此时间只是响应延迟的一部分。

考虑到无传感器 ACI 电机基准测试应用程序,PWM 促使 ADC 开始采样。ADC 需要一定数量的周期才能完成采样或转换,具体数量取决于系统配置以及 ADC 功能。ADC 准备就绪后,将产生中断。在 ACI 电机基准测试中, ADC 配置为产生早期中断,即在采样完成之后以及转换开始时(而不是转换结束时)产生中断。ADC 产生中断后,硬件对中断做出响应,并跳转到中断矢量。然而,中断服务例程不会立即开始执行用户代码,而是在此之前必须执行一些编译器生成的上下文保存,然后再执行用户代码。

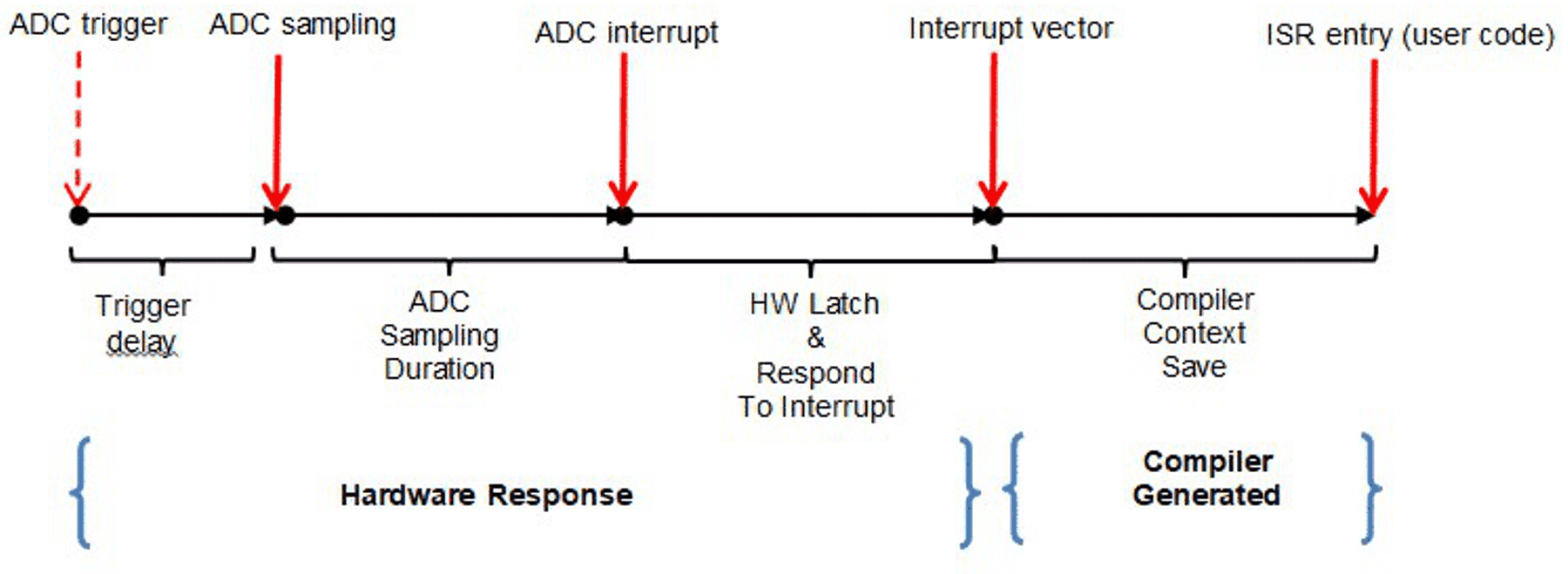

实际上,如图 3-1 所示,实际中断延迟包含四个部分:触发延迟 + ADC 采样持续时间 + 硬件锁存和响应 + 编译器生成的上下文保存。

图 3-1 ACI 电机基准测试中断响应分量

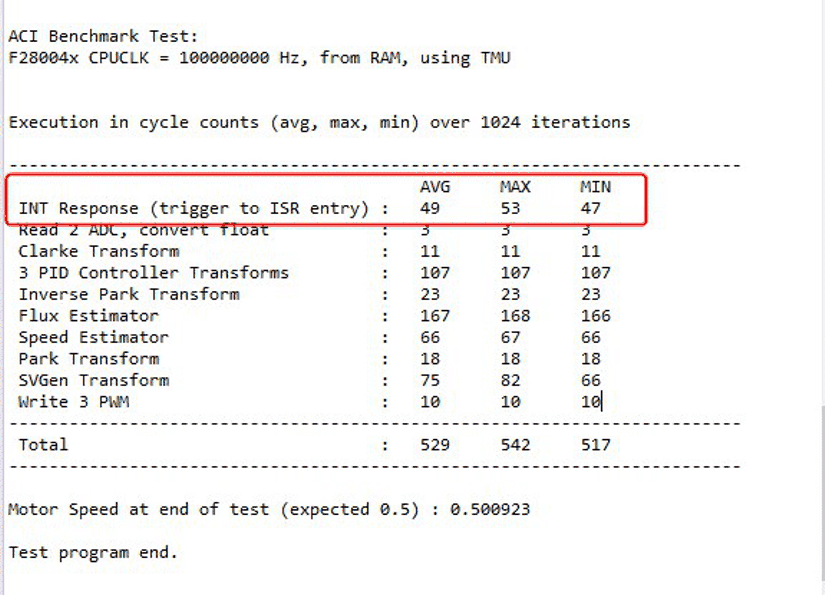

图 3-1 ACI 电机基准测试中断响应分量ACI 实时基准测试将此值输出为“INT Response (trigger to ISR entry)”。从图 3-2 中可以看出,C28x INT 响应时间平均为 49 个周期,表示在无传感器 ACI 电机示例中,应用程序开始响应感测事件的实际延迟。传统基准测试不会以此方式测量系统。INT 响应周期在最小值和最大值之间的差异是可以预期的,因为在 CPU 接收异步中断事件之前,可能还需要额外的周期来完成正在进行的后台指令。

图 3-2 ACI 电机基准测试中断响应基准测试数据

图 3-2 ACI 电机基准测试中断响应基准测试数据表 3-1 列出了每个单独元素的理论估计影响值,并且可以看出总周期数与应用程序基准测试获得的最小周期数一致。

| 触发延迟 (1) | ADC 采样持续时间 (2) | 硬件锁存和响应(3) | 编译器上下文保存(4) | 总计(周期数) |

|---|---|---|---|---|

| 2 | 8 | 14 | 23 | 47 |

查看影响总周期数的各个组件,可以看出 PWM 和 ADC 紧密集成,并且触发延迟也带来了几个额外的周期。ADC 早期中断产生特性允许系统响应中断时并行进行 ADC 转换。这样允许转换周期与中断产生和编译器上下文保存周期重叠,从而减少响应 ADC 采样事件所需的总时间。相比之下,对于任何其他不具有 ADC 早期中断产生特性的系统,中断响应将包括转换周期,因此会增加总响应时间。此特性的另一个优点是,ADC 结果可在时间更接近采样时间时应用于系统,从而实现更精确的系统控制。