ZHCAAH9A September 2020 – March 2022 BQ769142 , BQ76942 , BQ76952

8 DSG 驱动器

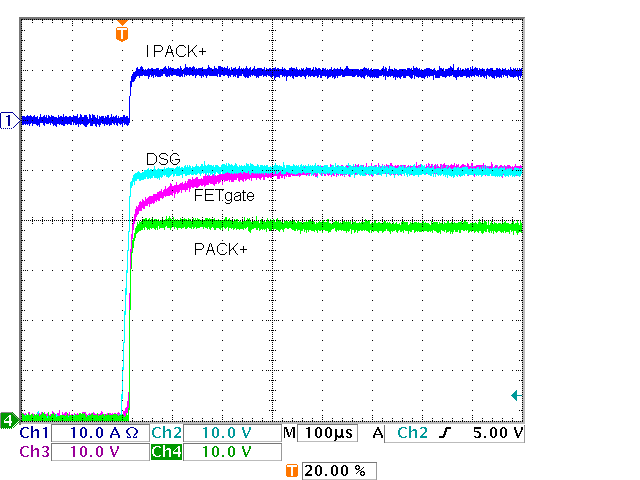

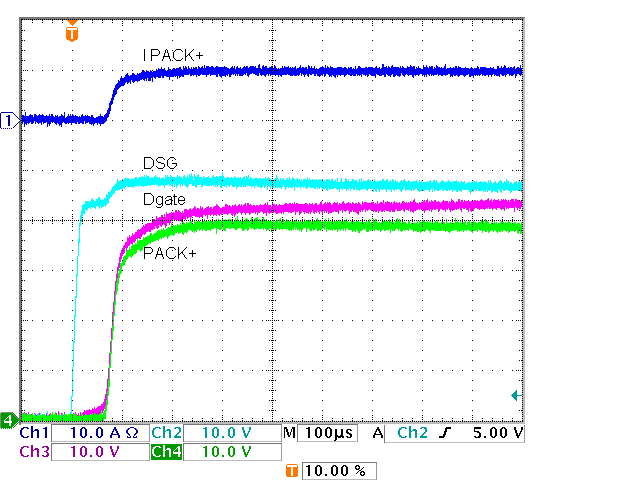

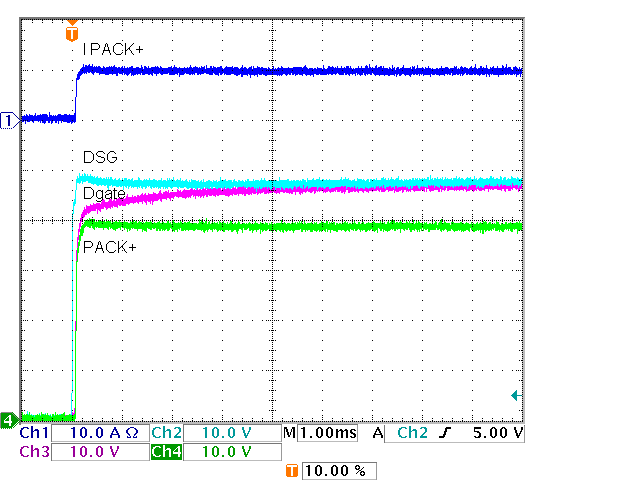

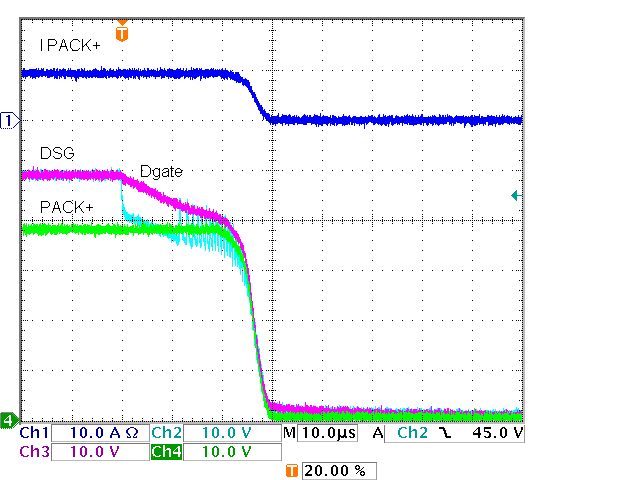

放电驱动器在 VSS 和 CP1 电压之间运行。当驱动器打开时,随着电流流过图 5-1 的 R45 和 R40,DSG 上升至 CP1 电压。R45 和 R40 提供了 10kΩ 导通电阻。图 8-1 所示为单个 FET 导通示例。随着 FET 导通,PACK+ 上升且电流流入放电 FET。由于导通电阻和栅极电容的滤波效应,栅极电压将滞后于 DSG 电压。

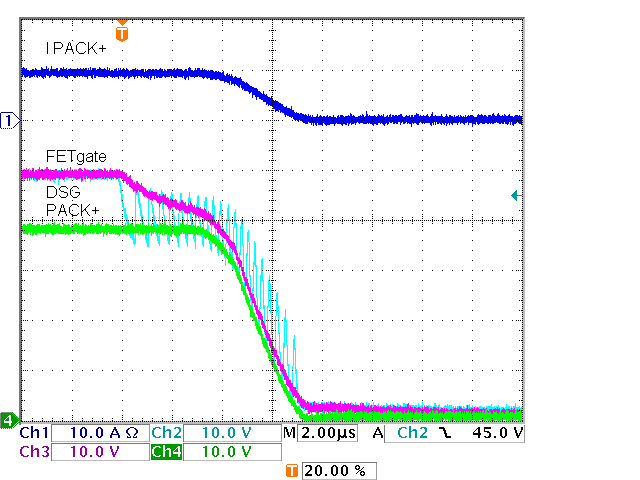

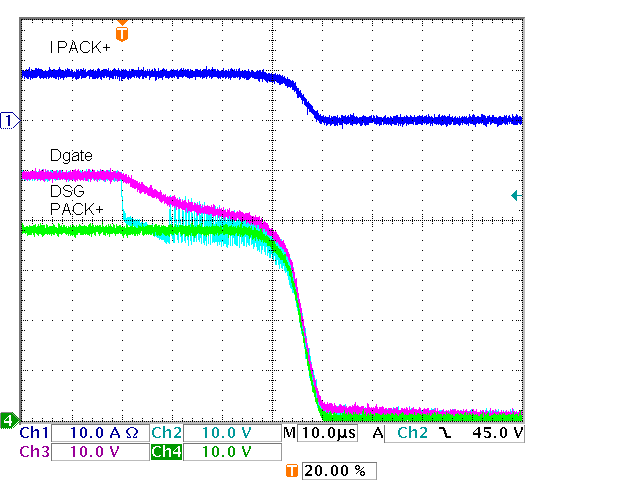

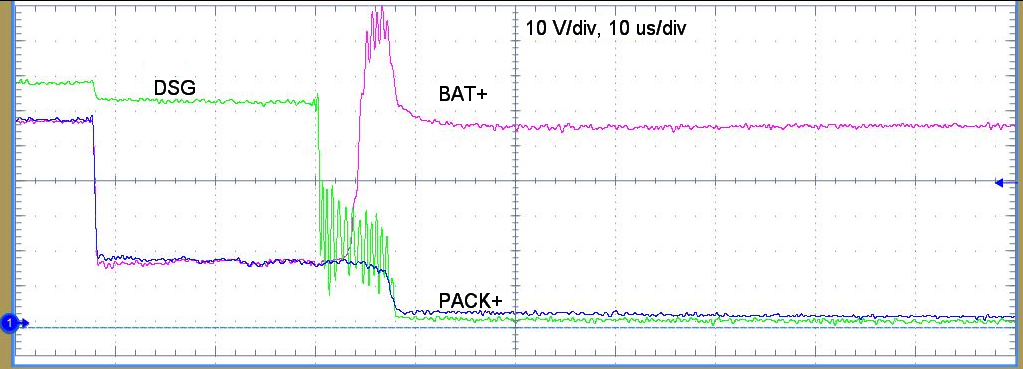

当 DSG 驱动器被触发关断时,该器件将最先开始趋向 VSS 对 DSG 引脚放电。但是,PACK+ 端子可能不会很快下降到接近 VSS 的电压,因此不应将 DSG FET 栅极驱动到显著低于 PACK+ 的电压,否则 DSG FET 可能会因栅源负电压过高或者 DSG 引脚尝试通过栅源电阻器或齐纳二极管将 PACK+ 放电而受损。因此,器件监控 LD 引脚(通过外部串联电阻器连接到 PACK+)上的电压,并在 DSG 引脚电压低于 LD 引脚电压时停止放电。当放电停止时,引脚电压可能会释放,回到 LD 引脚电压以上,此时器件将再次趋向 VSS 对 DSG 引脚放电,直到 DSG 栅极电压再次降至 LD 引脚电压以下。此过程在一系列脉冲中重复,这些脉冲随着时间的推移将 DSG 栅极放电至 LD 引脚的电压。该脉冲持续约 200μs。在这之后,如果低于 LD 的引脚电压加上约 500mV,驱动器将保持高阻抗状态。然后,DSG 栅极和源极之间的外部电阻器将剩余电压释放,使 FET 保持关断。

图 8-2 展示了一个关断示例。DSG 拉低从 FET 的栅极通过肖特基二极管 D7 和 R41 获取的电流。额外的电流会流过 R40 和 R45。流入 DSG 引脚的电流被发送到 VSS 引脚,而不是流出 LD 引脚。 图 8-1 和图 8-2 展示的是单个 FET 的栅极电压,而非公共栅极网络电压,因为只有 1 个 FET。

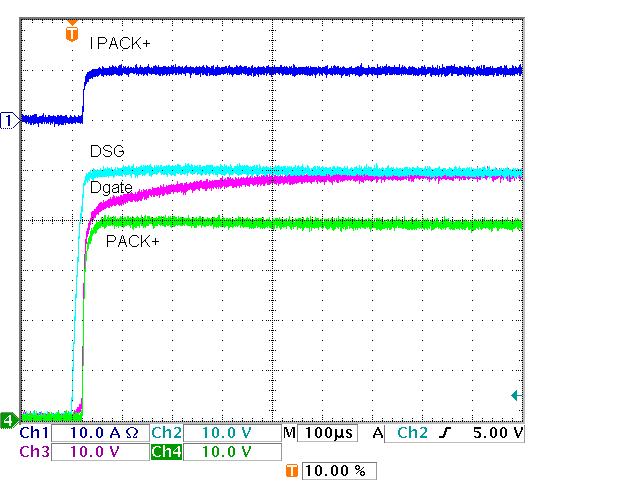

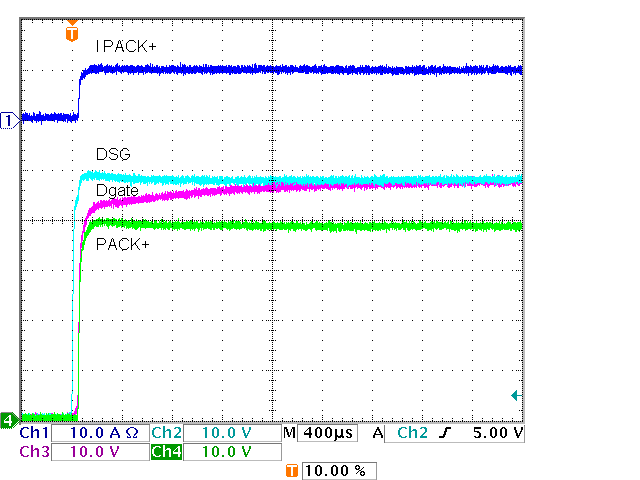

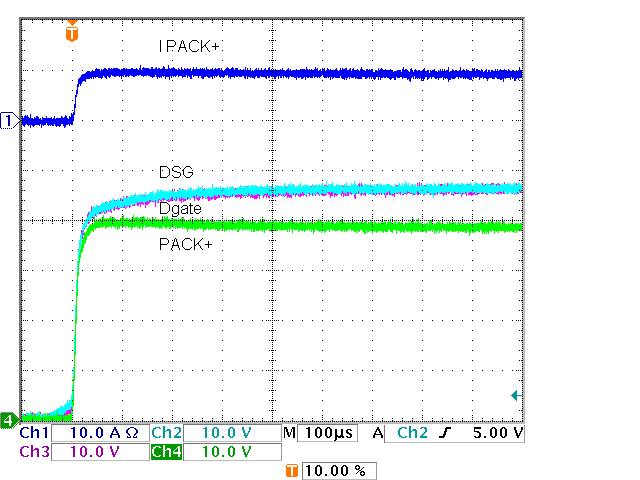

图 8-1 DSG 导通,单个 FET,10kΩ,470nF

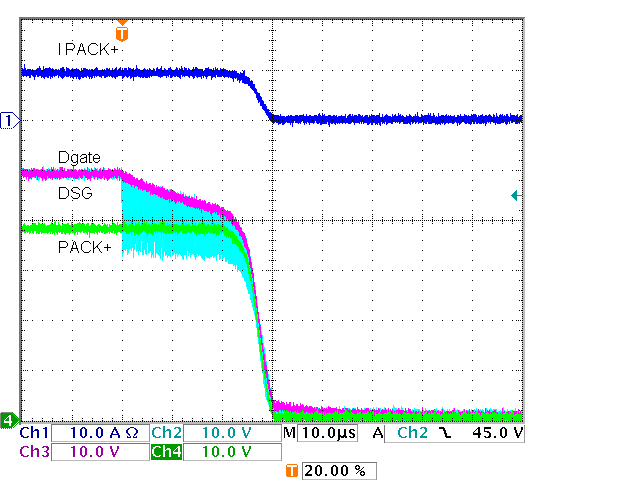

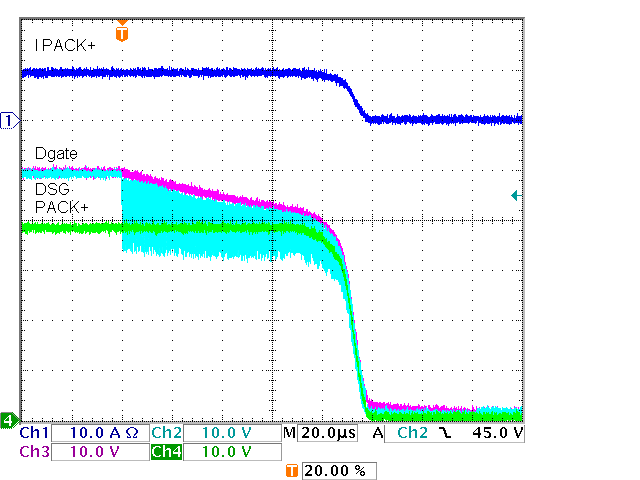

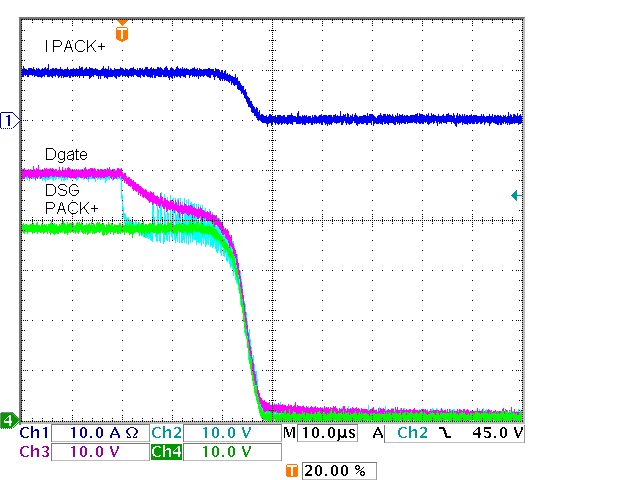

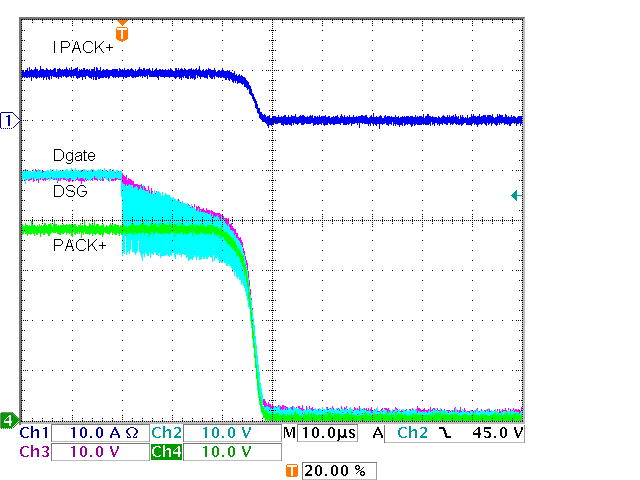

图 8-1 DSG 导通,单个 FET,10kΩ,470nF 图 8-2 DSG 关断,单个 FET,R41 100Ω

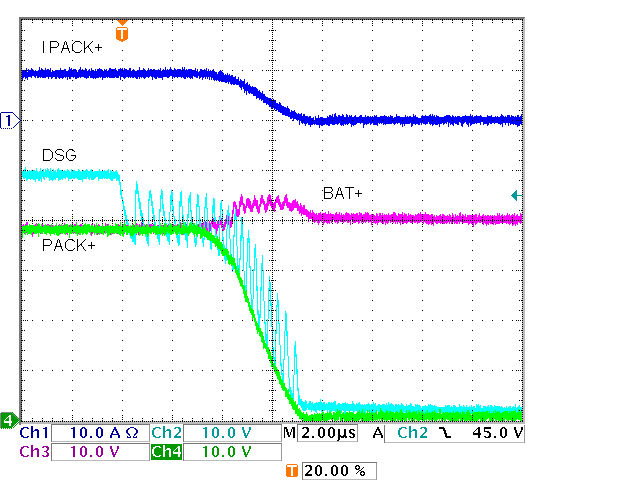

图 8-2 DSG 关断,单个 FET,R41 100Ω检查图 8-3 中的电池电压,脉冲的作用是避免快速关断以及由此产生的大电感尖峰。设计人员必须选择适合电池电感的关断速度。在此测试电流下,电池电压上升了 4V,较大的 R41 值将被用于进行低 FET 计数比较。

图 8-3 具有单个 FET,R41 100Ω 的电池瞬态

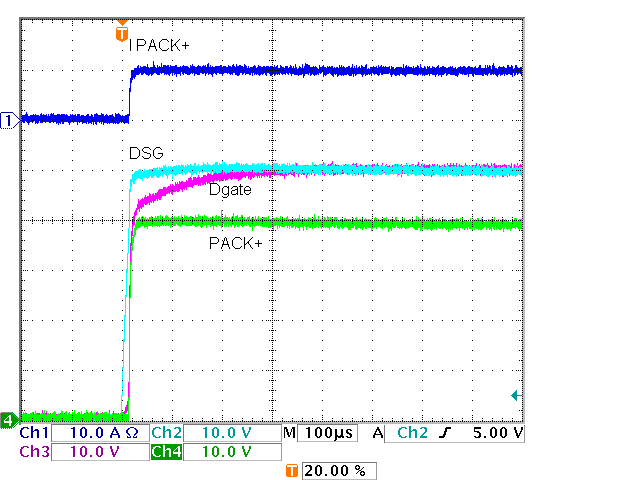

图 8-3 具有单个 FET,R41 100Ω 的电池瞬态图 8-4 至图 8-9 展示了反向充电电路的导通和关断示例(R41 为 1kΩ、分别具有 1 至 4 个 FET)。单个 FET 的导通与 R41 100Ω 的情况类似,因为肖特基二极管在导通期间阻止 R41 中的电流流动。在图 8-4 中,受到监控的是公共栅极网络,而非单个 FET 栅极。

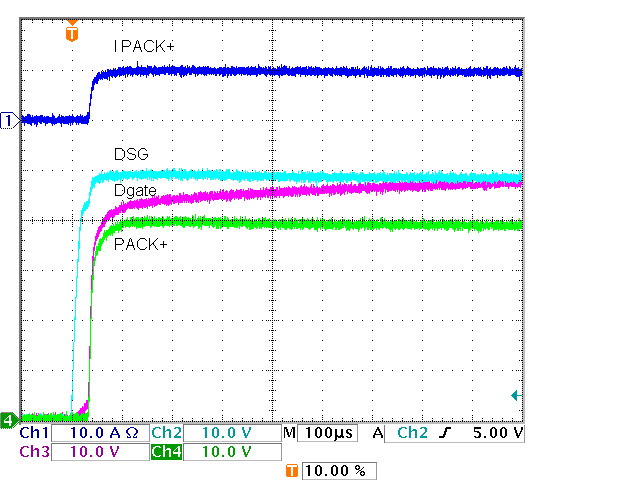

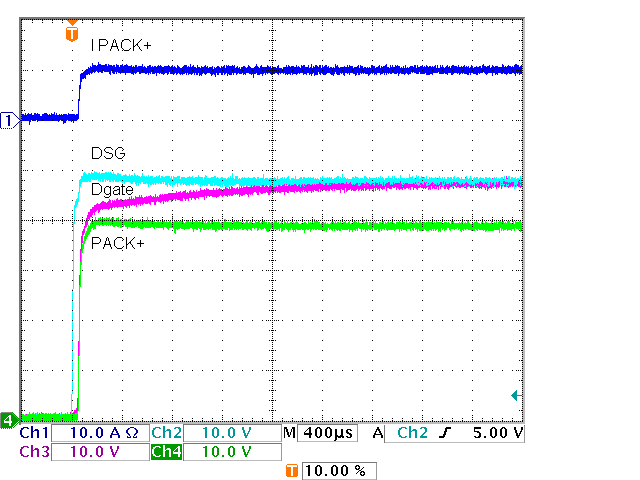

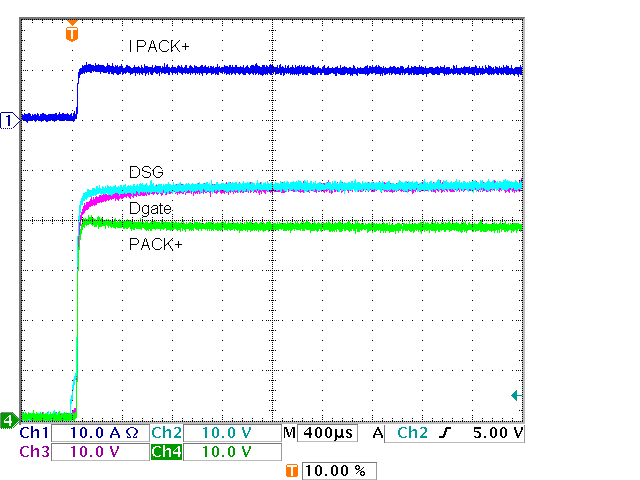

图 8-4 DSG 导通,单个 FET,10kΩ,470nF

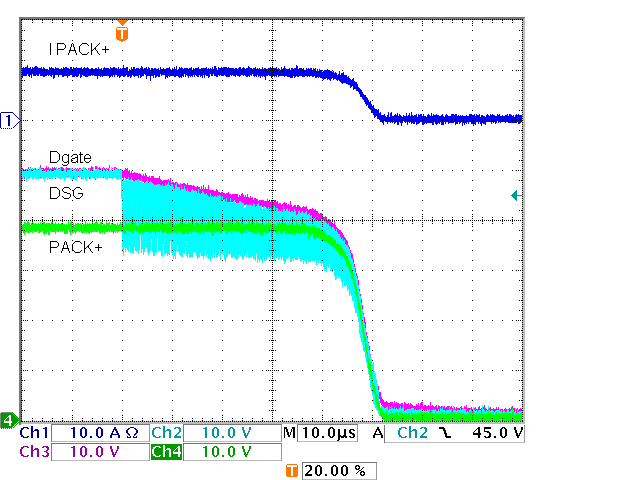

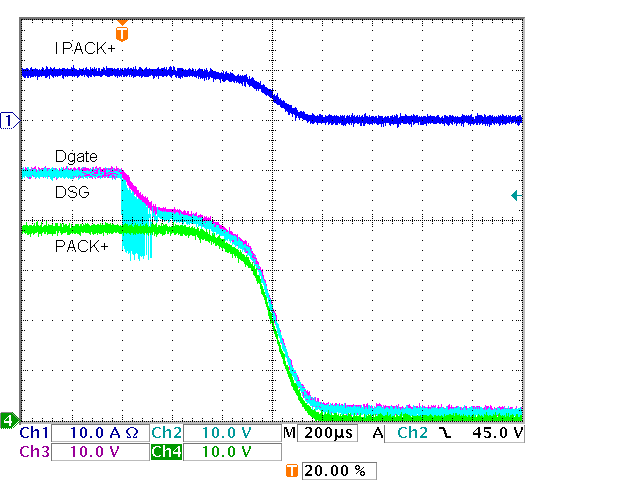

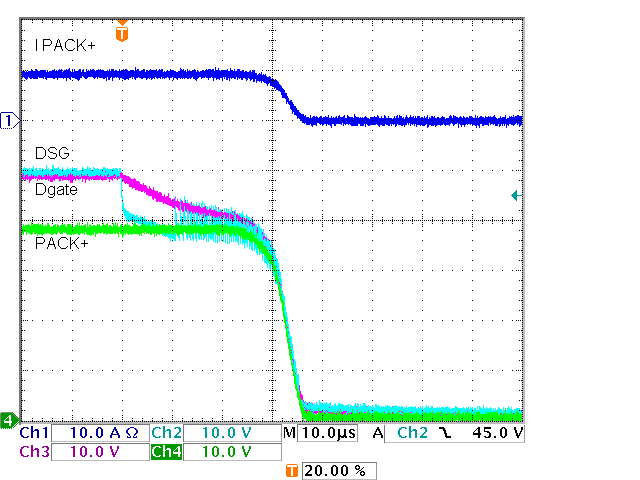

图 8-4 DSG 导通,单个 FET,10kΩ,470nF 图 8-5 DSG 关断,单个 FET,R41 1kΩ

图 8-5 DSG 关断,单个 FET,R41 1kΩ 图 8-6 DSG 导通,2 个 FET,10kΩ,470nF

图 8-6 DSG 导通,2 个 FET,10kΩ,470nF 图 8-7 DSG 关断,2 个 FET,R41 1kΩ

图 8-7 DSG 关断,2 个 FET,R41 1kΩ 图 8-8 DSG 导通,4 个 FET,10kΩ,470nF

图 8-8 DSG 导通,4 个 FET,10kΩ,470nF 图 8-9 DSG 关断,4 个 FET,R41 1kΩ

图 8-9 DSG 关断,4 个 FET,R41 1kΩ使用 8 个 FET 时,栅极电容促进了导通时 DSG 和 Dgate 网络的分离,并减缓了上升,如图 8-10 所示。在图 8-11 中,在 DSG 输出的脉冲时间内,FET 不会关断,而是在 DSG 弱下拉之后关断。关断时间明显延长,且关断缓慢。设计中应避免这种状况。

图 8-10 DSG 导通,8 个 FET,10kΩ,470nF

图 8-10 DSG 导通,8 个 FET,10kΩ,470nF 图 8-11 DSG 关断,8 个 FET,R41 1kΩ

图 8-11 DSG 关断,8 个 FET,R41 1kΩ用于 DSG 的较小下拉电阻器可能不适用于 FET 数量较少的情况,但在 FET 数量较多时会使关断时间增加。在图 8-12 和图 8-13 中,R41 恢复为 100Ω。导通不会变化,但关断速度得以提高。图 8-14 和图 8-15 中展示了采用此配置开关 12 个 FET 的情况。

图 8-12 DSG 导通,8 个 FET,10kΩ,470nF

图 8-12 DSG 导通,8 个 FET,10kΩ,470nF 图 8-13 DSG 关断,8 个 FET,R41 100Ω

图 8-13 DSG 关断,8 个 FET,R41 100Ω 图 8-14 DSG 导通,12 个 FET,10kΩ,470nF

图 8-14 DSG 导通,12 个 FET,10kΩ,470nF 图 8-15 DSG 关断,12 个 FET,R41 100Ω

图 8-15 DSG 关断,12 个 FET,R41 100Ω对于给定的栅极下拉电阻,添加 FET 会增加电容,并减慢 DSG 引脚初始下降(这是其内部电阻和栅极转换导致的)的转换速度。这种影响很难通过 PACK+ 转换来识别。下表显示了为各种 FET 数量收集的典型值,其中使用 R41 100Ω 将 PACK+ 连接到 BAT+。下降时间为从 90% 到 10%,测量的是示例 FET 栅极而非 Dgate 网络。

| FET 数量 | Ciss 之和,nF | DSG 初始下降时间,us | 示例 FET 栅极下降时间,us |

|---|---|---|---|

| 1 | 9.25 | 0.50 | 6.4 |

| 2 | 18.5 | 1.0 | 9.6 |

| 4 | 37 | 1.4 | 16 |

| 6 | 55.5 | 2.3 | 21 |

| 8 | 74 | 5.0 | 27 |

| 10 | 92.5 | 6.7 | 33 |

| 12 | 111 | 7.2 | 39 |

在上图中,DSG 引脚直接对栅极电容放电。通过 DSG 引脚控制,PNP 晶体管可用于对栅极电容放电,如图 5-2 所示。图 8-16 和图 8-17 展示了此电路采用 12 个放电 FET 的导通和关断情况。

图 8-16 DSG 导通,12 个 FET,10kΩ,PNP,470nF

图 8-16 DSG 导通,12 个 FET,10kΩ,PNP,470nF 图 8-17 DSG 关断,12 个 FET,R41 1kΩ,PNP

图 8-17 DSG 关断,12 个 FET,R41 1kΩ,PNP读者已经观察到,随着 FET 数量的增加,导通所需的时间也会增加。这是因为 10kΩ 电阻(R40、R45)可在反向充电条件下将电阻器中的功率保持在合理水平。如果不需要反向充电电路,DSG 可以连接到公共栅极点,用单个电阻器替换图 5-1 的连接网络。肖特基二极管、R40 和 R45、反向充电钳位晶体管和相关元件均已省去。请参阅图 8-18。图 8-19 和图 8-20 中展示了开关情况。

图 8-19 DSG 导通,12 个 FET,100Ω,没有反向充电电路,470nF

图 8-19 DSG 导通,12 个 FET,100Ω,没有反向充电电路,470nF 图 8-20 DSG 关断,12 个 FET,100Ω,没有反向充电电路

图 8-20 DSG 关断,12 个 FET,100Ω,没有反向充电电路如果需要反向充电电路,可以插入一个 P-ch FET 来代替 R45,其栅极以 LD 引脚为基准,如图 8-21 所示。当 DSG 上升时,FET 将导通,当 DSG 下降到 LD 时,FET 将导通,且 R40 将帮助排出放电 FET 栅极电容,但 R40 将关断,从而使栅极下拉电阻器 R41 完全关断。在图 8-22 和图 8-23 中,R40 为 1kΩ。随着 DSG 关断,P-ch FET Q32 关断,反向充电电压将使 Dgate 网络下降,而 R40 中没有电流流动。导通时,R40 将与栅极电容一同工作,并且可以针对 Dgate 进行调整,以更好地接近 DSG 引脚。请记住,导通电流来自 CP1 电容器,DSG 的下降将取决于内部电阻和电荷从 CP1 电容器到 FET 栅极的转移。此示例使用 470nF CP1 电容器,可以观察到导通后的低电压。关断时,R40 与 R41 和肖特基路径并联,直到电压低到足以使 P-ch FET 关断为止。用户应注意,BQ769x2 不限制导通时 DSG 和 LD 之间的电压。P-ch 电路的目的是允许使用较小的 R40,以便 FET 栅极、PACK+ 和 LD 快速提供 DSG。如果使用的是大 R40 或者放电 FET 导通缓慢,则需要使用源极-栅极连接上的齐纳二极管以及从 Q32 栅极到 LD 连接的较大电阻器,以保护 Q32 栅极。

图 8-22 DSG 导通,12 个 FET,P-ch,1k 导通路径,470nF

图 8-22 DSG 导通,12 个 FET,P-ch,1k 导通路径,470nF 图 8-23 DSG 关断,12 个 FET,P-ch,1k 导通路径,100Ω

图 8-23 DSG 关断,12 个 FET,P-ch,1k 导通路径,100Ω图 8-24 中显示了使用单个 FET 和几 kΩ 的 R41 的短路示例。当施加短路时,BAT+ 和 PACK+ 由 FET 保持在一起,并由负载下拉。BAT 引脚的放电被 BAT 引脚电容器阻止,CP1 电容器将电荷泵电压保持在其之上,作为 CHG 和 DSG 输出的电源。在图 5-1 中,充电和放电 FET 的栅极由 D1 和 D2 保护。将 CHG 和 DSG 加载,并因存在器内电阻而略有下降,但电阻器两端的大部分电压下降到栅极:R44、R40 和 R45。DSG 的电压将随着对短路事件进行计时而下降。若采用更长的 SCD 延迟和更小的栅极电阻器,CHG 和 DSG 将下降,直到 D1 和 D2 停止传导。BQ769x2 使用 REG18 电源对事件进行计时。如前所述,当达到选定的延迟时,DSG 将关断。R41 关断放电 FET,并且必须选中 R41 ,以迅速关断 FET,从而避免过热,或缓慢关断 FET,以避免 BAT+ 过度上升。

图 8-24 短路示例

图 8-24 短路示例